芯片后仿之SDF 3.0解析(三)

描述

本文接着解析SDF3.0的Timing Checks Entries、Timing Environment Entries两个部分。

(一)SDF3.0 Timing Checks主要分以下两种:

VCS/NC-Verilog后仿真在timing violation时报出warning;

Timing Sign-Off工具报出timing check violations;

以时序分析工具Sign-Off为主,后仿为辅,SDF3.0 Timing Checks具体的类型如下:

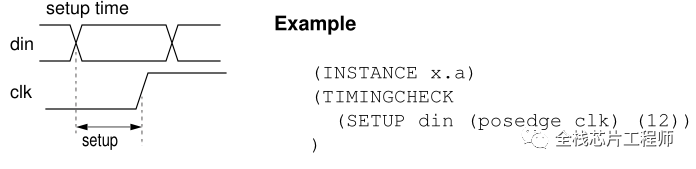

Setup Timing Check

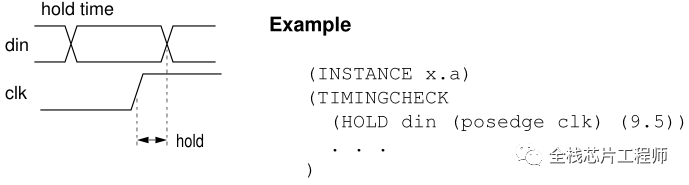

Hold Timing Check

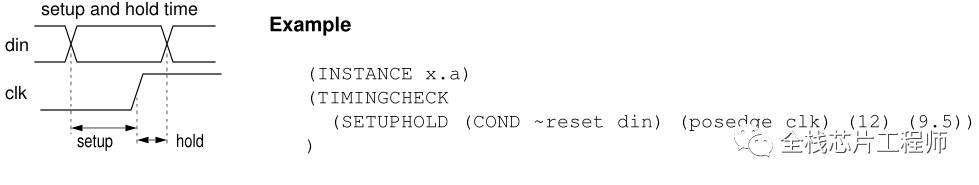

SetupHold Timing Check

注意,示例中~reset必须为真(Ture),timing check才会进行,此外,12是建立时间要求,9.5是保持时间要求。

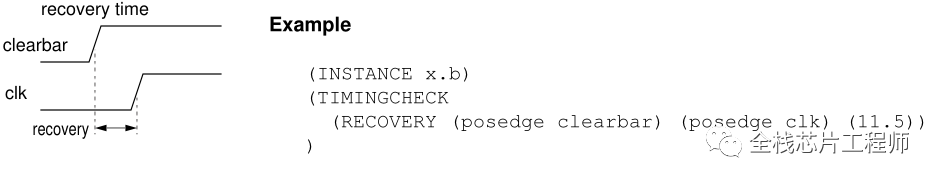

Recovery Timing Check

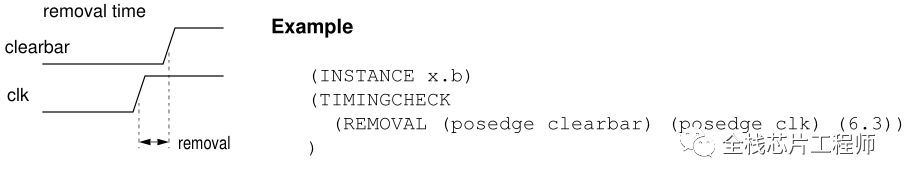

Removal Timing Check

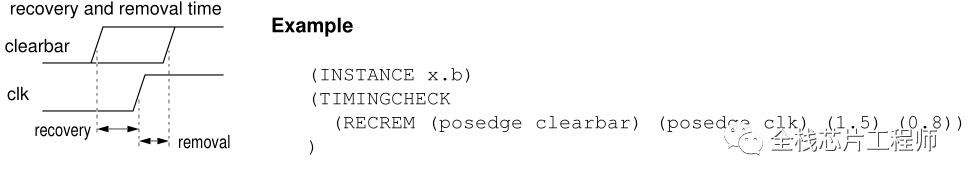

Recovery/Removal Timing Check

示例中,recovery time为1.5个time unit,removal time为0.8个time unit。

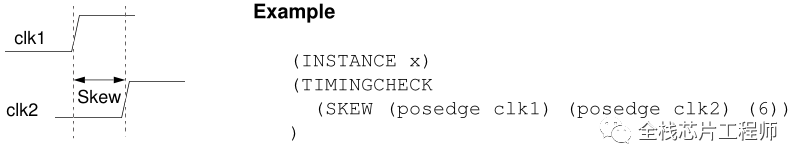

Skew Timing Check

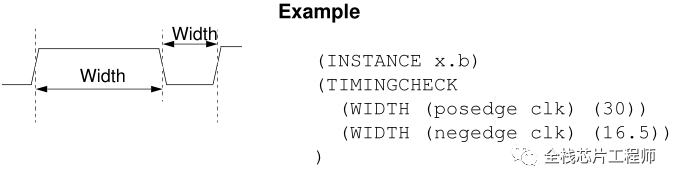

Width Timing Check

示例中,第一个minimum pulse width检查是posedge clock驱动的high phase;第二个minimum pulse width检查是negedge clock驱动的low phase;

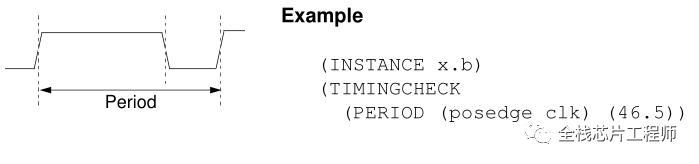

Period Timing Check

示例中,两个连续上升沿之间或两个连续下降沿之间的最小Cycle时间。

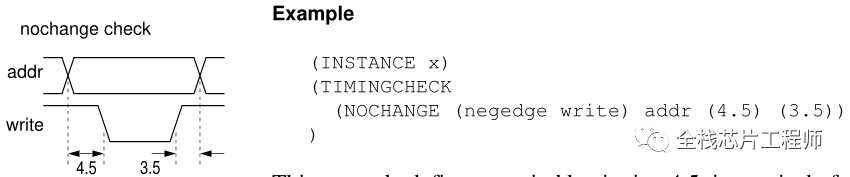

No Change Timing Check

示例中,addr提前write下降沿4.5个time unit, addr晚于write上升沿3.5个time unit。

(二)SDF3.0 Timing Environment Entries

SDF3.0 Timing Environment Entries分成Constraints与Timing Environment两个部分,首先解析Constraints。

1.Constraints

首先,SDF3.0 Timing Environment包括以下几类constraints:

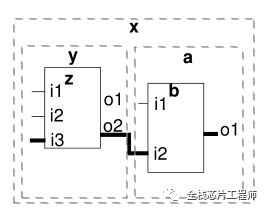

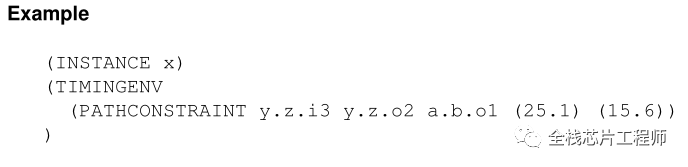

a)Path Constraint 针对timing analysis中发现的关键路径添加的约束,PR工具可以利用这些约束优化physical design,该约束指定路径的最大延时; 如下图, y.z.i3是path起点,a.b.o1是path终点,25.1是起点和终点之间的maximum rise delay,15.6是起点和终点之间的maximum fall delay。

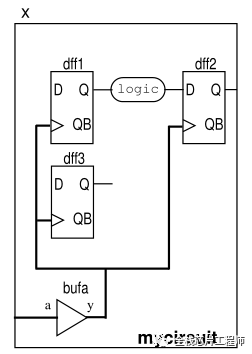

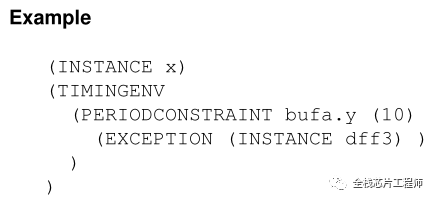

b)Period Constraint

时钟树上common clock到其驱动的leaf cell的路径的最大延迟约束。

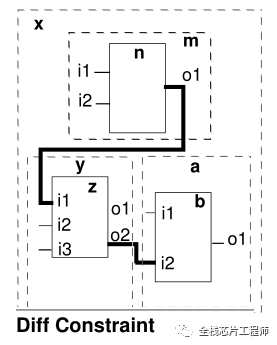

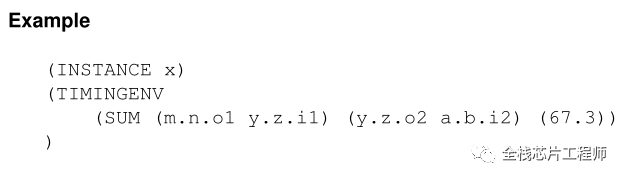

c)Sum Constraint

顾名思义,指的是几条路径的延时之和。示例中,约束两条net的延时之和小于67.3个time unit。

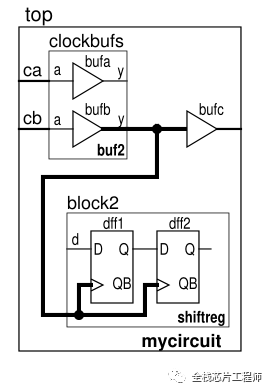

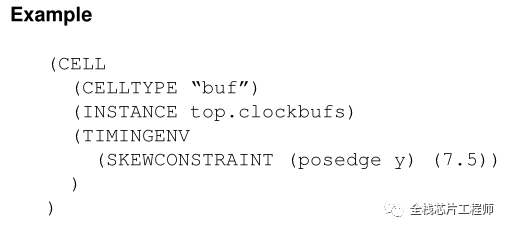

d)Skew Constraint

SDF3.0 Timing Environment Entries分成Constraints与Timing Environment两个部分,上文解析了Constraints,现在解析Timing Environment。Timing Environment包含以下4点约束

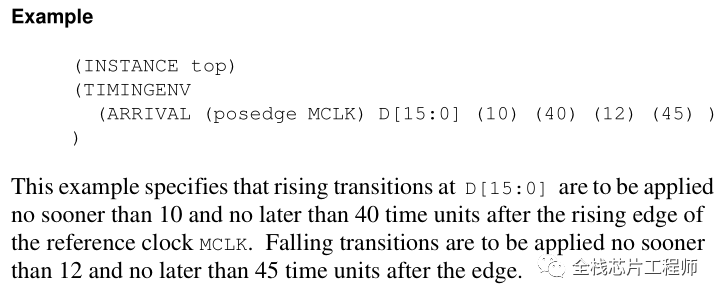

a)Arrival Time

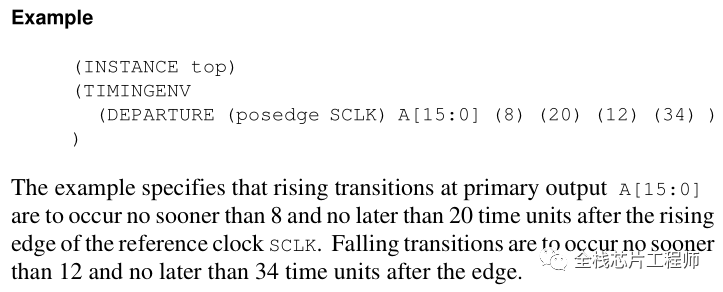

b)Departure Time

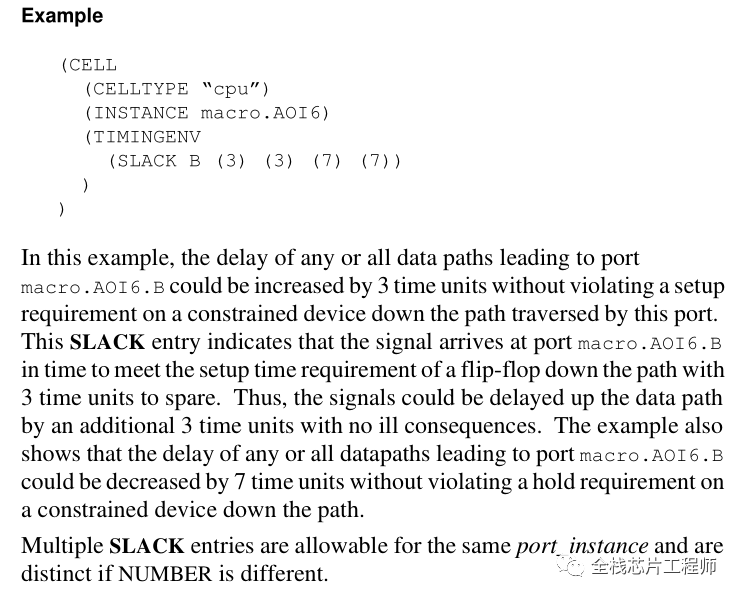

c)Slack Time

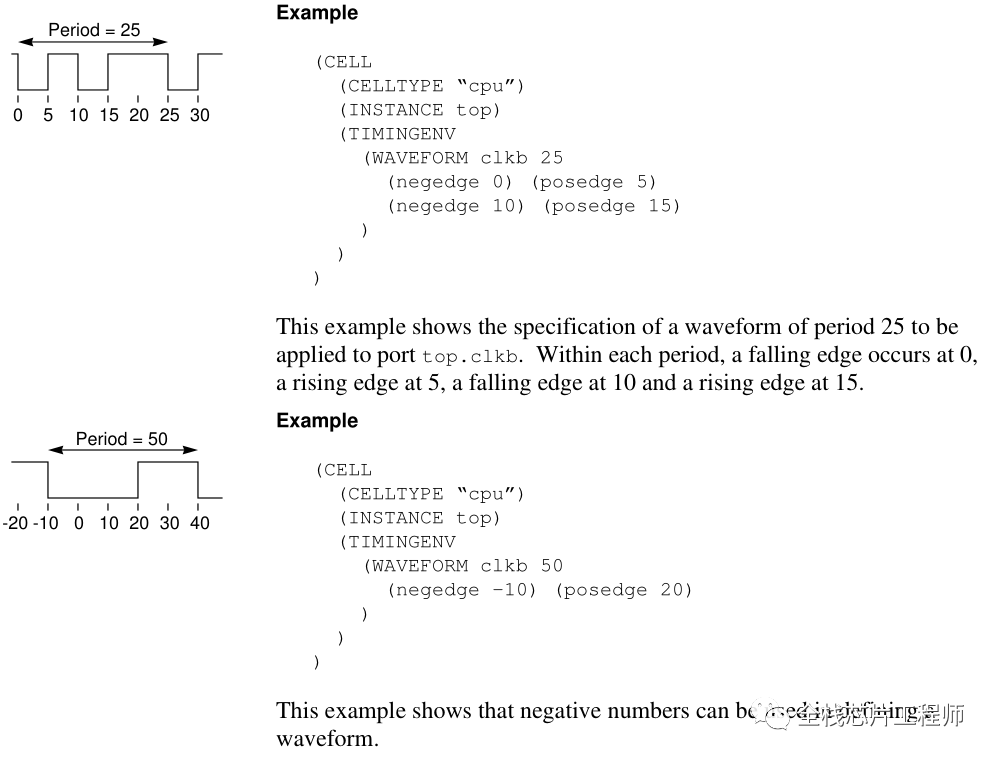

d)Waveform Specification

审核编辑:刘清

-

运行后实现时序仿真后重新生成sdf文件2018-11-07 5965

-

X_BUF在SDF中具有零延迟是为什么?2020-06-08 1872

-

如何将PT产生的SDF文件反标设计进行后仿真?2021-06-23 4163

-

SDF是什么?有何应用2021-09-02 1185

-

NodeMCU V3.0 Arduino开发之点灯测试程序2021-11-01 1551

-

ZigBee3.0数据包解析2022-02-28 3304

-

什么是数字后仿?浅谈芯片数字后仿的那些事2023-03-15 12443

-

解析SDF的Header Section信息与Cell Entries信息2023-05-06 3975

-

详解芯片SDF文件 MCU芯片全流程设计2023-05-08 14305

-

芯片后仿及SDF反标2023-06-08 6348

-

芯片后仿之SDF 3.0解析2023-12-18 3267

-

芯片后仿真要点2024-10-23 3546

全部0条评论

快来发表一下你的评论吧 !