利用ISE与Matlab创建并仿真FPGA设计中的ROM IP核

可编程逻辑

描述

今天给大侠带来FPGA设计中使用ISE和Matlab创建并仿真ROM IP核,话不多说,上货。

本想使用简单的中值滤波进行verilog相关算法的硬件实现,由于HDL设计软件不能直接处理图像,大部分过程都是可以将图像按照一定的顺序保存到TXT文档中,经过Modelsim仿真后,处理的数据再经过matlab显示图像;图像首先通过matlab或者C语言保存在TXT文档中,生成测试向量文件,然后在仿真软件中进行仿真处理,把处理后的数据保存为TXT格式,最后用matlab显示,观察结果。一般都是先创建MIF文件,将图像中的像素信息用一个ROM储存起来,然后调用ROM里面的地址进行处理,相当于制作了一个ROM查找表。

图像保存的步骤

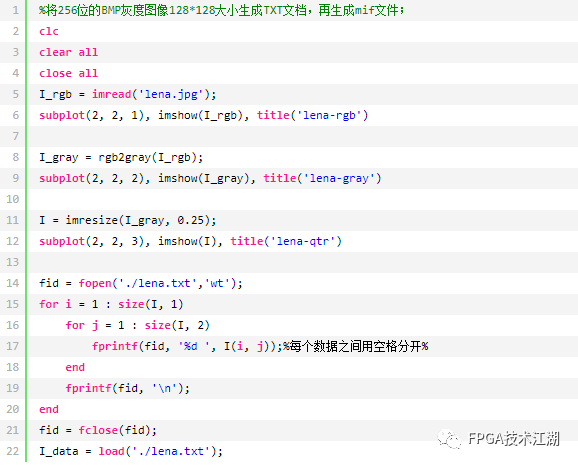

1.使用matlab将图像生成txt文。

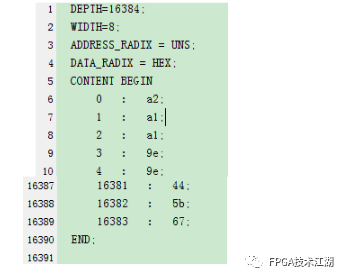

2.创建mif文件(Memory Initialization File):使用mif生成器、C语言或者matlab语言来生成;选择直接使用matlab生成mif文件gray_image.mif;

生成的mif文件如下图所示:

3.调用mif文件生成ROM(verilog文件即.v文件)

使用Xilinx ISE创建并仿真ROM的步骤:

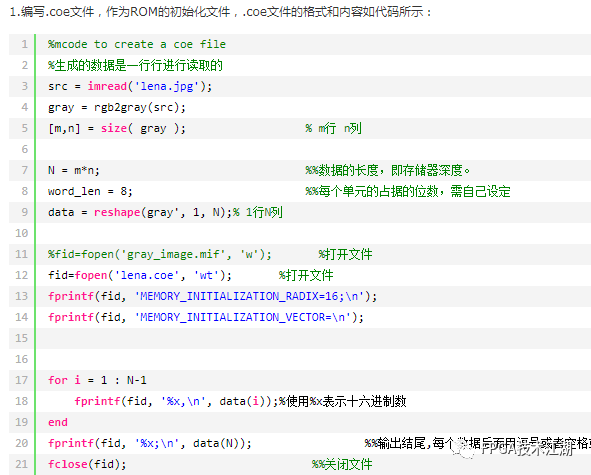

1.编写.coe文件,作为ROM的初始化文件,.coe文件的格式和内容如代码所示:

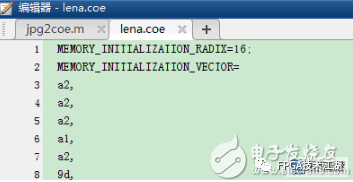

2.生成的.coe文件格式如下图所示:

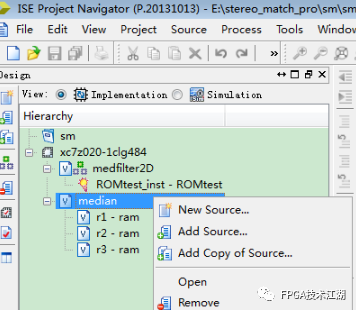

3.使用Xilinx中的Core Generator完成ROM的例化(生成的.coe文件的图像数据是一行行进行读取的)。打开ISE,右键单击New Source,如下图所示:

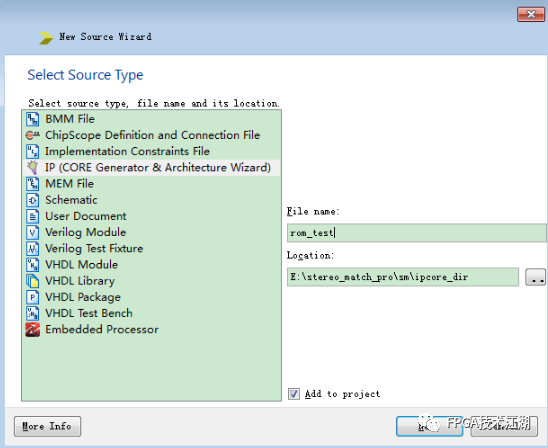

单击之后选择IP_Core_Generator,

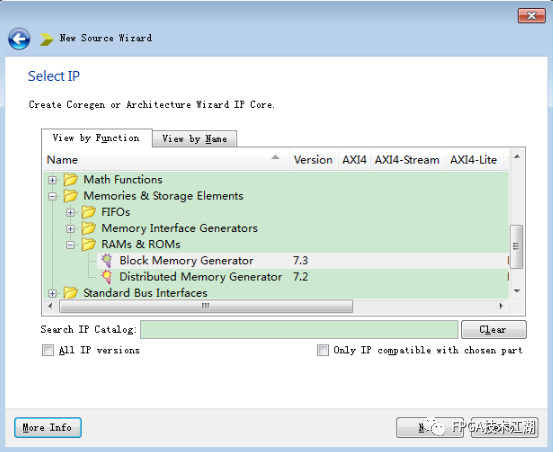

单击Next选项,选择Memories&Storage Elements->RAMs&ROMs->,选择块式存储或者分布式存储(这里根据存储数据的大小进行选择,较小的可以选择块式存储)。

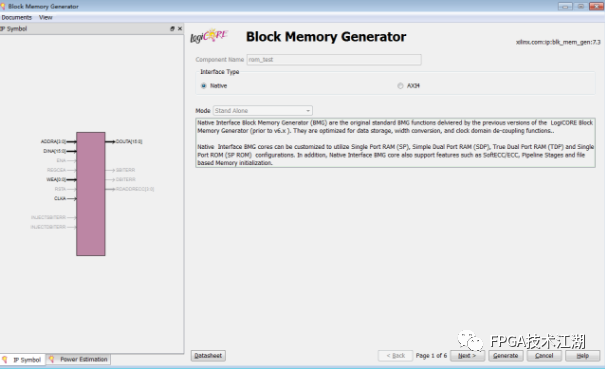

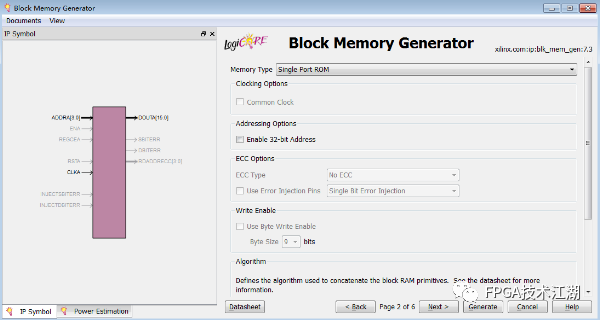

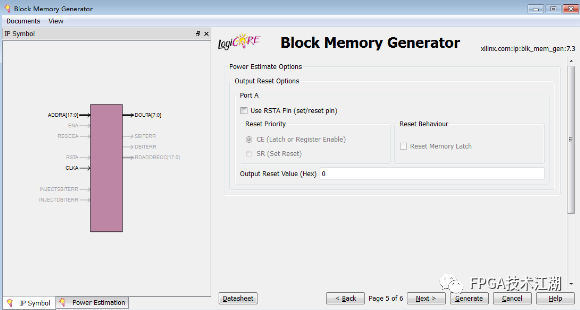

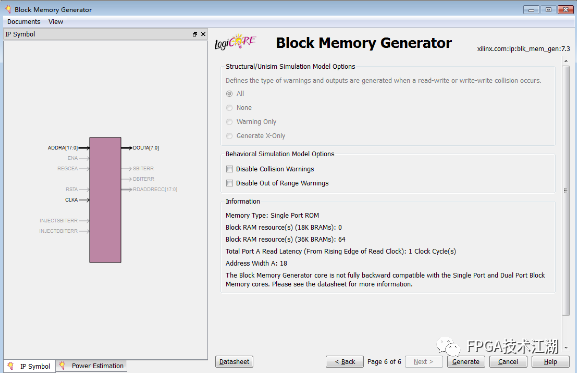

点击Next,然后Finish。然后就出现了下面的界面,一直点击Next进行ROM属性的一些设置,直至完成:

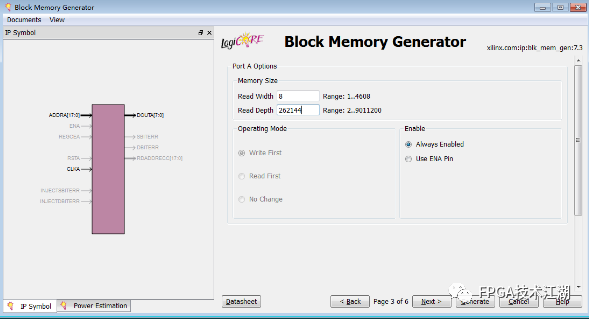

然后就要选择所需要的ROM的大小:

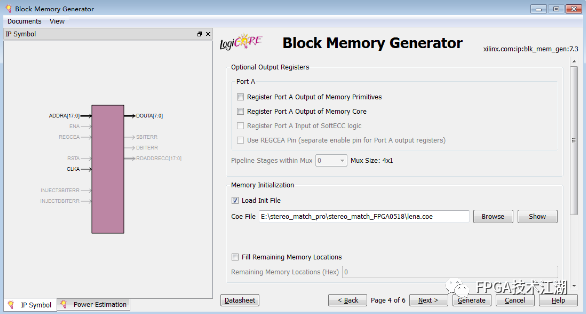

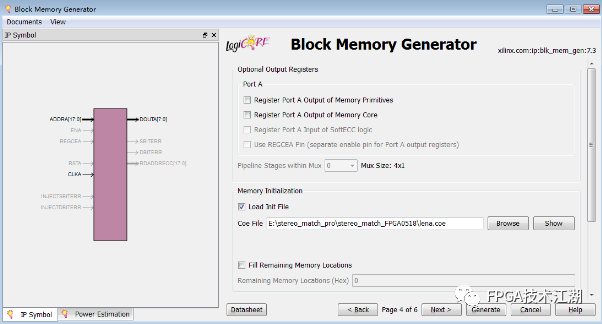

portA 表示输出要不要时钟打拍输出,这个是在mux里实现的; 在添加初始化文件的时候,将之前matlab生成的.coe文件添加到ROM IP核中去。

一直next下去,就可以得到初始化好的ROM IP核,可以在./ipcore_dir目录下查看ROM文件,从而可以在顶层模块中对ROM进行例化。

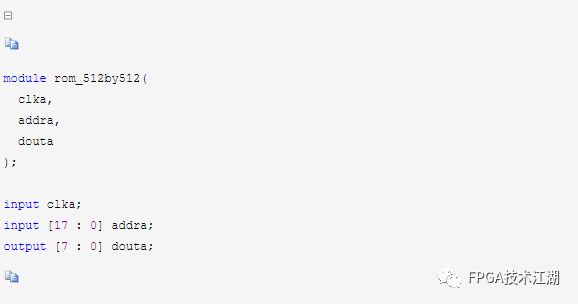

生成的ROM文件的输入输出变量如下:

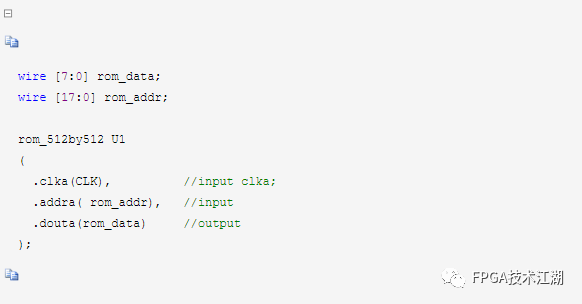

在顶层模块中对ROM进行例化如下:

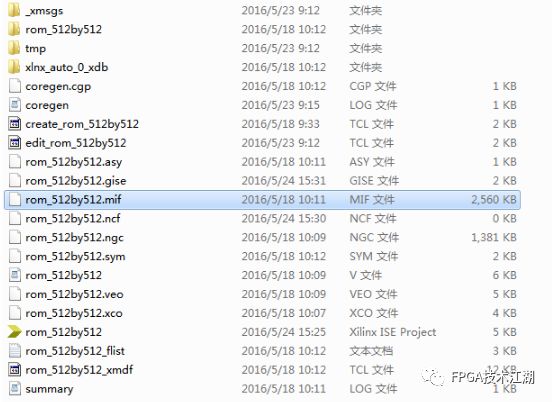

4.使用CoreGenerator完成ROM的例化后会生成一个.mif文件,这是Modelsim进行ROM仿真时需要的初始化文件,将.mif文件复制到Modelsim工程下进行仿真。

5.查看ROM模块中的初始化数据,双击Rom模块,出现如下图的界面,点击show按钮,即可查看数据;

审核编辑:黄飞

-

FPGA的IP软核使用技巧2024-05-27 3389

-

FPGA IP核的相关问题2013-01-10 3038

-

关于ip核生成的rom2013-05-14 3854

-

ise中的iP核2013-10-08 2503

-

modelsim 仿真 altera IP核(ROM,RAM实例2015-11-19 6119

-

Xilinx FPGA入门连载43:FPGA片内ROM实例之功能概述2016-01-06 4847

-

【锆石A4 FPGA试用体验】IP核之ROM(二)创建ROM IP核2016-09-25 4363

-

基于FPGA的FFT和IFFT IP核应用实例2019-08-10 6165

-

如何使用FPGA内部的ROM以及程序对该ROM的数据读操作2021-01-07 2573

-

FPGA设计中,使用ISE和Matlab创建并仿真ROM IP核2021-09-22 2883

-

IP CORE 之 ROM 设计- ISE 操作工具2023-04-07 1045

-

FPGA中IP核的生成2015-11-30 955

-

FPGA学习:使用matlab和ISE 创建并仿真ROM IP核2018-10-25 4756

-

测试与验证复杂的FPGA设计(2)——如何在虹科的IP核中执行面向全局的仿真2022-06-15 1783

-

FPGA学习笔记:ROM IP核的使用方法2023-08-22 7937

全部0条评论

快来发表一下你的评论吧 !