3D DRAM进入量产倒计时,3D DRAM开发路线图

存储技术

描述

在AI服务器中,内存带宽问题越来越凸出,已经明显阻碍了系统计算效率的提升。眼下,HBM内存很火,它相对于传统DRAM,数据传输速度有了明显提升,但是,随着AI应用需求的发展,HBM的带宽也有限制,而理论上的存算一体可以彻底解决“存储墙”问题,但该技术产品的成熟和量产还遥遥无期。在这样的情况下,3D DRAM成为了一个HBM之后的不错选择。

目前,各大内存芯片厂商,以及全球知名半导体科研机构都在进行3D DRAM的研发工作,并且取得了不错的进展,距离成熟产品量产不远了。

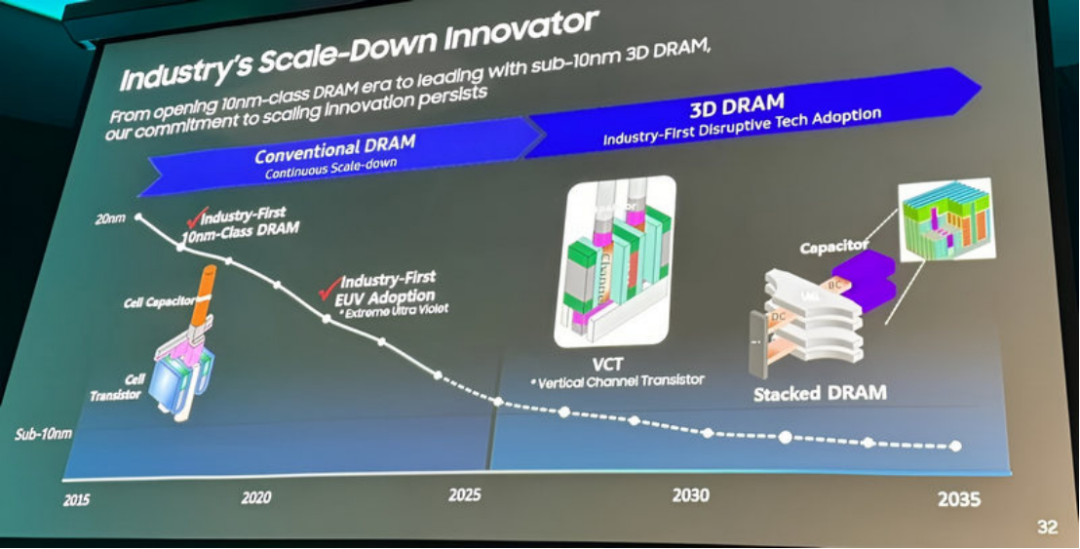

据首尔半导体行业消息人士透露,3月,三星电子在加利福尼亚州圣何塞举行的全球芯片制造商峰会Memcon 2024上公布了其3D DRAM开发路线图。

4月初,从三星电子传来消息,该公司计划在2025年推出基于其垂直通道晶体管技术的早期版本的3D DRAM,该技术在构成单元的晶体管中垂直设置一个通道,并用一个栅极包裹住它作为开关。该公司还计划在 2030 年推出更新版本的堆叠式 DRAM,该DRAM可以堆叠包括电容器在内的所有单元。

01、3D DRAM的优势何在?

AI应用对内存性能(速度和存储密度等)的要求不断提升。然而,在大幅度增长的数据量,以及处理器快速提升的算力面前,传统的平面架构(2D)DRAM在存储密度和速度方面越来越吃力,与此同时,目前的DRAM制程工艺已经接近极限(最先进的DRAM制程约为12nm),进一步提升越来越难,这是由DRAM的结构导致的,它的基本存储单元是基于一个晶体管和一个电容器,目前的DRAM制程工艺扩展是在一个平面上进行的,工艺提升主要面临两个挑战:一、电容器的缩放;二、电容到数字线的电荷共享,要考虑用多少时间将电荷转移到数字线上、数字线有多长。存储电容的深宽比会随着制程工艺微缩而呈倍数增加,这就是平面DRAM工艺微缩越来越难的原因。

也就是说,传统DRAM架构是平面型的,而在一个平面内加入更多存储单元越来越困难。因此,类似于3D NAND,人们开始考虑将立体的3D架构带入DRAM。3D DRAM将存储单元堆叠在逻辑单元上方,以实现在单位面积上产出更多存储容量,3D DRAM可以有效解决平面DRAM存储电容高深宽比这一难题。此外,使用3D堆叠技术还能重复使用存储电容,从而降低DRAM的单位成本。

由于3D DRAM中的晶体管堆叠为多层结构,这种结构可以扩大晶体管之间的间隙,从而减少电流泄漏。

总之,3D DRAM芯片是垂直堆叠存储单元,而不是像传统DRAM那样水平放置所有单元,它将单位面积的容量增加了3倍(3D DRAM的基本容量为100GB,而当前DRAM的最大容量为36GB)。

就发展路线来看,据semiengineering报道,3D DRAM有两条路,其中,最直接的方法是保留当前的DRAM 技术,并将多个芯片堆叠在彼此之上。这是用于HBM的高级封装方法,常见的HBM芯片为4和8高,预计很快会达到16高。与传统DRAM相比,这是一种更昂贵的方案,因为在封装中堆叠die需要更先进的工艺,但对于需要大量高带宽内存的应用(如AI)来说,这是值得的。

另外一条路,也是多数厂商追求的最终目标,那就是单片堆叠。这种方案只需少量额外步骤,但是,这些步骤会导致很多困难。为了实现这个目标,有分析人士认为3D DRAM 可以效仿3D NAND Flash,将存储单元翻转。因为DRAM 单元具有较小的2D区域,但具有较大的垂直方向电容器,使其很高且难以分层堆叠。而且,随着 2D 尺寸越来越小,电容器越来越薄,它必须加长以保持足够的电荷。

这就延申出了另外一个问题,那就是电容器问题。

在传统DRAM的制造过程中,几乎都是采用电路和存储器堆叠在同一平面的方法来生产的,芯片制造商通过减小单元尺寸或间距来提高 DRAM 的性能。然而,他们达到了在有限空间内增加存储单元数量的物理极限,这里有一个问题,如果电容器变得越来越薄,整个器件可能会崩溃。如果无法解决电容器问题,DRAM的存储密度和数据传输带宽就难以实现跨越式提升。因此,业界提出了无电容DRAM方案,再加上3D堆叠技术,有望实现3D DRAM的突破。

所谓无电容DRAM,就是在其存储单元中,仅用一个晶体管来存储信息,且使用具有不对称双栅极结构的多晶金属氧化物硅半导体FET,通过floating body效应来存储电荷(不需要外部电容器)。

目前,全球多家知名半导体科研机构都在进行无电容3D DRAM 的研究工作,具体技术包括Dynamic Flash Memory、VLT、Z-RAM和IGZO-FET等。不过,从目前的发展情况来看,包括存储芯片三巨头(三星电子、SK海力士和美光)在内的厂商还没有披露更多关于无电容3D DRAM的细节。

02、各大厂商的研发进展

传统DRAM需要复杂的读写数据操作流程,而3D DRAM可以通过垂直堆叠的存储单元直接存取和写入数据,显著提高了存取速度。3D DRAM的优势不仅包括高容量和快速数据访问,还具有低功耗和高可靠性特点,可以满足各种应用需求。

有机构预测,到2030年,全球3D DRAM市场规模有望增长到1000亿美元。

正是看到了这样的发展前景,以存储芯片三巨头为代表的厂商都在发力,进行相关技术和产品的研发。

如前文所述,三星电子计划在2025年推出3D DRAM的量产产品。在三巨头中,三星是对该技术最为关注的,投入也最大,3D DRAM可以帮助三星在未来的AI芯片市场占据优势地位。而就目前来看,在AI内存市场,特别是HBM产品,SK海力士占据着主导地位,占有全球90%的HBM市场份额。三星要想赶超SK海力士,在HBM阶段恐怕是难以实现了,只能寄希望于3D DRAM或其它更先进的技术方案。

尽管存储三巨头都在研究这项技术,但SK海力士和美光科技尚未公布任何3D DRAM发展路线图。

下面分别看一下这三大存储芯片厂商在3D DRAM方面的研发和进展情况。

三星电子想主导3D DRAM市场,一直在开发新技术。

自2019年以来,三星电子一直在进行3D DRAM的研究,并于同年10月宣布了业界首个12层3D-TSV(Through-Silicon Via)技术。

2021年,三星电子正式对外宣布其3D DRAM开发项目,当时,恰逢该公司在其DS部门内设立下一代工艺开发团队,作为一项关键技术,3D DRAM包含其中,三星半导体业务公司总裁兼首席技术官宋斋赫(Song Jaihyuk)领导该团队。

在2022年的SAFE论坛上,三星表示,准备通过逻辑堆叠芯片SAINT-D解决DRAM堆叠问题,该设计旨在将8个HBM3芯片集成在一起。

据消息人士称,2023年5月,三星电子在其半导体研究中心内组建了一个开发团队,大规模生产4F2结构DRAM。由于DRAM单元尺寸已达到极限,三星想将4F2应用于10nm级工艺或更先进制程的DRAM。如果三星的4F2 DRAM存储单元结构研究成功,在不改变制程的情况下,裸片面积可比现有6F2 DRAM存储单元减少约30%。

2023年10月,在“内存技术日”活动上,三星电子宣布计划在下一代10nm级制程DRAM中引入新的3D结构,而不是传统的2D结构。

2023年,在日本举行的“VLSI研讨会”上,三星电子发表了一篇包含3D DRAM研究成果的论文,并展示了3D DRAM芯片内部结构的图像。

据报道,三星电子在美国硅谷开设了一个新的研发实验室,主要进行3D DRAM研发。据悉,该实验室隶属于硅谷的Device Solutions America (DSA)部门,负责监督三星电子在美国的半导体生产,并专注于新一代DRAM产品的开发。

除了要在2025年量产,三星电子还要在2027~2028年将相关制程节点缩小到8nm~9nm,目前,最先进的DRAM制程约为12nm。

下面看一下SK海力士和美光。

虽然没有明确的发展路线图,但SK海力士在一些行业会议上介绍过该公司对3D DRAM的理解。据BusinessKorea报道,负责SK海力士未来技术研究所的副总裁Cha Seon-yong表示,2024年,SK海力士将会披露3D DRAM电气特性的相关细节,到时候,该公司将会明确3D DRAM的发展方向。

据外媒报道,SK海力士正在为将来的DRAM开发IGZO通道材料,它可以改善DRAM的刷新特性。据悉,IGZO薄膜晶体管凭借其适中的载流子迁移率、极低的漏电流以及基板尺寸的可扩展性,在显示面板行业长期得到应用。它可以成为未来 DRAM 可堆叠通道材料的候选方案。

美光在2019年就开始了3D DRAM的研究工作。据TechInsights统计,到2022年8月,美光获得了30多项3D DRAM专利,三星电子持有的专利数为15项,SK海力士持有约10项专利,可以看出,美光的3D DRAM相关专利数量是这两家韩国存储芯片巨头的2-3倍。

除了大厂,有些创业公司也在进行3D DRAM开发。

例如,美国公司NEO Semiconductor推出了一种名为3D X-DRAM的技术,旨在克服DRAM的容量限制。3D X-DRAM的单元阵列结构类似于3D NAND Flash,采用了FBC技术,它可以通过添加层掩模形成垂直结构,从而实现高良率、低成本和显著的密度提升。

据NEO介绍,3D X-DRAM 技术可以跨230层实现128Gb的密度,是当前DRAM密度的8倍。NEO提出了每10年容量增加8倍的目标,计划在2030~2035年实现1Tb的容量,比目前DRAM的容量增加64倍。

由于内存与处理器联系非常紧密,因此,3D DRAM技术的研究工作并未局限于存储芯片厂商,CPU等处理器大厂也很关注。

由于在Chiplet(小芯片)技术的商业化上取得了成功,AMD想在HPC用处理器(CPU和GPU)方面更进一步,一种设想是在不久的将来在计算Chiplet上堆叠DRAM。在ISSCC 2023峰会上,AMD在其演示文稿中详细介绍了如何提高数据中心能效,其中,对用于服务器处理器和HPC加速器的多层堆叠DRAM的介绍十分引人注目,该公司预测这将是未来HPC用内存的一个发展方向。

近些年,华为在CPU、AI等HPC上投下重注,要想在这方面进入产业前沿,同样躲不开内存技术的改进问题。在VLSI Symposium 2022上,华为发表了一篇关于3D DRAM的论文,详细介绍了该公司采用的垂直CAA型IGZO FET技术,该研究项目可以推动IGZO晶体管在高密度DRAM领域的应用。

除了企业(特别是大型存储芯片和处理器厂商),全球多家知名半导体科研机构,包括中国知名的科研院所,也都在进行3D DRAM的研究工作,就不在此一一赘述了。

03、结语

目前,AI正在各行各业渗透,大到数据中心和云计算服务器,小到手机。在可预见的未来,没有AI能力的设备将很难在市场上竞争。而AI对处理器和内存提出的要求越来越高,眼下,在手机等小型计算系统中,传统LPDDR还可以满足应用需求,将来则很有可能被淘汰;而在大型计算系统当中,HBM冉冉升起,但用不了多少年,其存储密度和数据传输带宽也将难以保障应用升级。此时,3D DRAM是一个更好的方案。

从长远来看,汽车行业也有望使用3D DRAM,因为智能化的电动汽车和自动驾驶技术需要能够实时处理从道路上收集的大量数据,此时,如果只有处理器性能提升,而DRAM不能满足要求,不会有好的效果和驾驶、乘坐体验,必须保证DRAM不存在存储密度和带宽短板,才能充分发挥汽车智能化和自动驾驶系统的性能。

因此,在多个应用市场不断发展的情况下,3D DRAM拥有广阔的增长空间。

审核编辑:黄飞

-

3D IC最快2014年可望正式量产2013-07-23 1267

-

为了延长DRAM存储器寿命 必须短时间内采用3D DRAM2017-03-17 3721

-

iTOF技术,多样化的3D视觉应用2025-09-05 192

-

3D NAND路线图#硬声创作季电子学习 2022-11-20

-

浩辰3D的「3D打印」你会用吗?3D打印教程2021-05-27 8046

-

3D XPoint的原理解析 NAND和DRAM为什么拼不过它2018-04-19 52224

-

关于3D超级DRAM技术简单剖析2018-10-28 5608

-

未来的3D NAND将如何发展?如何正确判断一款3D NAND的总体效率?2020-11-20 4278

-

如何看待3D DRAM技术?2023-05-31 1100

-

三星电子新设内存研发机构,专攻下一代3D DRAM技术研发2024-01-29 1099

-

三星电子在硅谷设立下一代3D DRAM研发实验室2024-01-31 1269

-

美国公布3D半导体路线图2024-03-25 1481

-

三星2025年后将首家进入3D DRAM内存时代2024-04-01 1200

-

三星已成功开发16层3D DRAM芯片2024-05-29 1376

-

SK海力士5层堆叠3D DRAM制造良率已达56.1%2024-06-27 1455

全部0条评论

快来发表一下你的评论吧 !