基于FPGA的多通道高速信号采集与处理平台设计方案

可编程逻辑

描述

概述 高速信号采集处理广泛应用于各个领域,随着科学技术的飞速发展,对信号采集处理装置的性能要求也越来越高。在该领域,我国的研究与产业化均起步较晚,大多数国内厂商的设备依赖进口,价格昂贵,功能灵活性不足。 本团队针对现有信号采集处理装置采样通道数少、动态接收范围小、灵活性针对性差等不足,提出了更加优化、更为全面的包括采集预处理(完成模拟域的放大、滤波、传入模拟-数字转换模块)、处理(基于FPGA的数字域信号处理算法)和传输(包括万兆以太网SFP+和PCIe 2.0 ×8传输接口)三大模块为一体的一整套解决方案。

主要创新点 1、各项参数指标较现有技术显著提升 高速信号采集处理广泛应用于各个领域,随着科学技术的飞速发展,对信号的采集处理装置也提出了越来越高的要求。 在用作数字接收机的场景下,在传统的模拟接收机中,模拟正交混频器难以做到严格的90°相位差,且I/Q两路放大器滤波器几乎不可能做到完全相同。 [1]专用DDC芯片,具有增益动态调节范围小、带外抑制差、处理精度低的缺点以及在面对不同应用需求,灵活度低针对性差。 [2]现有的一些高速采样卡应用场景受限,必须配合一整套设备使用,且有采样通道数少、采样速率低、灵活性针对性差等不足。

为此,本作品提供了更加优化、更为全面的包括采集、处理和传输三大模块为一体的一整套解决方案。具体技术指标如下: * 最大支持四通道同步采集; * 最大支持-10dB~+53dB,共128档程控增益控制,0.5dB步进; * 最高支持16bit模拟-数字转换精度; * 支持20M~125MSPS可调采样率; * 数据传输到PC端最高速率达32Gbps; * 板载8GbDDR3存储器 * 软硬件自主研发设计的全套完善系统 本作品以自主设计的数模结合印制电路板为基础,FPGA程序、C语言程序均为团队自行开发,不借助任何成品模块。硬件系统保证了信号完整性、电源完整性及电磁兼容性,工作稳定、性能良好。整个软件系统完整、成熟、稳定性好,且系统的测试、调试程序、接口也非常完善,方便用户使用。 3、兼具板卡模式和独立仪器模式 * 板卡模式下,可将多卡并行复用,实现高效扩展 * 板卡模式下,可将多块多通道高速信号采集处理卡插入机箱中的PCIe插槽,通过板间同步信号的连接,实现多卡并行工作,从而方便地成倍扩展通道数量。 * 独立仪器模式下,可远离接收端PC机,实现超远距离传输 * 与传统嵌入于机箱的信号处理板卡相比,本平台在兼具传统的板卡模式之余,设计了万兆以太网SFP+接口,可作为独立仪器,远离接收端PC机放置,实现超远距离高速传输。此外,由于其独立性强、体积小,为嵌入信号源端提供了可能。

本系统已申请国家发明专利、实用新型专利以及软件著作权。本系统已申请三项国家发明专利、三项实用新型专利和两项软件著作权。 三项已授权实用新型专利如下: * 《一种核磁共振信号采集处理装置》,201721626471.9 * 《一种多通道宽动态范围高速信号采集处理装置》,201822012511.1 *《基于FPGA的可变带宽的核磁共振信号实时处理系统》,201820448016.2 两项实审中发明专利如下: * 《一种核磁共振信号采集处理装置》,201711227275.9 * 《一种基于FPGA的磁共振信号实时处理方法》,201711233672.7 一项初审中发明专利如下: * 《一种多通道宽动态范围高速信号采集处理装置》,201811465362.2 两项软件著作权如下: * 《多通道磁共振信号数字下变频软件系统》,2018SR215409 * 《多通道高速信号采集处理软件系统》,2019SR0544832 系统架构

1. 系统设计指标与系统总体架构

1.1 系统设计指标

系统拟实现的总体主要技术指标如下: * 通道数:四通道; * 增益调节范围:-10dB~+53dB; * 增益调节步进:0.5dB,共128档程控增益控制; * 采样率:20M~125MSPS; * 采样精度:16bit; * 板载数据存储容量:8Gb; * 数据上传到PC端速率:32Gbps;

1.2 系统总体方案

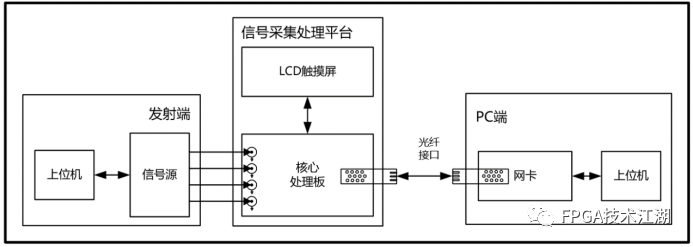

整套系统的架构如图2-1所示。以核心处理板为核心,由信号源产生的待处理模拟信号通过同轴线缆连接到核心处理板的信号接口,同时,连接同步时钟等其他相关信号到核心处理板。LCD显示屏通过FFC/FPC软排线连接到核心处理板的ARM处理器上。在核心处理板上完成处理后的数据通过光纤连接到PC端。

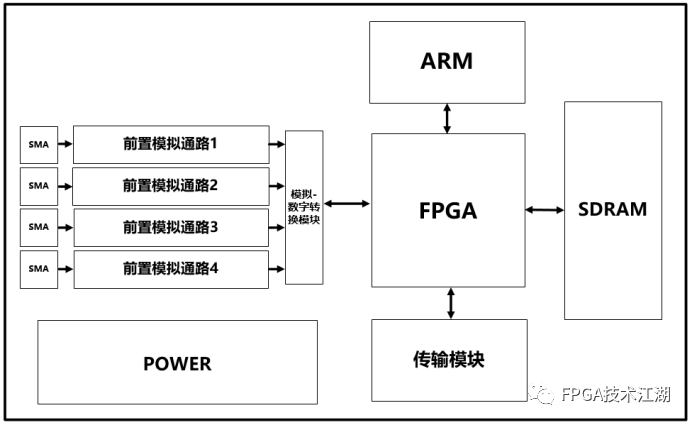

图2-1 系统总体实现架构方案 核心处理板总体架构方案如图2-2所示,主要包括以下部分:四路模拟信号采集模块、核心处理模块、数据片外存储模块、与PC机端的数据及控制信号交互模块以及电源模块。

图2-2 核心处理板总体架构方案 2. 指标论证与方案设计

2.1 模拟前端方案论述

为适应不同场景需求,本核心处理板上设计了可选的两套模拟前端放大方案,包括两路宽带(10 MHz~200MHz)放大和两路特定频点(63.5MHz)的放大。 以针对63.5MHz特定频点的放大为例,整条通路上包括两级压控增益放大器用于实现0.5dB的调节步进;一级用于抗混叠滤波的带通滤波器;一级固定增益放大器;一级用于进一步抑制由于放大器的非线性所产生的谐波的低通放大器。其中,VGA的增益可以通过FPGA实时调节。 四路经过放大/缩小的信号被传入模拟-数字转换芯片,本系统中所选用ADI公司的串行模数转换器AD9653。AD9653拥有4个通道,最高16bit精度,采样速率最高可达125 MSPS。

2.2 核心处理器方案论述

多通道高速信号采集处理平台需要支持对最多四路最高125Mbps的模拟信号的实时处理,需要支持高速(1Gbps)的 LVDS 接口。此外,由于要完成大量信号处理类算法,因此对DSP资源需求量也很大。而为了将处理完的数据及时发送到PC端,需要支持高速串行SERDES接口。整个处理过程庞杂,对时序要求严格,因此,需要核心处理器具备强大的处理能力及丰富的逻辑资源。 为满足上述要求,本系统采用Xilinx公司的Kintex-7系列FPGA,具体型号为XC7K325T-2FFG900C。该芯片拥有326,080个逻辑单元,16,020Kb的片上RAM存储资源,840个DSP48资源,最大时钟输入速率为933MHz,用户I/O口为500个,支持外部扩展SDR、DDR、DDR2 SDRAM和DDR3 SDRAM ,支持最高1,400Mbps的LVDS接收,GTX bank支持12.5Gbps的收发。 结合外设接口传输需求和FPGA代码的资源消耗量,综合评估,该芯片是在能够满足本系统的各项需求的前提下,具有较高性价比的选择。

2.3 数据缓存方案论述

本系统缓存方案的设计分为FPGA片上存储和板载存储器两部分。FPGA片上缓存的优点是访问迅速并且处理时延短,但是容量非常有限。板载存储器缓存的优点是容量大,但访问读写速度相对慢,且面临跨时钟域亚稳态等问题。 基于上述优缺点,对于存储资源的使用如下:面向PC机的传输利用板载DDR3 SDRAM,其他数据缓存利用FPGA片上存储资源。 其中,板载存储器DDR3 SDRAM选用4片镁光科技的 MT41K128M16JT-93K,为FPGA提供额外的8Gb的存储空间,使用1,600Mbps传输速率的设计方案。

2.4 万兆以太网接口方案论述

万兆以太网遵循IEEE802.3ae 标准,保留了与 10/100/1000M 三速以太网相同的数据帧格式,帧长度的界定,但在传输速率上具有显著提升,此外,该标准指明通过光纤介质进行信号的传播。 在网络接口的光模块选择上,SFP+相比于 XFP 体积小,适配 IEEE802.3ae协议并遵循SFF-8431 协议,其 PHY 和 MAC 层转换由FPGA处理器实现。因此本系统选择SFP+光模块作为网络硬件接口。

2.5 PCIe接口方案论述

为了能在需要时作为板卡模式使用,本核心处理板同时配备了PCIe2.0 ×8的传输方案,单通道带宽为500MB/s,采用8b/10b 编码方式,其总共的有效数据带宽为32Gbps。超出本系统所需基本需要,并留有余裕,便于以后功能扩展。 设计演示

1.电源测试

在确认电源网络和地网络之间不存在短路现象之后,即可上电对各路电源进行测试。在测试过程中主要关注输出电压值精度,及其与理论设计值之间的误差,以及纹波。各个电源电平和纹波测试结果如下表5-1所示。从表中可以看到,各电压均正确且电源纹波控制得比较好,是各负载芯片可以正常工作的重要前提。 表5-1 电源电平和纹波测试结果

| 电源名 | 设计电压(V) | 实际电压(V) | 误差 | 纹波峰峰值(mV) |

| 9V_A | 9 | 8.9433 | 0.63% | 20.50 |

| 5V_A | 5 | 4.9705 | 0.59% | 15.50 |

| 3P3V_D1 | 3.3 | 3.2817 | 0.55% | 13.20 |

| 3P3V_D2 | 3.3 | 3.2944 | 0.17% | 15.80 |

| 3P3V_D3 | 3.3 | 3.2797 | 0.62% | 16.50 |

| 2P5V_D | 2.5 | 2.4978 | 0.09% | 17.80 |

| 2V_D | 2 | 2.0063 | 0.32% | 12.50 |

| 1P8V_A | 1.8 | 1.7927 | 0.41% | 15.40 |

| 1P8V_D | 1.8 | 1.8039 | 0.22% | 13.40 |

| 1P5V_D | 1.5 | 1.4948 | 0.35% | 11.60 |

| 1P2V_D | 1.2 | 1.2015 | 0.13% | 20.80 |

| 1V_D1 | 1 | 1.0158 | 0.16% | 9.80 |

| 1V_D2 | 1 | 0.9960 | 0.40% | 13.6 |

| 0P75V_REF | 0.75 | 0.7443 | 0.76% | 8.0 |

| 0P75V_VTT | 0.75 | 0.7459 | 0.55% | 8.8 |

2.复位和时钟模块

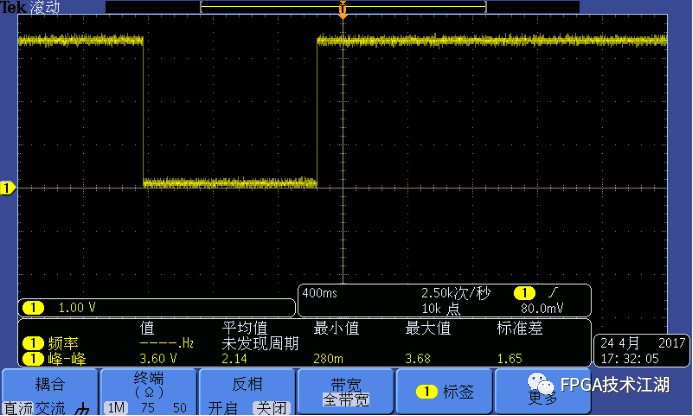

首先,测试复位信号。针对全局复位信号进行测试。可以看到复位信号输出的电平变化如图5-1所示,当用手按键时,全局复位信号置为低电平;当松开按键时,信号恢复成高电平。

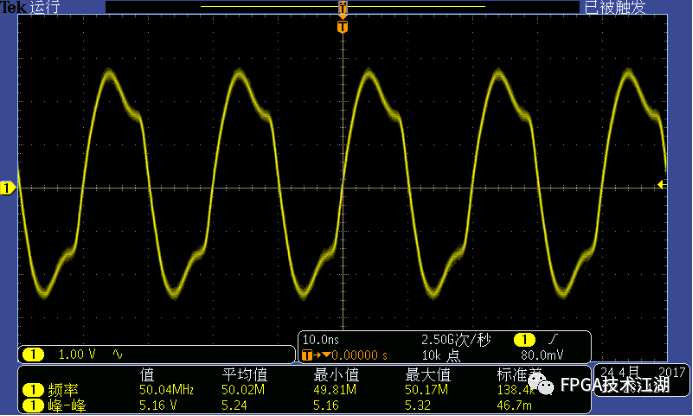

图5-1 复位信号测试 其次,测试时钟信号。板上时钟信号众多,包括有50MHz单端时钟,用于操作系统和外设的工作;200MHz差分时钟,用于逻辑触发时钟;156.25MHz差分时钟,用于万兆以太网的IP核输入时钟。以50MHz单端时钟的测量为例,如图5-2所示为测试结果。

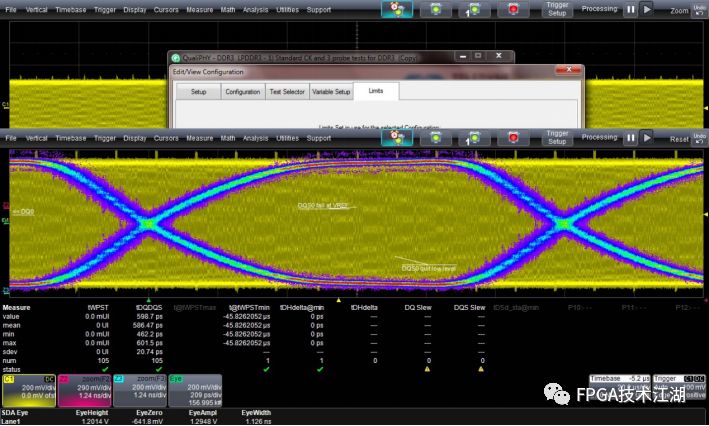

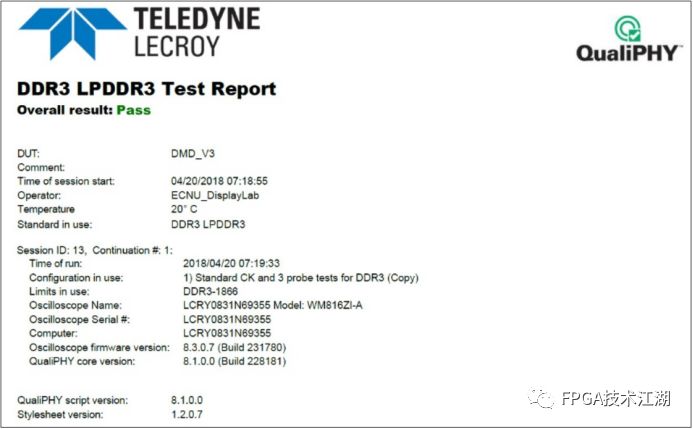

图5-2 时钟信号测试 3. DDR3信号测试 测试FPGA外部缓存DDR3的信号完整性。DDR3的运行速率为1600Mbps,编写测试程序持续对DDR3进行读写。 利用示波器的三个差分探头分别测试CLKP/CLKN(黄色)、LDQS/LDQSN(粉红色)、DQ0/GND(蓝色),能看到如图5-3所示测试结果。 800MHz差分时钟眼图,如图5-4所示。可以由示波器读出该信号眼高为1.1366V,眼宽为578ps,眼交叉比为50.37%,差分时钟设计指标通过了LeCroy 示波器的QualiPHY对1600Mbps DDR3的标准测试,因此眼图各指标符合设计要求。生成的测试报告结果,如图5-5 所示。

图5-3 DDR3部分信号测试结果图

图5-4 DDR3差分时钟眼图测试结果图

图5-5 DDR3 物理层一致性测试报告

4. 万兆以太网数据链路测试

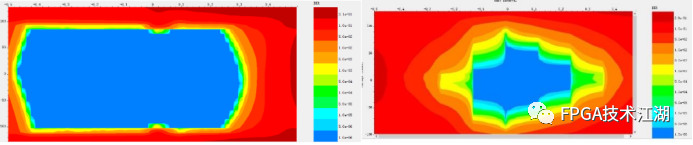

首先针对SFP+数据链路,利用Vivado软件中IBERT IP核对万兆以太网的速率进行测试。使用光纤将TX和RX端环回互连,测试编码使用PRBS-31。图5-6(I)是使用千兆光纤,可见眼图饱满,信号完整性好。图 5-6(II)是使用万兆光纤,测试协议类型选用10GBase-R,当数据速率是 10.3125Gbps 时测试收发数据链路,可见眼图受制于自身速率和板材的损耗角影响,虽然不如千兆时饱满,但测试结果误码率为0,能够满足需求。

(I) (II) 图5-6 SFP+数字眼图测试

5. PCIe数据链路测试

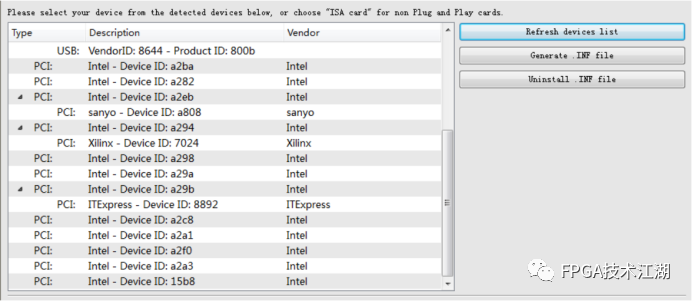

对于PCIe,如图 5-7所示,在主机中识别到EP设备。

图5-7 主机识别PCIe 设备 编写测试程序,由主机与核心处理板环回发送接收数据,然后统计数据的传输速率。如表5-2所示,PCIe的写存储器平均速率是1467.6MB/s;PCI的读存储器平均速率是1665.2MB/s该结果符合设计要求。 表5-2 PCIe性能测试

| 项目 | 1 | 2 | 3 | 4 | 5 |

| 写存储器 | 1475MB/s | 1472 MB/s | 1451 MB/s | 1434 MB/s | 1506 MB/s |

| 读存储器 | 1591MB/s | 1680 MB/s | 1687 MB/s | 1665 MB/s | 1703 MB/s |

6.系统功能测试

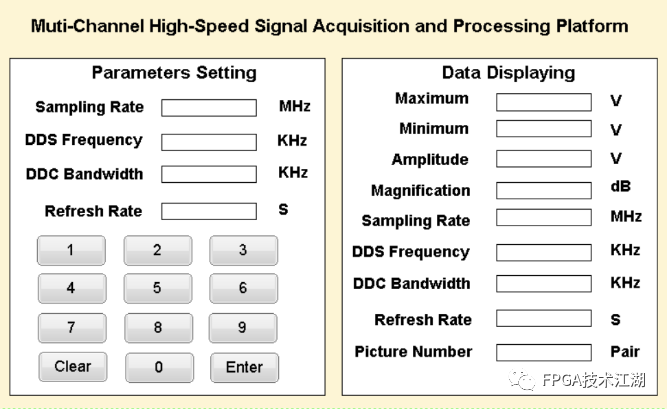

在完成对板上各模块及功能测试后,对系统进行级联测试。系统的实物连接如图5-8所示。 将用于信号产生的PC机的模拟信号输出接口,用同轴线缆连接到核心处理板的一路信号接口,同时,用同轴线缆连接同步时钟等其他相关信号到核心处理板。LCD显示屏通过FFC/FPC软排线连接到采集处理板上。在核心处理板上完成处理后的数据通过光纤连接到PC端。 连接好系统后,给核心处理板上电,负责收发的两台PC机开机。在如图5-9所示的LCD触摸液晶屏的界面上设置相关参数。

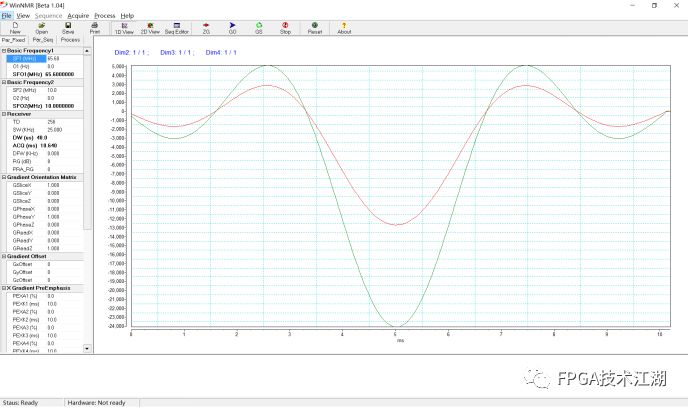

图5-9 LCD参数设置界面 将发送端的上位机打开,设置各项参数,发送模拟核磁共振信号。如图5-10所示。

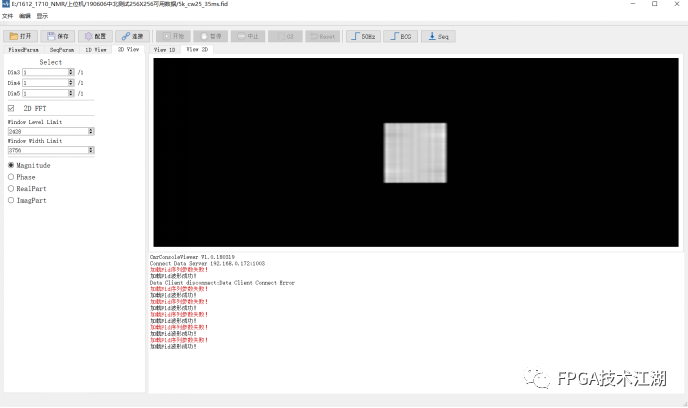

图5-10 发送端上位机界面 将接收端上位机打开,调入自动保存的文件,可以看到恢复出来的图像。如图5-11所示。

图5-11 接收端上位机界面

审核编辑:黄飞

-

jf_89520058

2024-12-16

0 回复 举报你好,这是什么设备啊,有的卖吗 收起回复

jf_89520058

2024-12-16

0 回复 举报你好,这是什么设备啊,有的卖吗 收起回复

-

基于FPGA的多普勒测振计信号采集与处理系统设计方案2013-10-29 3188

-

基于PCI总线的微弱信号采集模块的设计方案2014-01-24 4458

-

Pico示波器如何实现多通道同步采集2026-03-17 750

-

一种基于FPGA和DSP的高速数据采集设计方案介绍2019-07-05 2594

-

ARM和FPGA的嵌入式多通道超声波采集开发2020-09-07 1630

-

多通道信号采集记录 多通道采集存储 多通道记录存储介绍2021-08-11 1324

-

多通道信号采集与分析2008-08-06 981

-

基于FPGA 的交流信号采集与处理系统2009-05-16 754

-

基于FPGA的高速定点FFT算法的设计方案2010-02-09 1396

-

基于ARM/FPGA的高速多通道同步数据采集解决方案(恒颐)2012-11-27 1725

-

基于FPGA的多通道高速CMOS图像采集系统2016-08-30 692

-

高速中频采样信号处理平台的设计方案2017-10-30 936

-

如何使用ARM处理器和FPGA进行高速信号采集系统设计2018-11-02 1629

-

基于FPGA和高速ADC实现多通道通用信号处理平台的设计方案2020-07-16 3497

-

旋转环境下基于FPGA的多通道数据采集系统设计2023-08-08 2389

全部0条评论

快来发表一下你的评论吧 !