PMOS开关仿真电路分析

电源/新能源

3642人已加入

描述

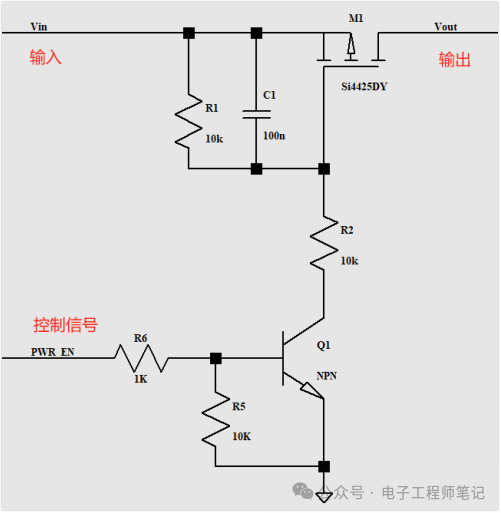

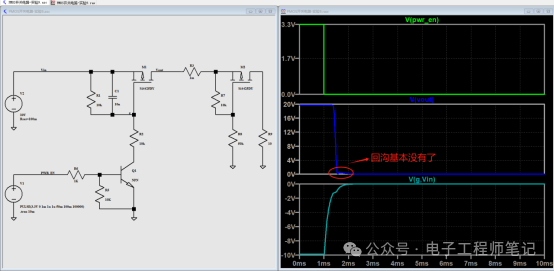

电路现象:PMOS断开后,输出端Vout电压先降低,后上升,再下降,随即下电波形出现回沟。(由以下电路展开)

以上为PMOS开关仿真电路,其将负载换成了一个开关电路,在改变负载以后,Vout的下电波形就不正常了,这是为什么呢?

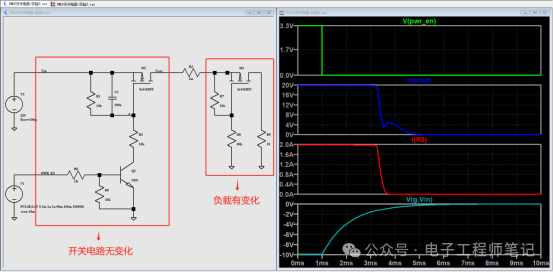

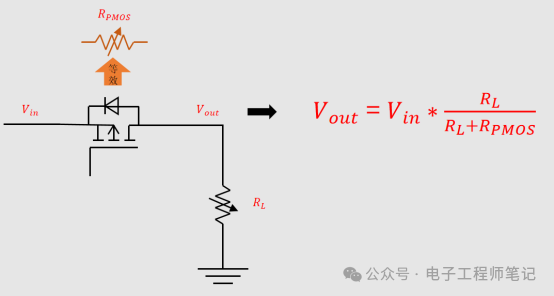

PMOS从导通到关断时,PMOS的阻抗会从接近0(导通),再到电阻无穷大(断开),这里会有一段过程,而PMOS会存在一定的阻值,负载也非恒定电阻。

在Vout下电过程中,负载获得的电压会下降到一定程度,随后可能会因为欠压突然停止工作,所需要的电流会急剧减小。

即其等效电阻突然变大,导致它获得的分压变大,这时就会出现以上的情况,Vout电压就涨上去了。也就是说,Vout的电压等于Vin在PMOS和负载上面的分压,如果负载RL突然变大,那么就有可能出现Vout突然上涨的情况。

因此,当PMOS从导通到关断切换期间,PMOS的Vgs电压等于其Vgsth,就出现了回沟。

那要如何解决这个问题呢?有两个选择。

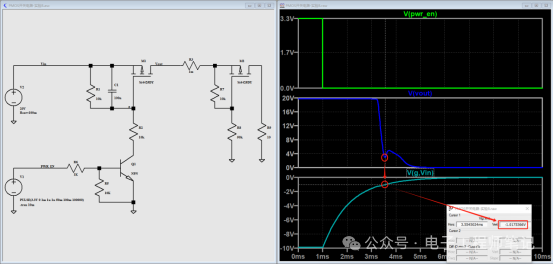

1、可以让PMOS更快的关闭,例如将PMOS的g和s跨接的电容从100nF调整到10nF,回沟就基本没有了。

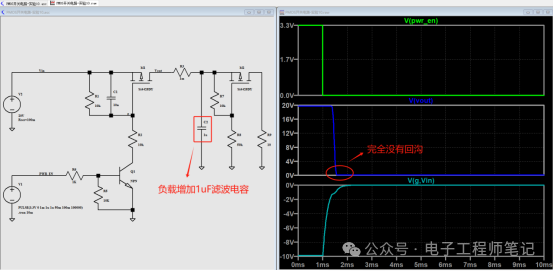

2.在输出端加一个滤波电容,避免负载等效RL突然变大。

这是因为增加一个滤波电容以后,等效负载会变成原本的RL和新增加电容阻抗的并联。尽管原本的RL突然变大,由于有电容阻抗的存在,负载阻抗就不会超过电容的阻抗。

PMOS关断的瞬间,过程是比较短暂的,信号可以当作交流,因此电容在这不可以看成是 开路,而是构成总的阻抗的一部分。

只要电容值合理,基本是可以解决电容回沟问题的。(如下图)

审核编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PMOS电路设计分析2025-07-21 3584

-

pmos开关电路连接方式有哪些2024-10-06 7857

-

NMOS与PMOS经典电源开关电路的深入解析2024-04-10 13314

-

PMOS作为高边开关,大电流关断时损坏的问题2024-02-05 7131

-

电源开关电路图讲解:NMOS、PMOS2023-08-14 11878

-

PMOS开关电路分析2023-03-10 12567

-

PMOS管开关电路分析2022-10-20 8685

-

一些PMOS做电源防倒灌及单向开关的电路2021-11-12 4616

-

NMOS管和PMOS管做开关控制电路2021-11-07 2718

-

PMOS按键电源开关电路2021-10-21 1755

-

开关电源的PSPICE仿真分析2021-09-18 1690

-

基于PMOS的高速开关电路求教2020-06-08 6590

-

负电保护电路,PMOS管开关关断问题2019-11-06 38081

全部0条评论

快来发表一下你的评论吧 !