多通道同步数据采集及压缩系统

数字信号采集

描述

1 引言

现代遥测系统中为了尽可能少地占用传输时间和存储空间,在有限的信道容量内传输更多的有用信息,采用数据压缩技术,有助于降低功率和带宽要求,改善通信效率。这里提出一种基于DSP与CPLD的多通道同步数据采集与压缩系统设计方案,该系统应用于遥测多路噪声数据,其中多通道同步数据采集可实现同时测量信号。并进行相关分析后,得到信号间的相关信息,而DSP内嵌的数据压缩算法实现其数据压缩的功能。

2 系统的硬件结构

2.1 系统设计思路

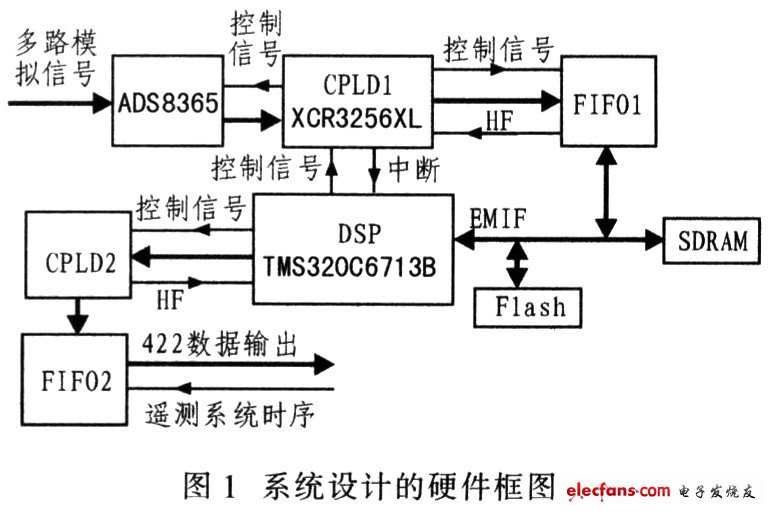

图1为系统设计的硬件框图。基于CPLD和DSP的多通道同步数据采集及压缩系统主要由数据采集模块、数据处理模块以及数据接口模块3部分构成。前端由传感器输人的模拟信号经信号调理模块的整形放大后,输入到 A/D转换模块中,模拟量转变为数字量,可编程逻辑器件(CPLD1)控制A/D转换器,按照设定的采样率采集数据,将采集到的数据通过总线写入 FIFO,FIFO半满时.发送一次半满信号,即DSP的中断,DSP接收到中断后立即将一帧数据从FIFO中读人到数据处理模块。DSP将其采集的数据高速压缩后写入到接口模块,再由可编程逻辑器件(CPLD2)通过RS-422总线将数据传送至遥测系统,做进一步分析。

2.2 器件选型

2.2.1 A/D转换器ADS8365

该系统的A/D转换模块选用TI公司的 ADS8365型A/D转换器,该件支持6通道信号差分输入,有3组信号采集控制端,每组控制2路信号,16位精度,每通道的转换速度高达250 kHz。支持高速并行数据输出接口,数据输出接口包括直接地址选择模式、CYCLE模式、FIFO模式。

2.2.2 复杂可变程逻辑器件(CPLD)XCR3256XL

采用CPLD控制各个接口,这里选用 XCR3256XL型CPLD,它是Xilinx公司的CoolRunner系列的高性能复杂可编程逻辑器件(CPLD)。该器件具有如下特点:采用 COMSEEPROM制造工艺技术;内置标准JTAG接口,支持3.3 V在系统可编程(ISP);3.3 V电源,集成密度为6 000个可用门;引脚间延时7.5 ns.系统频率高达140 MHz。同分离逻辑器件相比,单片CPLD实现逻辑控制功能,简化电路设计,提高系统可靠性。另外,XCR3256XL具有在系统可编程的功能,只需一根下载电缆连接至目标板上,可方便实现多次重复编程,大大方便电路调试。

2.2.3 数字信号处理器(DSP)TMS320C6713B

该系统设计的DSP选用TMS320C6713B,该器件TI公司推出的TMS320C67xx系列浮点DSP中的一款。它采用改进型哈佛结构,具有运算速度快、功耗小和性价比高等特点。其体系结构采用 Veloci TI超长指令字VLIW(Very Long Instruction Word)结构。每周期执行8条32位指令,支持32/64位数据。采用类RISC指令集,具有300 MHz、3.3 ns指令周期的运行速度和2 400 MI/s或1 800 MFLOPS的处理能力适用于高速信号处理。为了加快处理速度,DSP内核采用2级CACHE,其中L1级CACHE分为4 KB直接程序CACHE和4 KB数据CACHE(分为2路);L2级CACHE分为64 KB统一存储器和192 KB附加存储器。其内部有16通道EDMA控制器,能够高速处理几乎所有I/O和存储器的接口问题,大大提高器件吞吐速度。外部总的存储器地址空间最大 512MB,数据宽度为32 b,可支持SBRAM,SDRAM,SRAM,Flash和EPROM。TMS320C6713与外部I/O接口通过FFA构造的I/O端口、HPI口、多缓冲串口(McBSP)、SPI口等几种方式实现。与专用的硬件压缩器件相比,TMS320C6713B可方便实现数据压缩。以及系统升级和配置灵活。

3 CPLD部分设计

3.1 CPLD1控制部分

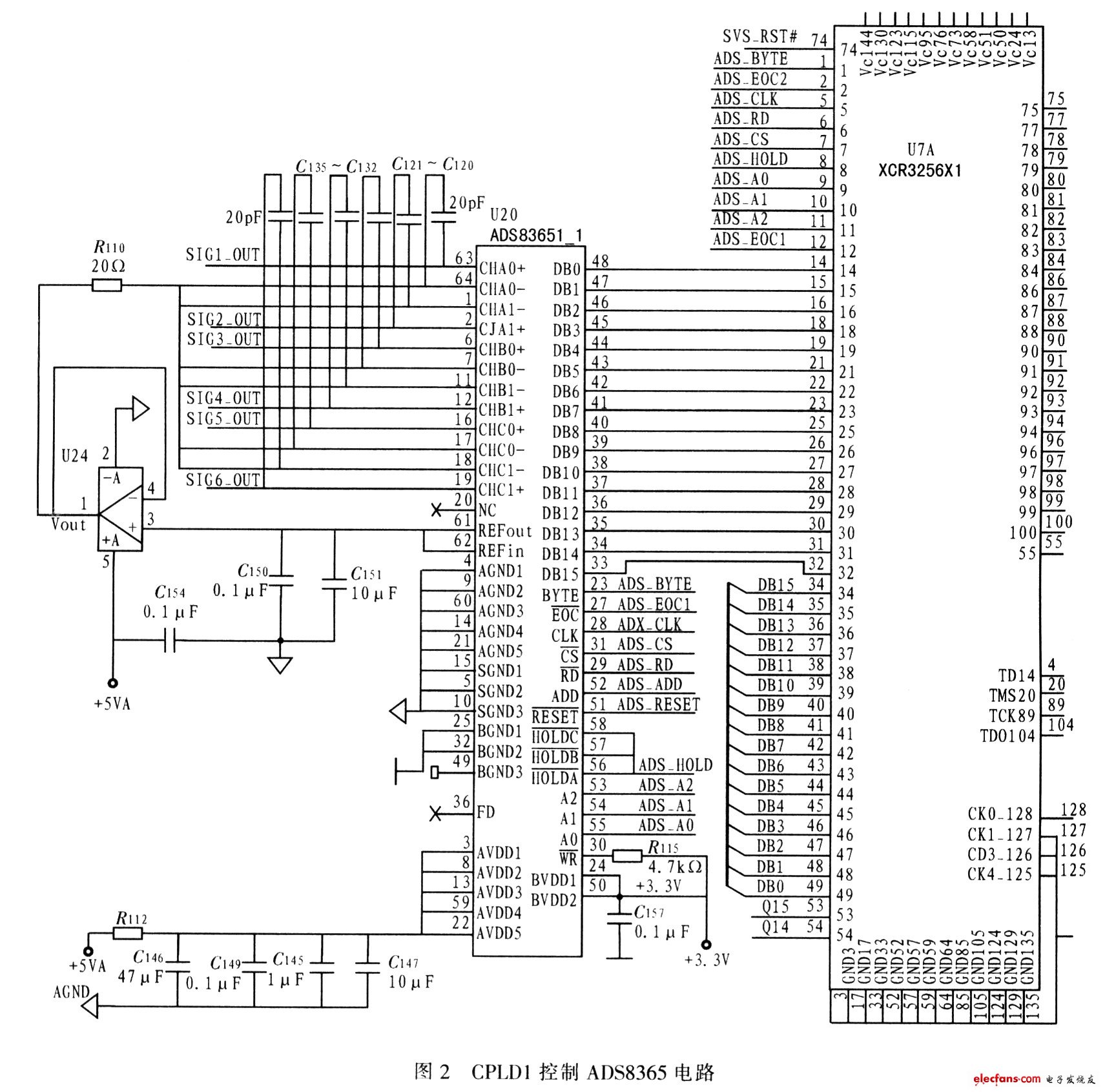

CPLD1控制ADS8365包括控制A/D转换器的采样率以及数据量化输出模式等,同时控制CS信号可有效抑制噪声;系统时钟输入为50 MHz,CPLD1对其分频产生5 MHz时钟以触发A/D转换器。程序通过控制A/D转换器的HOLDX来启动A/D转换;控制A/D转换器的ADD来控制其输出通道信息,控制A/D转换器的ADDRESS控制其数据输出工作模式。考虑DSP内程序算法每次判断通道信息会增加DSP运算负担,故设置A/D转换无通道信息,A/D转换器工作在CYCLE模式下,A/D转换后的数据按通道号顺序循环输出,DSP可根据顺序性直接判定数据的具体通道。图2为CPLD1控制ADS8365电路。

CPLD1控制DSP主要包括DSP复位设置,看门狗设置,DSP控制信号与CE空间组合逻辑控制读FIFO1等。

3.2 数据帧格式设置

CPLD1将A/D转换后的数据不断写入FIFO1,当2 048字节数据写入FIFO1后,CPLD添加16位的帧标志及16位的帧计数,即数据格式为:被采集数据+帧标志+帧计数。

3.3 CPLD2控制接口

接口转换模块的核心是CPLD,负责从输出FIFO2中读取数据,按照遥测系统的要求时序编码后。通过RS-422总线将压缩后的数据上传至遥测系统。

4 DSP部分设计

4.1 DSP程序设计流程

设备上电DSP复位后,由其内部固化的自引导程序(BOOT)将存于Flash存储器的程序和数据搬移至内部RAM中,然后DSP开始读取压缩算法的应用程序,继续运行。DSP的工作流程为:首先初始化DSP的CSL函数库,然后初始化PLL、GPIO及相关中断寄存器,等待中断。

采集模块16位数据通过总线不断写入。FIFO1中。程序通过控制其半满(HF)信号,即当数据超过半满时,HF信号低电平有效,将触发一次中断通知 DSP,DSP则进入中断后把2048字节的数据从输入FIFO1中读入到DSP所指向的SDRAM的空间中,DSP在处理完中断的空闲时间内进行高速压缩。将压缩数据与原数据相比较,若压缩数据小于原数据,就把压缩数据写入DSP的软FIFO中,否则,就将原数据写入DSP的软FIFO中。

最终,DSP把软FIFO中得压缩数据写入输出FIFO2中,等待发送模块将数据上传至遥测系统。

4.2 数据压缩算法选择

压缩编码信源信息在解压缩时能够完全恢复,也即在压缩和解压缩过程中信源信息无损失,该编码方法称为无损压缩,经常使用的无损压缩方法有Shannon-Fano编码,Huffman编码,游程(Run-length)编码,IZW (Lempel-Ziv-Welch)编码和算术编码(ARC)等。这里重点讨论ARC算法和LZW算法。ARC算法的思想就像查字典。众所周知.英文词典的编排方式是按首字母排序,首字母相同的词继续按第二字母排序,以此类推。实际应用算术编码更巧妙。利用字符出现的概率对0~1区间分割,然后用0~1 之间的一个小数对数据编码,原始数据越多,这个小数点后的位数就越多。

LZW编码是围绕称为词典的转换表完成的。该转换表用来存放称为前缀(Prefix)的字符序列,并且为每个表项分配一个码字(Code word),或称为序号,这张转换表实际上是把8位ASCII字符集进行扩充。增加的符号用来表示在文本或图像中出现的可变长度ASCII字符串。扩充后的代码可用9~12位甚至更多的位表示。12位有4 096个不同的12位代码,这就是说。转换表有4 096个表项,其中256个表项用于存放已定义的字符,剩下的3 840个表项用于存放前缀(Prefix)。LZW编码器(软件编码器或硬件编码器)通过管理该词典完成输入与输出之间的转换。LZW编码器的输入是字符流(Charstream),字符流是用8位ASCII字符组成的字符串,输出是用n位(例如12位)表示的码字流(Codestream),码字代表单个字符或多个字符组成的字符串。LZW编码器采用一种实用的分析(parsing)算法,称为贪婪分析算法(greedy parsingalgorithm)。

在贪婪分析算法中,每一次分析都要串行检查来自字符流(Charstream)的字符串,从中分解出已识别的最长字符串,也就是已在词典中出现的最长的前缀(Prefix)。用已知的前缀(Prefix)加上下一个输入字符C也就是当前字符(Currentcharacter)作为该前缀的扩展字符,形成新的扩展字符串——缀一符串(Sning):Prefix.C。这个新的缀一符串(String)是否要加到词典中,还要看词典中是否存有和它相同的缀一符串(String)。

如果有,那么这个缀一符串(String)就变成前缀(Prefix),继续输入新的字符,否则就把这个缀一符串字符(String)写到词典中生成一个新的前缀(Prefix),并给一个代码。

一般来说,不同的压缩算法有不同的优缺点。不同算法的复杂性对空间的要求以及压缩率也不同。这不仅依赖于压缩方法,也与被压缩数据的特点有关。

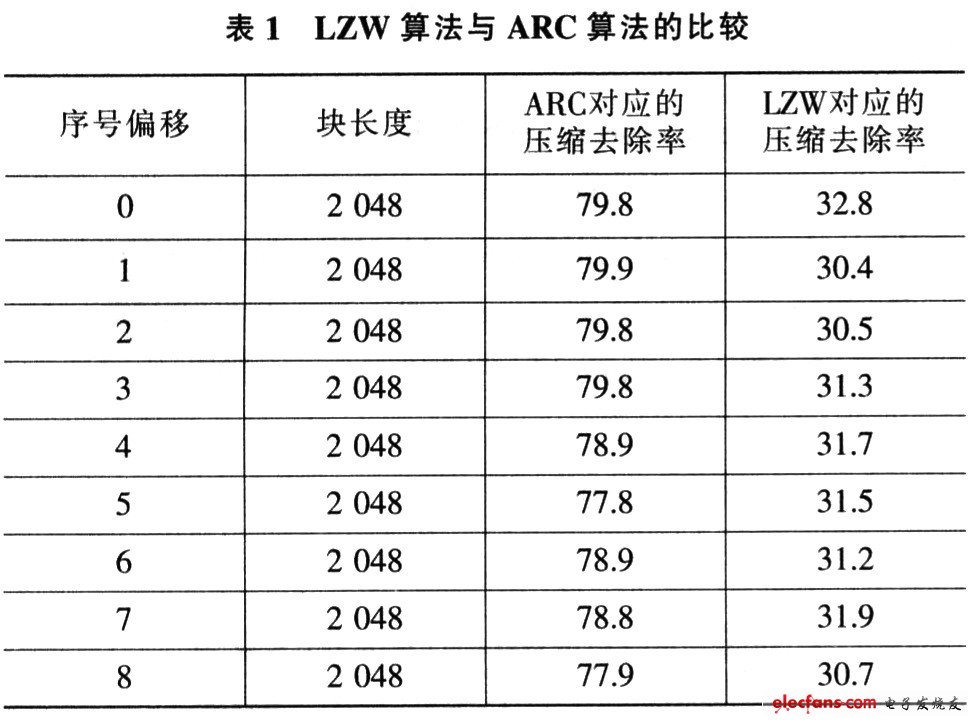

该系统设计是压缩实时数据,要求压缩过程的时间性能较高,故采用事先统计模型的ARC算法。实验证明,采用该算法其运算速度与LZW算法速度相近。而ARC算法在压缩去除率上优于LZW算法。

5 实验结果

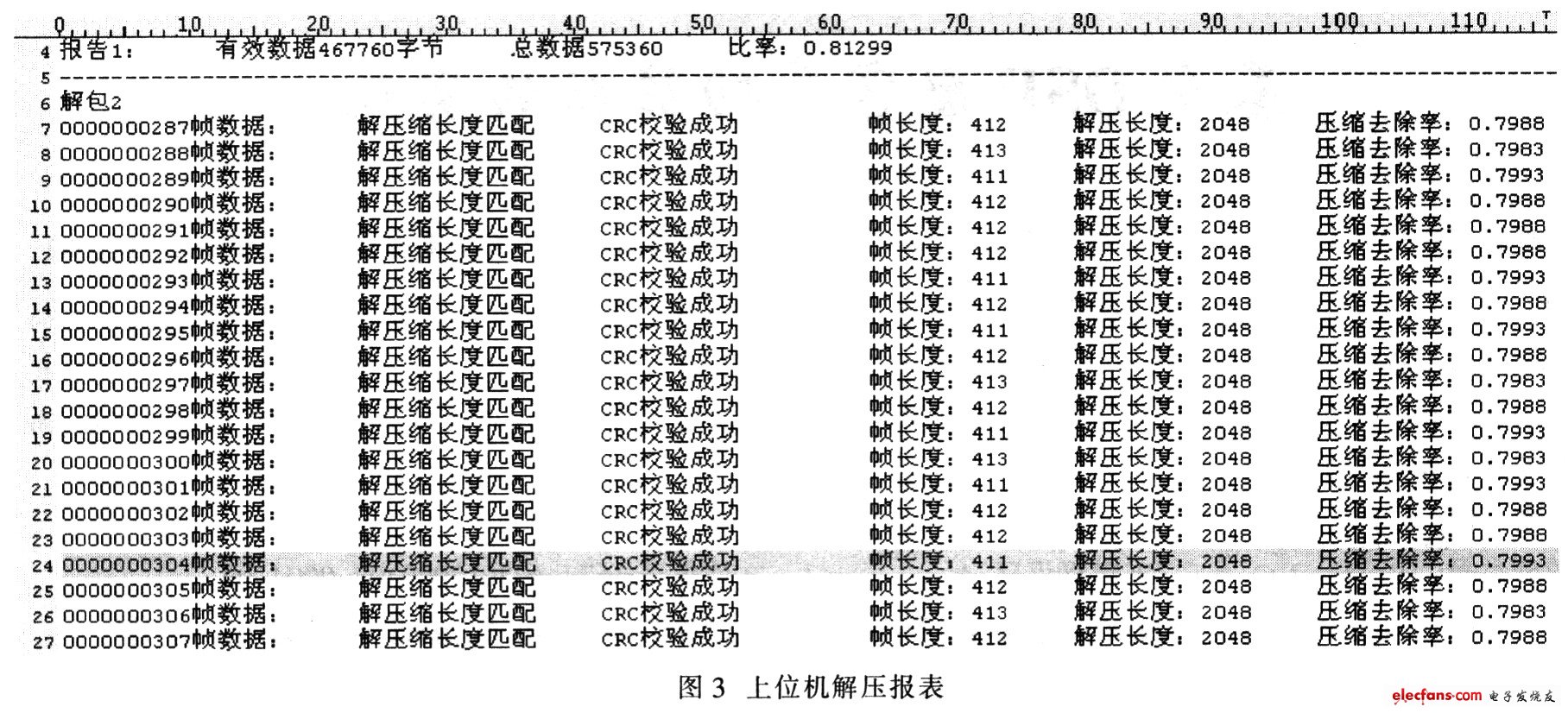

算法选择主要从压缩速度和压缩去除率进行比较。该设计中前端以27 kHz的速度实时采集某系统多路噪声压缩,从表1中可知ARC算法针对不同分组段的数据压缩去除率约为79%,而LZW算法,在该分组段压缩去除率仅约 31%,可见ARC压缩算法的压缩去除率比较高。实验中通过上位机发送一定规律数据,经过该系统压缩数据处理,压缩后数据再通过上位机解包、解压,还原的数据与原始数据相比对。其结果一致,证明系统安全可靠。图3为上位机解压报表。

6 结束语

详细介绍了系统组成,采用复杂可编程逻辑器件(CPLD)和数字信号处理器(DSP)的体系结构,对无损压缩的相关算法进行比较,最终采用算术编码 (ARC)作为系统压缩算法。本系统创新点在于采集模块的多通道同步性以及对噪声数据压缩的针对性。最后通过大量实验,证实本方案切实可行,各项指标满足系统要求。

-

Pico示波器如何实现多通道同步采集2026-03-17 776

-

多通道数据采集串扰问题怎么解决2024-07-02 4012

-

多通道数据采集系统的优缺点2024-07-01 3756

-

求一种多通道同步数据采集及压缩系统的设计方案2021-04-28 1639

-

多通道数据采集测试系统NSAT-4000在应用中具有哪些优势2020-10-29 2012

-

使用LabVIEW实现多通道数据采集系统的资料概述2020-07-24 2107

-

如何使用FPGA进行多通道同步数据采集系统的设计2018-12-18 1621

-

基于FPGA的多通道数据采集系统设计2016-05-10 1006

-

基于FPGA的多通道同步数据采集存储系统2010-12-27 1207

-

基于CVI的多通道数据采集系统2009-12-31 1232

-

基于PCI总线多通道数据采集系统的设计2009-10-22 1634

全部0条评论

快来发表一下你的评论吧 !