如何运用Retiming优化Block RAM的使用

描述

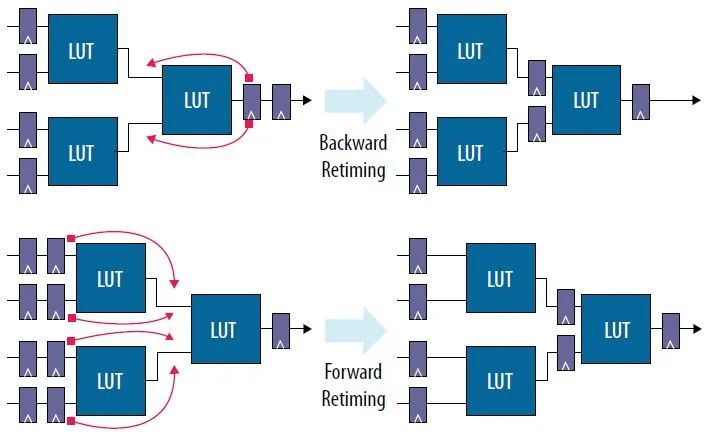

对于逻辑级数较大的路径,常用的时序收敛的方法之一就是采用Retiming(中文翻译为重定时)。Retiming到底是怎么回事呢?我们可以通过下图理解。图中通过搬移触发器的位置减小了关键路径的逻辑级数。无论是把触发器向前搬移还是向后搬移,搬移后整个路径的Latency和搬移前的Latency保持一致。可以看到Retiming的前提是相邻路径有可供搬移的触发器,换言之,相邻路径的时序裕量较为“富余”,从这些“富余”中拿出一部分给时序较为紧张的路径。这样,时序紧张的路径其逻辑级数降低了,而相邻的时序“富余”的路径逻辑级数增加了,达到整体逻辑级数的平衡。

Vivado提供了多种方法实现Retiming。在综合选项设置界面提供了-retiming,如下图所示。在这里,它是一个全局选项,作用于设计中的所有模块。除此之外,Vivado还提供了模块级综合技术,可针对关键模块使用Retiming,此时需要借助属性BLOCK_SYNTH.RETIMING实现。显然,这个综合属性是针对指定模块的,所以这是一种更精细的设置方法。实践证明往往全局选项-retiming加上模块级Retiming能获得更好的效果。

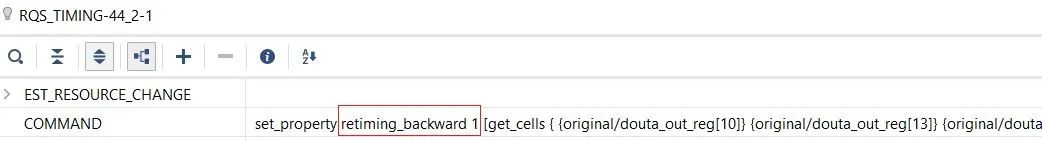

上述两种方法人工干预度都较低,如果用户能够判定哪些路径上的触发器可搬移以改善相邻路径的时序,那么就可以使用Vivado提供的综合属性RETIMING_BACKWARD或RETIMING_FORWARD,直接将其作用于指定的触发器。另外,在PSIP阶段还可以使用属性PSIP_RETIMING_BACKWARD或PSIP_RETIMING_FORWARD实现Retiming。对用户而言,这一过程还是有一定难度的,好在Vivado提供了另外一种方式就是QoR建议,有时该报告就会包含Retiming的相关设置,如下图所示。这样用户只需将该建议添加到工程中直接使用即可。

此外,phys_opt_design还提供了-directive AddRetime,既可在布局之后执行也可在布线之后执行。本质是是因为phys_opt_design提供了选项-retime。

审核编辑:黄飞

-

FIFOPrimitive在Block RAM上有什么优势?2019-02-27 2126

-

Block RAM的功耗始终为0mW2019-03-13 2173

-

请帮助我解决Block RAM问题?2019-06-04 7760

-

创建Block RAM IP不起作用2019-06-05 1888

-

请问9K Block RAM设计中那些2 9K Block RAM在哪里?2019-06-06 3207

-

SPARTAN-3AN怎么使用标准JTAG命令读取Block RAM内容2019-06-11 1900

-

用INIT_XX初始化Block RAM的方法有哪些?2019-07-22 2107

-

为什么Spartan 6 block ram有2个时钟延迟?2019-07-25 2560

-

请问分布式RAM和Block RAM的芯片中有menexternalmemory或内存吗?2019-11-07 2605

-

怎么使用virtex 5上的Block RAM来实现延迟线?2020-06-18 1428

-

如何使用Block RAM及利用其功能和性能优势2018-11-23 5686

-

xilinx 7系列FPGA里面的Block RAM2020-11-23 9388

-

关于Block RAM的寄存器输出2021-03-26 2490

-

FPGA中block ram的特殊用法列举2020-12-24 2104

-

超高数据流通量FPGA新品类中的Block RAM级联架构2023-07-13 1104

全部0条评论

快来发表一下你的评论吧 !