PLD设计速成(2)-采用原理图设计三人表决器

HDL语言及源代码

描述

我们根据三人表决器的直值表,可以通过卡诺图化简可以得到:

L2=SW1SW2 SW1SW3 SW2SW3

L1=_L2

那么我们可以在MAX plusII中用原理图实现上面的三人表决器

下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过:

(1)打开MAX plusII

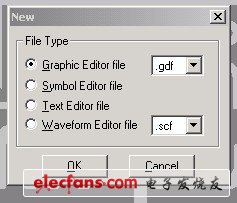

(2)新建一个图形文件:File菜单>new

新建文件时选择Graphic Editor file

点OK

(3)输入设计文件

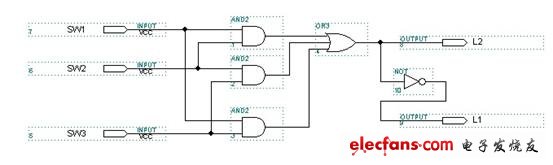

我们现在在图形文件中输入电路,我们这个电路需要AND2、OR3、NOT三个逻辑门电路和输入输出端,你可以

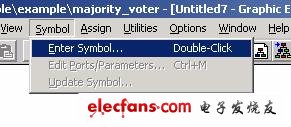

Symbol ->Enter Symbol(或者双击空白处)

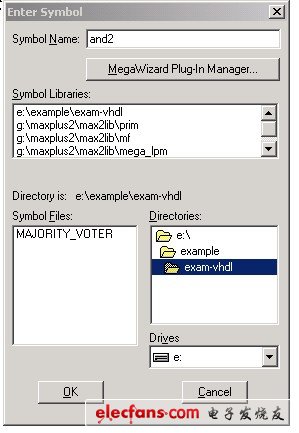

弹出窗口:

在Symbol Name中输入and2,点OK

同样可以加入or3、input、output、not

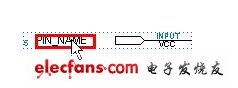

对input、output,鼠标左键双击PIN_NAME,那么PIN_NAME被选中,并且变黑,然后输入你要改的名字,如SW1

把元件拖动到合适位置,将光标放到元件的引线出,可以发现光标变为十字星,此时摁住左键就可以进行连线。

最后的电路图如下图

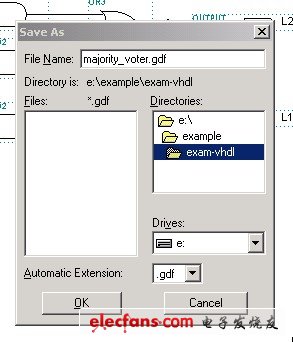

(4)保存文件:

保存为majority_voter.gdf,Automatic Extension选.gdf

把文件设为当前工程:FILE->PROJECT->SET PROJECT TO CURRENT FILE

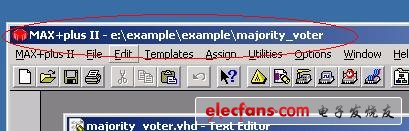

MAX PLUS II的标题条将显示新的项目名字

至此,程序输入就已经完成了

(5)检查编译

指定下载的芯片型号

指定芯片的管脚

(参见10分钟学会PLD设计2 -设计的编译)

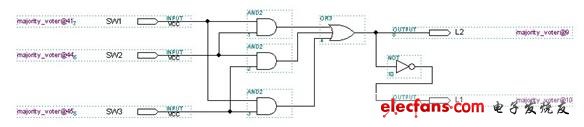

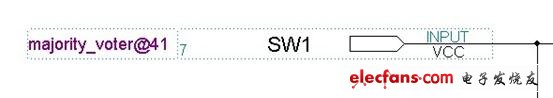

此时的图形为:

下图为SW1放大的图,其中majority_voter@41中前部分为设计的文件名,后面41为EPM7128SLC84-15的41脚,也就是说电路图中SW1被指定到EPM7128SLC84-15的41脚(而实验板上41脚被连接到指拨开关SW1上了,这样电路图上SW1就和实验板上的硬件SW1实现了连接)。

-

protel dxp三人表决器2022-06-14 2282

-

组合逻辑电路三人表决器的设计资料详细说明2019-12-03 4989

-

设计一个三人表决器电路,只是用简单的电子元器件,不适用芯片2019-09-29 10493

-

锆石FPGA A4_Nano开发板视频:三人表决器的功能叙述与设计2019-09-23 3172

-

三人表决器的VHDL设计实现,求代码2018-11-10 9507

-

74LS138和与非门设计三人表决器 74LS138设计详解2018-08-07 179250

-

74ls00制作三人表决器电路详解2018-02-08 277902

-

74LS153实现三人表决电路(4种方式实现3人表决电路)2018-01-26 397840

-

三人表决器电路设计方案汇总(两种仿真+三种逻辑电路设计)2018-01-17 340101

-

EDA/三取二表决器设计2016-01-15 1746

-

8人表决器2015-04-12 4047

-

7人表决器2013-04-23 7327

-

用AT89C51实现三人表决器2012-08-14 3972

-

三人表决器:VHDL源代码2012-05-18 22438

全部0条评论

快来发表一下你的评论吧 !