向FPGA设计添加复位功能的注意事项

嵌入式技术

描述

本文将探讨向 FPGA 设计添加复位输入的一些后果。

本文将回顾使用重置输入对给定功能进行编码的一些基本注意事项。设计者可能会忽视使用复位输入的后果,但不正确的复位策略很容易造成严重处罚。复位功能会对 FPGA 设计的速度、面积和功耗产生不利影响。

在继续讨论之前,有必要强调一个基本原则:FPGA 是可编程器件,但这并不意味着我们可以对FPGA 中的每个功能进行编程。这一基本原理将在本文的其余部分进一步阐明。

添加重置输入之前请仔细阅读详细信息

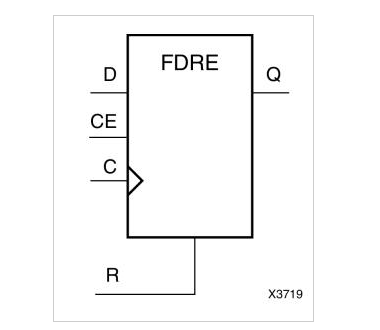

图 1 显示了 Xilinx 7 系列 FPGA 中提供的 D 型触发器 (DFF)。

图 1. Xilinx 7 系列 FPGA 的 FDRE D 型触发器。图片由Xilinx提供。

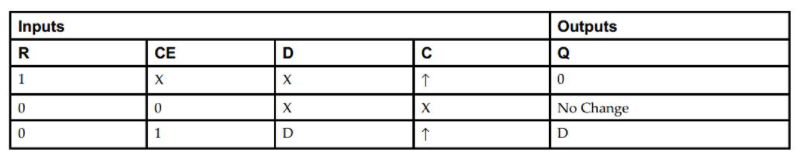

这种特殊的 DFF 具有同步复位 (R) 和时钟使能 (CE) 输入,在 Xilinx 库指南中称为 FDRE (触发器, D 型,同步复位,带时钟使能)。该元件的逻辑表如图2所示。

图 2. Xilinx 7 系列 FPGA FDRE D 型触发器的逻辑表。图片由Xilinx提供。

其中,R、CE、D 和 C 是 DFF 的输入,分别代表复位、时钟使能、数据输入和时钟。X 表示“无关”,↑ 表示时钟上升沿。复位是同步的,因为它只能在时钟的上升沿复位输出。

此 DFF 是一个设计元素,可用作更大设计的构建块。我们可以用它来注册所需的信号。而且,我们可以根据需要自由使用 FDRE 的复位和时钟使能输入。

我们可以选择是否要使用构建块的可用功能。但是,我们无法将不受支持的功能添加到给定的构建块中。作为示例,请考虑上面讨论的 FDRE 元素。该设计元素仅支持同步复位。如果我们同时需要异步和同步复位,我们将无法使用 FDRE 触发器。在这种情况下,综合工具将不得不使用其他资源,或者甚至可能求助于使用可用构建块的组合来实现所需的设计。正如您所看到的,FPGA 的低级功能是固定的,但一旦配置了这些设计元素,我们就可以按照我们想要的方式将它们连接在一起并构建更大的设计。

作为 FPGA 粒度如何影响实现的更微妙示例,请注意,根据上述逻辑表,FDRE 的复位 (R) 输入相对于时钟使能 (CE) 输入具有更高的优先级(注意表的行表明当R为1时,CE不相关)。现在,假设我们的 HDL 代码使用具有复位和时钟使能输入的 DFF。并且,HDL 描述给予 CE 输入比 R 输入更高的优先级。同样,在这种情况下,综合工具将必须使用 FDRE 以外的资源,或者必须使用可用构建块的组合来实现所需的功能。有关此示例的更多详细信息,请参阅Xilinx 白皮书。

上述讨论表明,为了实现高效的设计,我们必须仔细研究 FPGA 设计元素的细节,就像我们在使用分立元件之前研究其数据表一样。在本文的其余部分中,您将看到该原则的一些其他示例。

移位寄存器查找表 (SRL16)

Xilinx 综合工具可以实现基于 LUT 的移位寄存器,其比简单级联一些 DFF 获得的结构更紧凑、更快。这些高效移位寄存器称为 SRL,不支持复位输入。这就是为什么,如果您的移位寄存器并不真正需要复位,您应该避免它,以便综合工具可以推断出移位寄存器的基于 SRL 的高效实现。如果您的代码描述了具有复位功能的移位寄存器,XST 将使用 DFF 实现设计,或者将使用SRL 周围的一些附加逻辑来实现复位功能。SRL 可以从简单的串联运算符中推断出来(请参阅XST 用户指南的第 154 页)。

块 RAM

与 SRL 的情况类似,我们无法使用显式重置来重置 Block RAM 的内容。这就是为什么当将设计映射到 Block RAM 时,我们不应该使用复位。您可以在这里找到更多详细信息。

乘数

与不支持复位的 SRL 或 Block RAM 不同,某些模块(例如乘法器)对复位类型有限制。这些模块仅支持同步复位。对于给定的乘法器,用同步策略替换异步复位可以将操作频率提高两倍或更多。

总而言之,不正确的复位策略会阻止综合工具有效利用 FPGA 中可用的优化模块。这会对设计的面积、功耗和速度产生不利影响。现在,让我们看一些示例,其中综合软件使用 DFF 的复位端口来执行一些优化。

使用设置/复位输入来优化实施

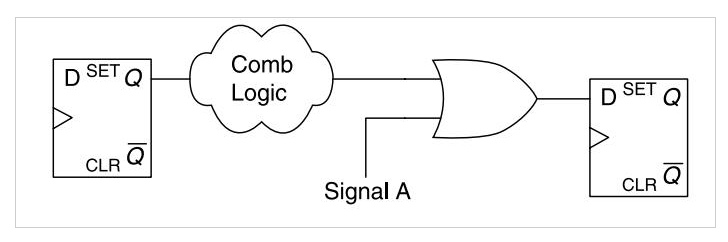

通常建议尽可能避免使用设置和重置输入。这有助于综合工具应用优化,检查 DFF 的设置/重置输入以简化实现。为了进一步阐明,假设我们要实现图 3 所示的原理图。

图 3.可以通过综合软件优化的特殊情况。图片由 FPGA 设计提供。

在图3中,当“信号A”为逻辑高电平时,无论组合电路“Comb Logic”的输出是什么,DFF输出都会在时钟边沿变高。这就是为什么,如图 4 所示,综合软件可以消除或门并将“信号 A”应用于 DFF 的同步设置输入。现在,当“信号 A”为逻辑高电平时,DFF 将在时钟沿设置为高电平。否则,输出将由组合电路“Comb Logic”决定。新设计提供了所需的功能,但现在取消了“或”门,并且设计的速度和面积都得到了提高。

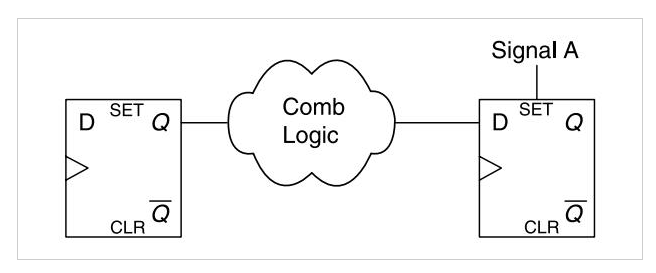

图4. 图 3 中电路的优化形式。图片由Advanced FPGA Design提供。

有趣的是,有时,综合工具可能会决定执行与上述优化相反的操作,并实现图 4 的原理图,如图 3 所示!这是因为,在 7 系列中,片中的所有 DFF 共享相同的 CK、SR(设置/重置)和 CE 信号。这意味着 SR 输入连接到“信号 A”的 DFF 不能与 SR 输入连接到“信号 A”以外的信号的 DFF 位于同一片中。如果控制信号(即CK、SR和CE)不相同,则DFF必须放置在不同的片中。这可能导致使用许多低扇出复位信号的设计中切片利用率低下。事实上,每个低扇出复位信号将使用切片的几个DFF,并且该切片的剩余DFF将被浪费。在这种情况下,综合工具可以实现图 4 的原理图,如图 3 所示。此过程将导致 DFF 不使用其复位输入。因此,这些 DFF 可以共享相同的控制信号,并且可以放置在同一片中。因此,设备利用率将会提高。

在图 3 和图 4 中,我们看到后跟 DFF 的 OR 门可以替换为使用其设置输入的 DFF。同样,我们可以将 DFF 后面的 AND 门替换为使用其复位输入的 DFF(参见下图 5)。

图 5.图片由Xilinx提供。

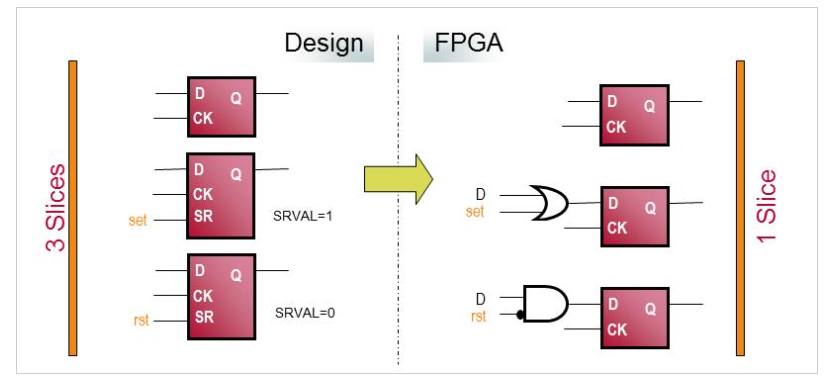

在图 5 中,SRVAL 属性指定断言 SR 输入后 DFF 的输出值。因此,对于左侧中间的DFF,SR输入被指定为设置端口。然而,对于左侧下方的 DFF,SR 输入实际上是复位输入。上部 DFF 不使用复位输入。

左边的三个DFF不能放在同一个slice中,因为它们有不同的控制信号。然而,通过上面讨论的转换,我们获得了具有相同控制信号集的三个 DFF。因此,我们可以将三个 DFF 放在同一个切片中。请注意,上述转换对于异步置位/复位信号无效。这就是为什么我们通常建议使用同步设置/重置信号而不是异步信号。

-

FPGA学习及设计中需要注意事项有哪些?2021-04-02 1852

-

FPGA仿真程序的设计方法,有什么注意事项?2021-04-29 1579

-

FPGA在逻辑设计中有哪些注意事项?2021-05-07 1274

-

Proteus仿真单片机串口的注意事项和实物调试注意事项2022-02-23 2031

-

向太阳能电网添加储能系统的四大设计注意事项2023-01-17 2768

-

FPGA设计的注意事项2010-04-10 1205

-

FPGA学习及设计中的注意事项2011-09-08 1080

-

STM32看门狗与复位IC同时存在的注意事项2020-03-06 6082

-

AN-1562:使用ADE9153A向系统添加电能监控时的布局注意事项2021-04-22 831

-

为FPGA设计添加复位功能的注意事项2023-05-25 1834

-

FPGA管脚调整的注意事项2023-06-20 1910

-

使用注意事项2023-07-07 996

-

FPGA的有源电容器放电电路注意事项2023-07-25 715

-

e² studio环境下添加源程序到当前工程的注意事项2023-07-04 2287

-

先进FPGA的电源设计注意事项(电源设计器121)2024-08-26 447

全部0条评论

快来发表一下你的评论吧 !