MC8051微处理器硬件模块

控制/MCU

描述

MC8051硬件模块

单片机作为一个大型设计,其内核由定时器时钟管理单元、ALU算数逻辑单元、串口及控制单元、存储单元RAM及ROM等模块组成。

1 时钟管理单元

MC8051内核采用完全同步的时钟设计。只有一个时钟信号控制每个存储单元的输入。没有使用门时钟,时钟没有输入到任何组合逻辑单元。中断输入线使用两级同步(锁存2次)与全局时钟同步。可以达到完全同步,即使用其他时钟的外部电路在驱动。并行I/0端口没有采用这种同步方式。

2 定时器、串口和中断

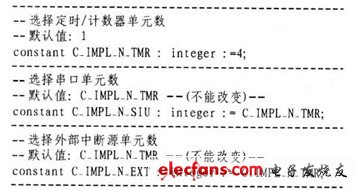

标准8051微控制器只提供两个定时/计数器单元、一个串口单元及两个外部中断源。而在MC805l IP核中,这些单元最多可增加到256组,只需修改VHDL源代码增加兼容的单元数。在VHDL源程序文件mc8051_p.vhd中,更改C_IMPL_N_TMR、C_IMPL_N_SIU、C_IMPL_N_EXT的常量值就可以,其范围是1~256。相关的VHDL代码如图1所示。

图1 相关VHDL代码

这里C_IMPL_N_TMR、C_IMPL_N_SIU、C_IMPL_N_EXT3个常量参数不能独立修改数值,只能同时增减。C_IMPL_N_TMR加l意味着对应的添加了2个定时/计数器、一个串口单元和2个外部中断源。为了能寻址所生成的单元而不改变微控制器的地址空间,在微控制器的特殊功能寄存器(SFR)内存空间增加了2个8位寄存器作为附加功能寄存器:分别是TSEL(定时/计数器选择寄存器,地址为Ox8E)和SSEL(串口选择寄存器,地址为Ox9A)。如果以上的寄存器指向不存在的器件单元,将使用默认的l单元,如果没有对这两个寄存器赋值,其缺省值为1。如果在中断发生期间设备(寄存器)没被选中(比如TSEL),那么相应的中断标志位将保持置位,直到执行中断服务程序。

3 存储器接口单元

由于采用优化结构设计,存储器采用同步结构,限制输入、输出的时序,因而存储器输入、输出数据没用寄存器寄存。

- 相关推荐

- 热点推荐

- 定时器

- 硬件模块

- MC8051微处理器

-

8051微处理器由哪几部分构成?2022-01-18 2205

-

基于S3C241OX微处理器和MC39i模块实现无线数据传输系统的设计2021-05-18 3398

-

MC8051 IP指令使用资源表2021-03-28 791

-

微处理器C8051F000资料推荐2021-03-23 885

-

如何将外部SPI Flash加载到FPGA内部ram然后复位MC80512019-06-11 1423

-

MC8051 IP核在Altera FPGA上的移植与使用2019-05-24 3191

-

基于MC8051内核的便携幅频特性测试仪设计[图]2018-01-19 731

-

【小梅哥FPGA进阶教程】第十章 MC8051软核在FPGA上的使用 上2017-02-17 11037

-

【超详细】MC8051 IP核在Altera FPGA上的移植与使用,基于芯航线FPGA核心板,小梅哥编写2016-03-11 39599

-

FPGA MC8051移植 100M频率计设计详细步骤2015-11-05 1026

-

基于MC8051 IP核和FPGA的频率计设计2012-12-24 2713

-

MC8051 IP核基本结构及原理2012-05-22 7913

-

基于IP复用设计的微处理器FSPLCSOC模块2010-05-17 2079

-

mc8051 design代码,MC8051 IP core2009-05-14 784

全部0条评论

快来发表一下你的评论吧 !