CoWoS封装在Chiplet中的信号及电源完整性介绍

描述

CoWoS封装在Chiplet中的信号及电源完整性

结论

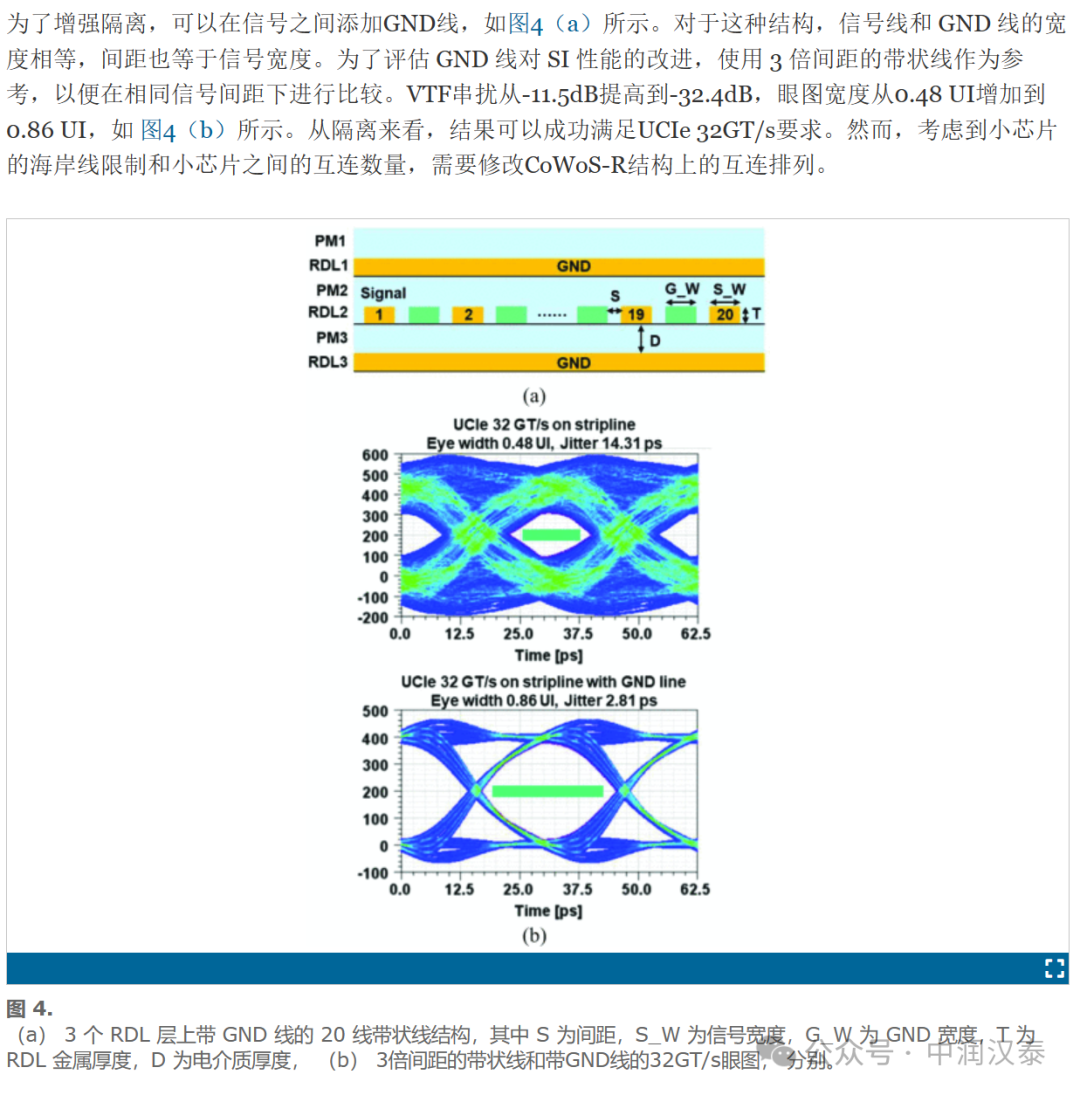

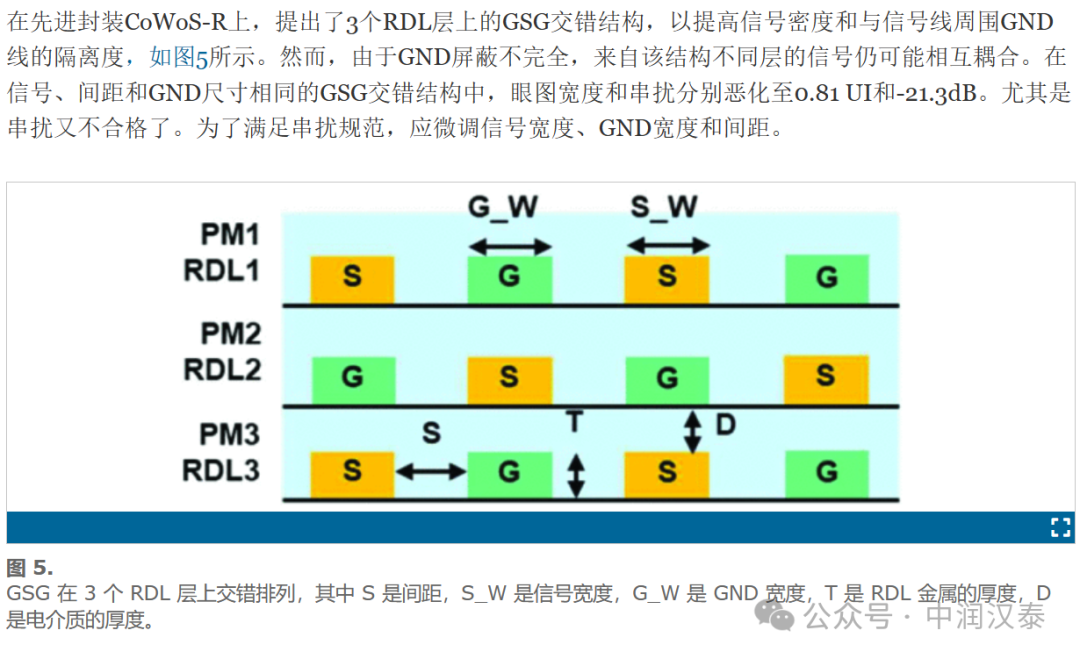

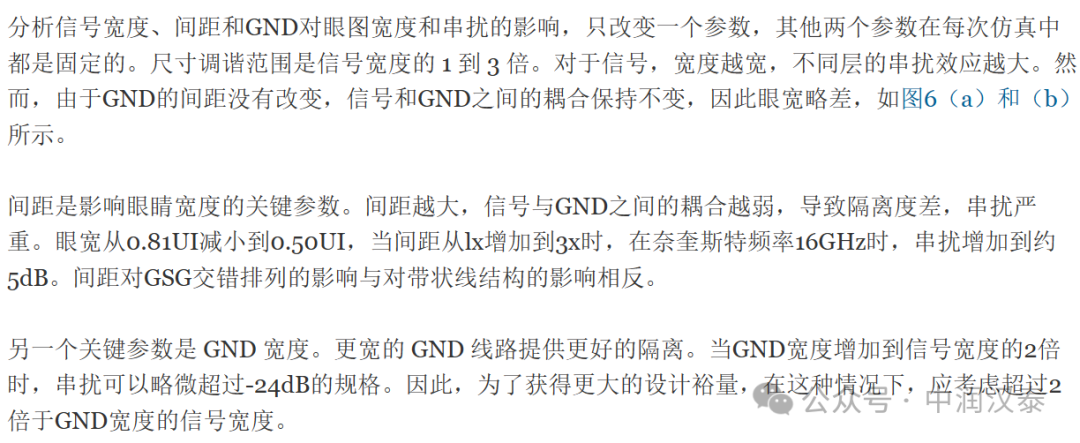

基于 CoWoS-R 技术的 UCIe 协议与 IPD 的高速互连是小芯片集成和 HPC 应用的重要平台。对于SI性能,研究了信号宽度、间隔和GND宽度对电气性能的影响。对于最高数据的 UCIe 32GT/s,信号线之间的接地屏蔽对于降低 VTF 串扰至关重要。在多层RDL结构中,GSG交错结构具有良好的串扰隔离和高带宽信号密度。最后,微调信号线、间距和GND线的尺寸,以获得CoWoS-R技术上最高的数据速率UCIe 32GT/s路由。

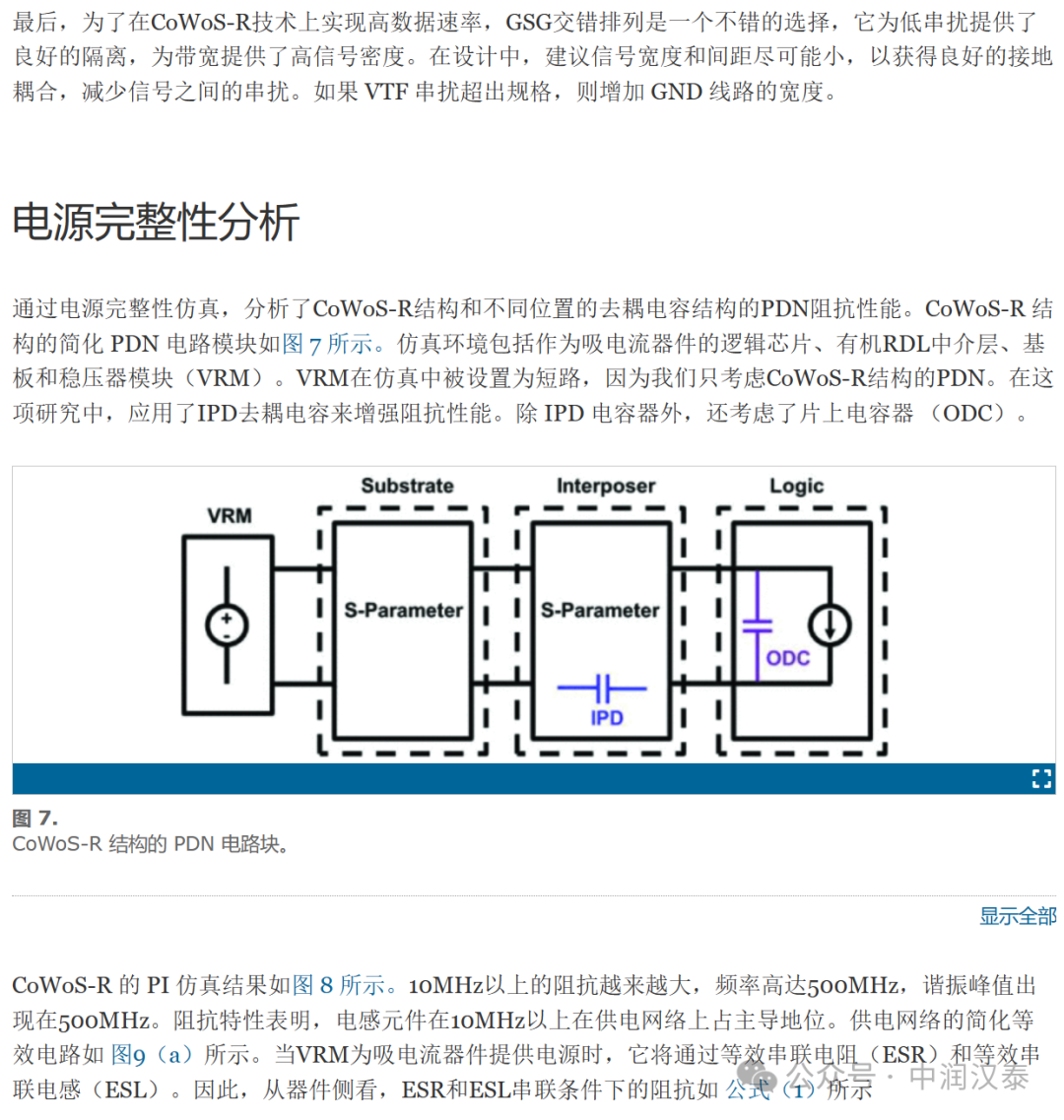

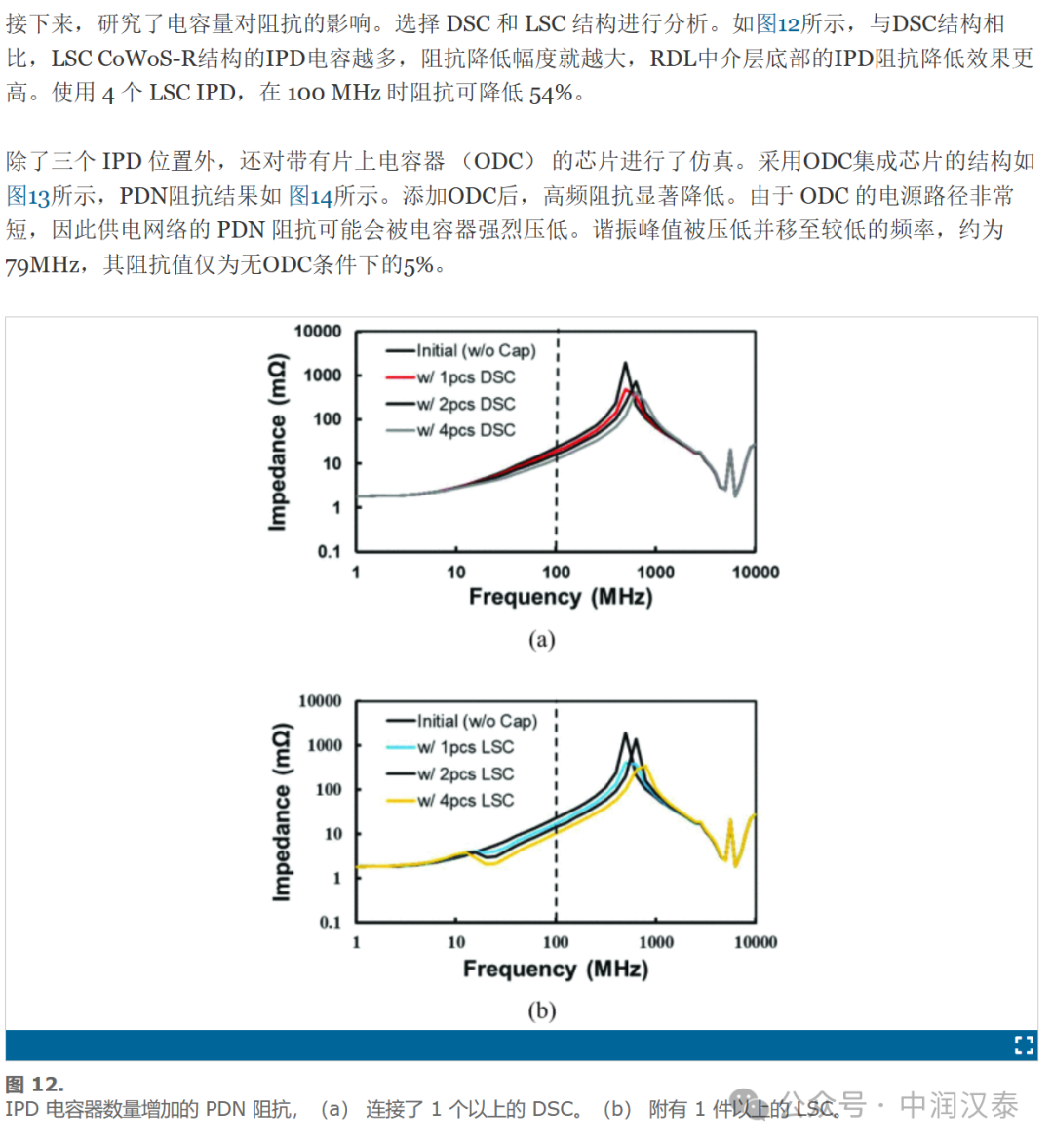

对于PI性能,分析了结构的PDN阻抗。为了降低总PDN阻抗,施加了IPD去耦电容。RDL中介层底部的IPD电容称为陆侧电容,在100 MHz时阻抗降低23%。使用 IPD 的 4,阻抗可以进一步降低 54%。除地面电容器外,还研究了片上电容器对阻抗的影响。它可以进一步降低谐振峰值和更高频率下的阻抗。

本篇摘自:CT,Wang, etc: Signal and Power Integrity Performance of CoWoS-R in Chiplet Integration Applications 2023

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

高速电路中的信号完整性和电源完整性研究2024-09-25 486

-

信号完整性与电源完整性-电源完整性分析2024-08-12 3271

-

如何利用全新互连系统提高电源完整性和信号完整性?2023-08-30 2121

-

信号完整性分析科普2023-08-17 9235

-

电源和信号完整性的分析与测试2022-01-07 1383

-

什么是电源和信号完整性?2021-12-30 2110

-

详解信号完整性与电源完整性2021-11-15 2557

-

信号完整性与电源完整性的详细分析2021-11-08 1836

-

信号完整性与电源完整性的仿真2021-09-29 1646

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 7032

-

高速信号的电源完整性分析2012-08-02 3612

-

信号完整性与电源完整性仿真分析2011-11-30 2109

-

2011信号及电源完整性分析与设计2010-12-16 3577

全部0条评论

快来发表一下你的评论吧 !