采用 Celsius PowerDC 仿真分析8层高速核心板的IR Drop和过孔电流

描述

当前数字系统的核心供电电压越来越低,而总的工作电流和布线密度则越来越大,从而导致直流问题日益突出。为了设计一个稳定可靠的电源系统,PI 仿真中的 IR Drop 直流压降仿真已被视作高速电路设计过程中不可或缺的环节之一。

IR Drop 指的是电源和地网络上电压的下降或者升高的一种现象,是指电路在直流工作时由直流电阻造成的电压降。当前芯片的制作工艺已突破到纳米级别,同时电路板上的走线也越来越密集,导致单位面积内电流急剧上升,再加上芯片与芯片之间的金属互联线宽度越来越窄,这就使得整个电源网络上的电阻值变大,当电源电流从电源端到达器件端时就会损失一部分电压,因此在电源网络的局部会存在一定的IR压降。

在实际设计一个电路板时,常常由于电源网络结构设计不合理而导致许多的IR Drop问题。这些问题表现为:

(1)电路板上的器件由于过压或者欠压而不能正常的工作。

(2)局部区域电流密度过大,引起此区域温度持续升高甚至烧

(3)I/O网络上的电阻过大,导致有用信号的严重衰减。

仿真案例

本文我们将采用 Celsius PowerDC 仿真分析8层高速核心板的IR Drop和过孔电流。

Celsius PowerDC 软件是一款专门用于电源完整性分析的工具,主要用于确保可靠的电源供应。对于承受高电流且工作在低电压条件下的产品,Celsius PowerDC 能提供精确的电性能分析。它能够分析从VRM(电压管理模块)到 SINK(负载端)的直流压降问题,这对于维持电源供应的稳定性至关重要。同时,它还能提供过孔与平面电流密度分析,通过分析过孔和平面的电流密度,Celsius PowerDC 可以帮助设计者优化布线,减少电磁干扰和提高信号完整性。并最终将分析结果以 2D 和 3D 的形式直观展现,使用户能够清晰地看到电流流动、热点分布和其他关键参数。

HI3516D是一块8层高速核心板的芯片,主频 0.9GHz,供电电压 VDD_CORE 为1.1V;DDR3 数据频率可达1.6GHz,接口电压DDR_IO为1.35V/1.5V。

仿真过程

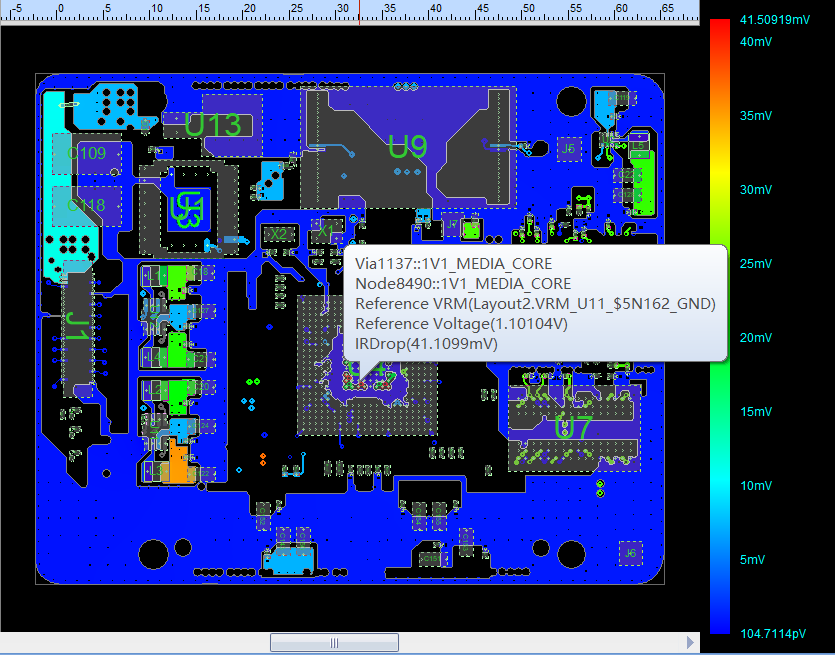

我们将根据实际选用材料,将软件中的电路板板材设置为FR4,芯板介质层设置为铜,过孔的铜壁厚度设置为1.4mil,填充材料使用SolderMask.以下为仿真结果,如下图所示。

从电压分布图上可以直观看出核心板电源模块的分布位置及走向。主控芯片U4处的IR Drop最大为226.24mV,超出了芯片的DataSheet规定的浮动范围 ,过大的IR Drop会造成U4的供电电压不足,使其无法正常工作。

,过大的IR Drop会造成U4的供电电压不足,使其无法正常工作。

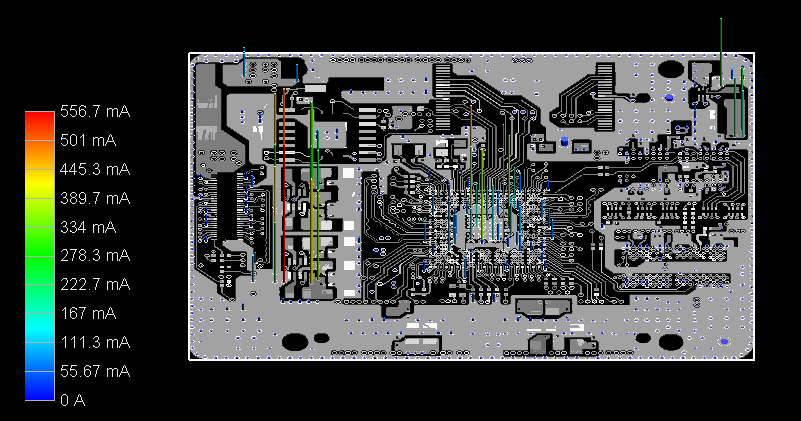

分析仿真结果,U4的供电电压经LDO转换,由电感器输出后有明显的损耗,检查电感器后发现是因为电感器自身的ESR过大造成了IR Drop过大。经损耗后的电压到达芯片U4处,由于该区域的电源网络覆铜面积过窄,导致连线上的电阻值较大,从而使得此处的IR Drop进一步变大。根据IR Drop分析的结果,可以很快找出电源网络的不合理之处,进行改进,从而确保整个系统的电源稳固性。依据分析,选用更小ESR的电感器,并且对U4的电源网络增加覆铜面积,如下图所示,整板的IR Drop下降到最大41.10mV,得到了明显的改善,满足了主控芯片的IR Drop限值。

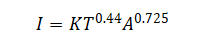

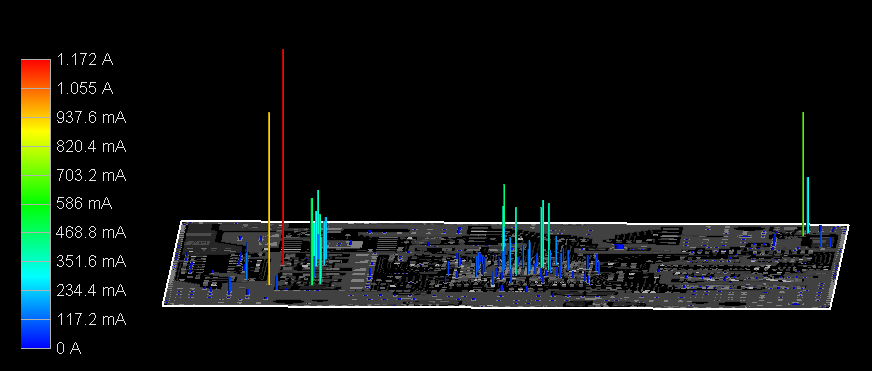

Celsius PowerDC 还可以进行对通过过孔的电流进行分析。在核心板的过孔电流分布图上可以看到U11、U12电源处过孔的电流分别为1.172A和937.6mA。此处使用的过孔孔径大小为10mil。过孔的通流能力的计算公式为:

常用且有效的解决办法是在保证电路信号质量的前提下:

1.增加过孔的数量:但要放置得当,避免形成瑞士干酪状布局

2.增加过孔的孔径:由于此处区域的走线过于密集,增大孔径会导致与过孔附近的线短路,所以此处选择在走线的间隙间添加过孔数量来进行优化。

在U11、U12靠近GND引脚处,将回流过孔均增加到3个,共同分担电流。如图4所示,优化后U11、U12的回流过孔上的电流分别降为最高556.6mA和501.4mA,效果显著。

长久以来备受工程师喜爱的口碑工具 Sigrity PowerDC 已升级为 Celsius PowerDC,在原有 PowerDC 高效签核 IC封装和 PCB 的直流分析基础上,整合了 Celsius 电热协同仿真,最大限度提升精度。整合升级后的 Celsius PowerDC 可以快速精准定位过度的压降,以及电流密度过大的区域和热点,从而最大限度地降低设计故障风险。如感兴趣,欢迎留言联系我们~

-

体积小 功耗低 工业级核心板2017-08-22 2879

-

Altium 4层核心板分享!2019-09-27 2080

-

高速差分过孔产生的串扰情况仿真分析2020-08-04 5085

-

【精品推荐】8层板设计的核心板实例讲解2021-04-24 5821

-

高速差分过孔的仿真分析2012-01-16 1565

-

高速PCB过孔的研究2017-11-18 2712

-

高速差分过孔之间的串扰仿真分析2018-03-20 1869

-

一款8层物联网网关核心板2022-03-23 2968

-

高速PCB设计:AM335X芯片核心板8层PCB实例详解2023-04-19 5090

-

IR Drop与封装分析2023-04-21 4716

-

Sigrity PowerDC是如何计算IR Drop Margin?2023-05-12 3518

-

IR Drop与封装(一)2023-06-16 2075

-

技术资讯 | PowerDC直流压降分析2022-03-01 5741

-

什么是DC IR Drop?DC IR Drop仿真有何意义?2023-09-28 7506

-

强悍的I.MX8MP核心板2025-02-13 949

全部0条评论

快来发表一下你的评论吧 !