从芯来到“香山”,芯华章助力国产RISC-V生态做了哪些事?

嵌入式技术

描述

4月18日,芯华章联合芯测、赛昉科技等7家公司举办联合技术论坛,吸引了来自阿里巴巴达摩院、新华三、寒武纪、芯来科技、华大半导体、蓝芯算力的几十位验证工程师参与。

在现场,我们的分享从 RISC-V架构的特点讲起,再到由此带来的验证挑战,以及针对这些挑战,芯华章验证工具做了哪些不一样的技术设计,获得了客户什么样的部署效果。

RISC-V生态:大家好才是真的好

2018年,ARM以“设计系统芯片之前需要考虑的五件事”为主题,从成本、生态系统、碎片化风险、安全性和设计保证方面指出RISC-V还有很多不足。

但6年过去,生态系统不断完善的RISC-V,因其开源、简洁、灵活等特性,采用率也正在快速增长,特别是在物联网、边缘计算和汽车电子等新兴领域。市场研究机构Semico Research预测,到2025年,RISC-V处理器核心将接近800亿个,成为X86、ARM之外的第三大架构生态。

作为一种新兴指令集,RISC-V的验证工作就尤为重要,因为比起成熟的架构,RISC-V充满了更多的开放性和不确定性。只有借助更充分、更完备的验证,才能保障基于RISC-V架构相关产品的稳定性,从而助力其获得大规模的商业部署。

特别是考虑到从架构到IP再到系统级应用,RISC-V都有自己区别于传统架构的独特挑战。我们认为其中有五个方面的内容比较典型,也是本次现场分享的重点:

◉ RISC-V 高性能处理器(CPU、GPU、AI等)的架构方案少、成熟度低,处理器设计团队需要在RISC-V芯片的应用场景上进行架构验证

◉ CPU定制程度更高,实现碎片化,需要更强更完备的验证,比如既需要单指令运行合规性验证;又需要完备的多指令运行验证:发现Data forwarding、Dead Lock等深层次的逻辑实现错误;浮点单元、AI加速单元等用户实现模块的精度高,验证难度大

◉ 从IP到SoC的实现过程需要大量的仿真和调试,高性能物理验证平台和高可调试的硬件仿真平台资源都不够用;PCIE/DDR/HBM等高性能外设需要系统级仿真验证方案

◉ 更多软件生态需要移植到RISC-V处理器,但由此带来的bug是软件问题还是硬件问题?定位和调试困难,需要更强大的软件代码-硬件电路联合调试手段

◉ 芯片的后端实现过程中,需要高效验证每个步骤变换的等价性

100亿颗RISC-V处理器一半来自中企

在验证领域,“初生牛犊”的芯华章,和“年轻的”RISC-V其实容易碰撞出更多火花。因为我们可以不受以前的技术包袱拖累,从底层架构创新做起,快速适应新的指令集扩展,同时提供灵活的脚本接口,允许工程师自定义验证环境,以适应不断变化的RISC-V生态系统。

在和国内领先的RISC-V处理器IP供应商芯来科技合作中,芯华章GalaxPSS智能验证工具,在多核CPU研发项目的cache一致性验证中就获得了客户的实名点赞。

创新引领 l 芯华章联手芯来科技提升RISC-V处理器设计验证

其中一个关键,是芯华章基于自主研发,已经打造了成熟的多核一致性模型。

借助这一模型,GalaxPSS可以方便地生成大量针对Cache Coherency的C testcase。C case中,我们也进行了expected result的计算,可以将读出的数据与Expected data进行比对,并将比对结果打印成log,方便客户高效完成后续调试。

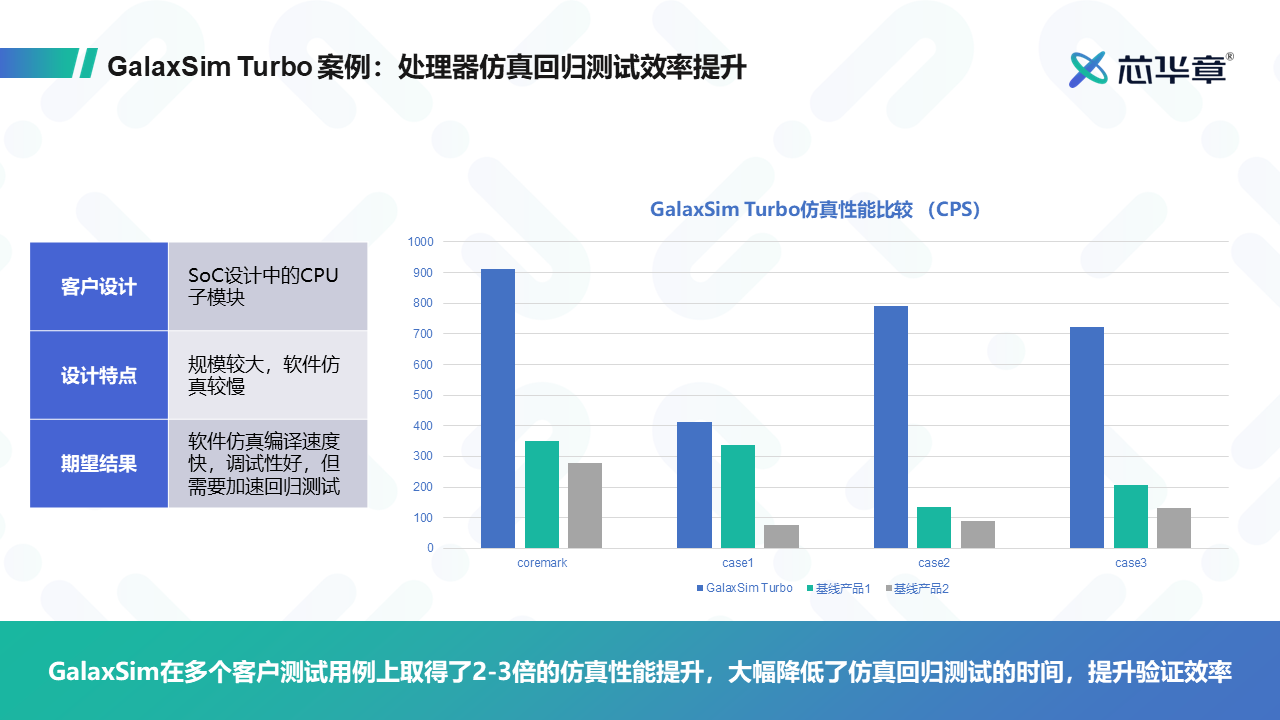

此外,GalaxSim通过对SystemVerilog和UVM标准的支持,能够为RISC-V CPU的研发提供仿真支持,同时其独有的Turbo模式更能成倍加速多核RV处理器的仿真验证效率。

目前,GalaxSim在多个客户测试用例上已经取得了2-3倍的仿真性能提升,大幅降低了仿真回归测试的时间,提升验证效率。

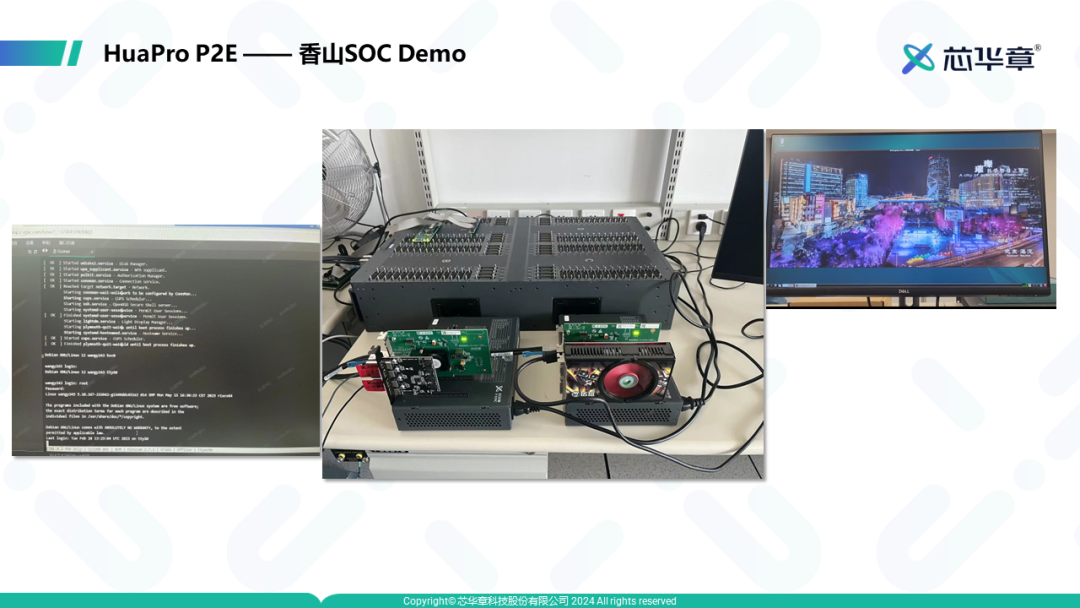

另一个不得不提的是“香山”项目。“香山”RISC-V,作为一个由中国科学院计算技术研究所孕育出的开源RISC-V处理器项目,在很多方面都极其有代表性。

比如高速子卡接口验证,以及通过高速PCIe接口将设计连接至真实的主机实现混合仿真,从而实现更好的软硬件协同验证等等。在这些方面,芯华章HuaPro P2E都发挥了很关键的作用。

因为不同于传统的原型验证或硬件仿真,HuaPro P2E基于统一的软件平台和统一硬件平台,实现了有效的创新双模工作形式:

◉ 硬件仿真模式下支持高达7千多个全信号互连,全信号不限深度的调试,以及各种虚拟验证方案

◉ 在原型验证模式下,通过一键式原型验证流程可以大大缩短验证时间,在超大规模SOC设计可以实现高达10M的仿真速率,以满足软件开发调试需求,同时还有丰富的接口解决方案

不仅仅是这些,芯华章Fusion Debug还针对RISC-V处理器提供定制调试服务,包括:

◉ 为客户的RISC-V core定制Fusion Debug CPU core模型

◉ 为客户的多核RISC-V CPU定制多核CPU模型

◉ 为客户的软件调试工具定制“硬件仿真-软件运行联合调试方案“,支持硬件电路和C代码的联合调试

同时,在芯片后端实现过程中,芯华章的GalaxEC也能够高效地验证每个步骤变换的等价性,确保设计在整个实现过程中的一致性和正确性。

一枝独放不是春,百花齐放春满园。根据RISC-V基金会的数据,截至2022年底,全球RISC-V处理器的出货量已达到100亿颗,其中近一半来自中国。

随着RISC-V技术的不断成熟和应用领域的扩大,芯华章将继续推动EDA工具的发展,助力RISC-V产业迈向新的高度。

- 相关推荐

- 热点推荐

- RISC-V

-

喜讯|昊芯RISC-V DSP荣获“中国芯”RISC-V生态推广奖2025-11-18 2526

-

开芯院采用芯华章高性能数字仿真器GalaxSim,RISC-V 验证获近3倍效率提升2025-11-17 2286

-

如意香山笔记本软件适配工作稳步推进,成功运行多款Linux发行版及国产办公套件2024-09-02 1466

-

思尔芯原型验证助力香山RISC-V处理器迭代加速2023-10-24 1871

-

RISC-V芯粒,终于来了2023-09-15 1721

-

助力开芯院“香山”项目!思尔芯亮相RISC-V中国峰会2023-08-26 1635

-

【RISC-V专题】芯昇科技RISC-V生态开发板首发试用2022-04-14 6101

-

道生物联基于芯来RISC-V内核,推出无线终端SoC芯片2022-03-22 2790

-

创新引领|芯华章联手芯来科技提升RISC-V处理器设计验证2022-03-03 2333

-

中科院发布国产开源高性能RISC-V处理器“香山”2021-07-01 2341

-

中科院重磅发布国产开源高性能RISC-V处理器“香山”2021-06-26 13058

-

沙龙活动:蓬勃发展的RISC-V生态2021-03-08 6217

-

千芯科技推出了针对芯来RISC-V平台的AI部署工具包(tinyAI SDK)2020-11-21 2473

全部0条评论

快来发表一下你的评论吧 !