氮化镓(GaN)功率集成电路(IC)开发的优势与挑战

描述

氮化镓(GaN)功率器件以离散形式已在电源充电器的应用领域得到广泛采用。在电源转换应用中,GaN高迁移率电子晶体管(HEMT)的诸多材料和器件优势也推动了它在多样化应用中的电源转换使用,例如数据中心、可再生能源和电动汽车。在本文中,我们将探讨创建GaN功率集成电路(ICs)的一些优势和挑战。

01

创造GaN功率IC的动机

基于硅的功率管理集成电路(PMICs)被广泛使用。许多晶圆厂现在提供先进的双极型CMOS-DMOS(BCD)集成工艺技术,它们包含最小门长约为90纳米或更小的CMOS低压器件和额定超过600V的DMOS器件。在这些工艺节点上,可实现超过125千门/mm²的高门密度。

集成允许在单一芯片中进行故障监控、门驱动和闭环控制与精确模拟电路。出色的器件匹配、广泛的无源器件(电阻器、电容器和电感器)可用性、基于非挥发性存储器的微调、高工艺产量以及成熟的PDK(工艺设计工具包)连同统计和极值模型,都有助于这些基于硅的PMICs在包括汽车在内的许多应用中的开发和使用。

GaN在电源转换方面相对于硅提供了许多优势。低导通和切换损耗以及在高切换频率下运行的能力带来了系统层面在电源转换效率、改善的功率密度和更简单的转换器拓扑上的优势。

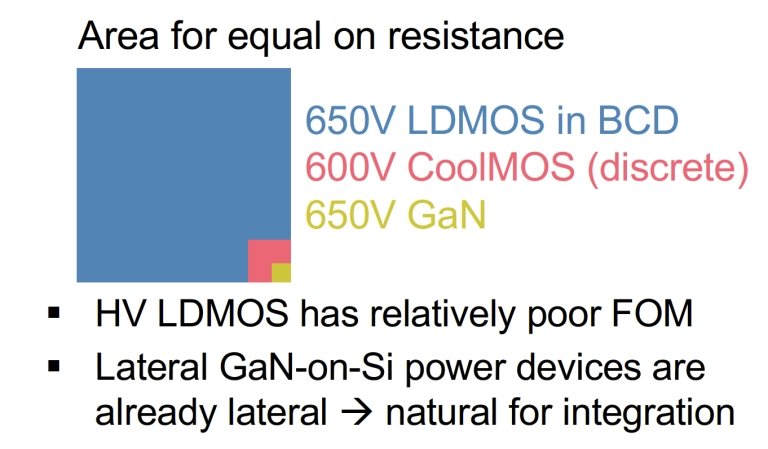

图1展示了一个例子。在这里,比较了在BCD工艺中使用的650V硅LDMOS器件、600V超结CoolMOS器件和650V GaN HEMT器件的特定开启电阻。图1中方块的面积表示大约可以转换为DMOS部分的硅BCD芯片的等效芯片面积改进,如果它被GaN替换的话。

GaN HEMT作为一种横向器件,也是器件集成的自然候选者。目标是利用GaN的许多优势,把它们应用到集成电路上,而采用硅BCD所达到的集成水平和性能则提供了一个激励指标。一个可能从这种单片GaN集成中受益的应用实例是用于多化学性(例如,结合LFP和NMC)电动汽车电池包(MCB)的七级飞行电容多级转换器1。在这项工作中创建的400至150V直流转换器原型采用了基于差分功率处理的闭环控制来优化MCB电池组内的电力组合。

图 1:特定导通电阻指标比较的图示

图 1:特定导通电阻指标比较的图示02

GaN IC集成的挑战为创建GaN功率IC,需要克服许多障碍,包括以下几点:

增强模式(e-mode)HEMT的典型阈值电压(Vth)为1.7V,最大栅极电压(Vgs)额定值为6-7V。这导致了器件栅极的噪声和过驱动裕度上的限制。尽管瞬态漏极过压额定值通常远远超过操作额定值,但单极性HEMT器件缺乏雪崩能力引发了关于器件未夹紧感应应力和短路鲁棒性的问题。硅和碳化硅MOSFET通常具有更强的栅极过驱动额定值(最大Vgs约为20V)。更高的Vth使得更容易实现栅极驱动电路,这可能是单极性的(即,不需要负驱动来关闭器件)。e-mode HEMT的另一个特性是比硅和碳化硅MOSFETs有着更高的栅极漏电流(Igs)。这个高Igs,可以在Vgs为5V时达到1µA/mm的量级,对许多需要采样和保持功能的模拟电路的性能产生负面影响。

与 Si CMOS 相比,缺乏可行的 PMOS HEMT 器件使 GaN 功率 IC 集成处于很大的劣势。低泄漏 CMOS 允许以较小的栅极长度实现高水平的低压逻辑集成。可以创建基于使用增强模式 HEMT 的电阻晶体管逻辑 (RTL) 或使用增强模式和常开耗尽模式 (d 模式) HEMT 的直接耦合 FET 逻辑 (DCFL) 的逻辑电路。然而,它们的泄漏比 CMOS 逻辑高得多。

GaN HEMT 的光刻水平比当前 Si BCD 工艺流程中低压 CMOS 的光刻水平落后约 20 年(约 1 µm 与 90 nm)。这使得逻辑和控制电路变得更大,并在一定程度上抵消了集成芯片高压部分的尺寸优势。

创建复杂 IC 所需的 PDK/建模基础设施在 GaN 电源设计生态系统中仍处于起步阶段。

缺乏高比电阻集成电阻器也会导致尺寸劣势。电阻器采用相对低电阻率的二维电子气 (2DEG) GaN HEMT 通道。

工艺稳定性和匹配是人们关心的问题,特别是对于电流镜和感测电路等缩放电路。Si BCD 在优化设计和工艺流程方面拥有数十年的经验,可实现出色的均匀性和可重复性,让设计人员的工作更加轻松。

产量和成本是 GaN 落后的重要指标。这些是大规模制造的关键。硅基氮化镓 (GaN-on-Si) 工艺流程的质量得到了显着提高,并且 8 英寸制造量不断增加,这可以降低成本并加快学习周期。

03

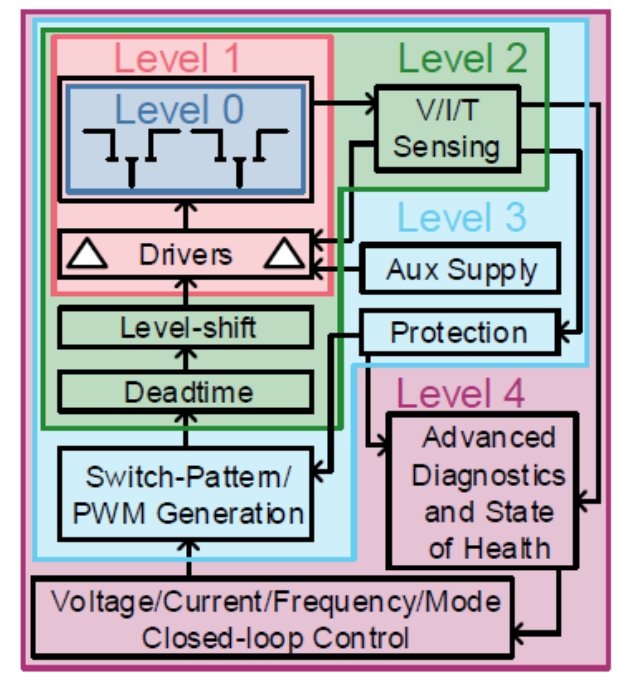

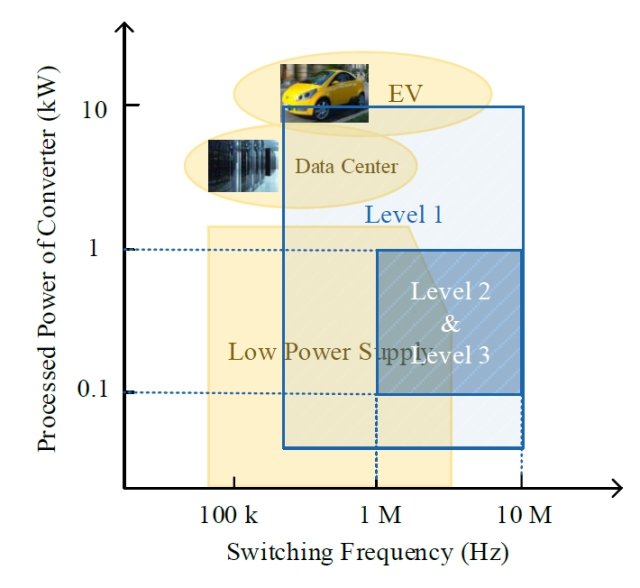

可以进行许多级别的集成,本质上是在增加的特性和功能与流程和集成复杂性之间进行权衡。图 2 描绘了显示这些不同级别的图表:

0 级和 1 级集成了电平转换和栅极驱动。可以实现较低的栅极和功率环路电感,从而提高开关性能。

2 级增加了电流、电压和温度的片上感测。这增加了对故障情况的动态响应和鲁棒性。

3 级和 4 级将全闭环控制与 PWM 生成和先进的健康状态诊断集成在一起。

Level 1和Level 2已被一些功率GaN制造商采用,而Level 3和Level 4大多处于研发阶段。

图 2:功率 GaN IC 集成水平

图 2:功率 GaN IC 集成水平

04

GaN IC集成方法和实例

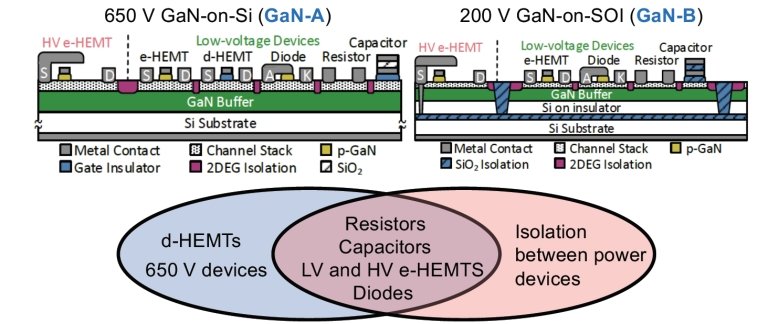

图 3 描述了功率 GaN IC 集成的两种方法。GaN-A(左)基于用于分立功率 GaN 器件的标准 GaN-on-Si HEMT 工艺流程。e-HEMT 和 d-HEMT 以及 2DEG 电阻器和金属-绝缘体-金属电容器的组合允许 DCFL 逻辑与高压 e-HEMT 器件集成。GaN-B(右)采用 GaN-on-SOI 工艺流程。GaN 器件和 Si 衬底之间以及器件之间使用沟槽隔离实现隔离。RTL 可与类似于 GaN-A 流程创建的增强型 HEMT 逻辑器件、电阻器和电容器以及高压增强型 GaN 器件集成。

图 3:GaN IC 集成的两种方法

图 3:GaN IC 集成的两种方法

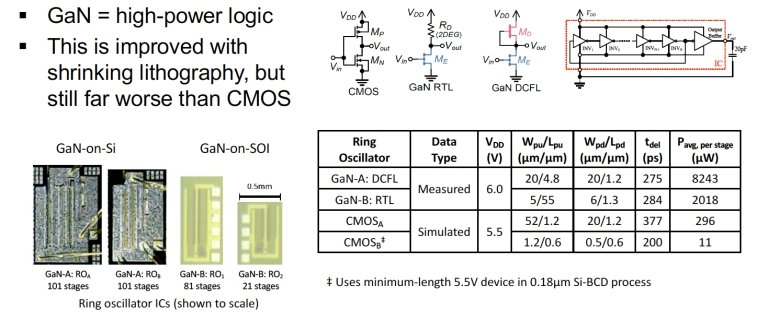

图 4 描述了这些集成方法与采用 CMOS 的 Si BCD 相比的一些逻辑功耗缺点。比较了 GaN-A DCFL 与 GaN-B RTL 和 CMOS 之间的环形振荡器性能。GaN-A 和 GaN-B 流程在不同的代工厂运行。虽然 GaN-A 和 GaN-B 逆变器的设计目标是相同的栅极延迟,但 DCFL 低侧 e-HEMT 宽度比 RTL 电路大 3 倍以上,导致功耗相对较高。对于类似的栅极延迟,这两种 GaN 电路的功率/级消耗至少比 CMOS 高一个数量级。

图 4:GaN-A、GaN-B 和 CMOS 之间的环形振荡器比较

图 4:GaN-A、GaN-B 和 CMOS 之间的环形振荡器比较

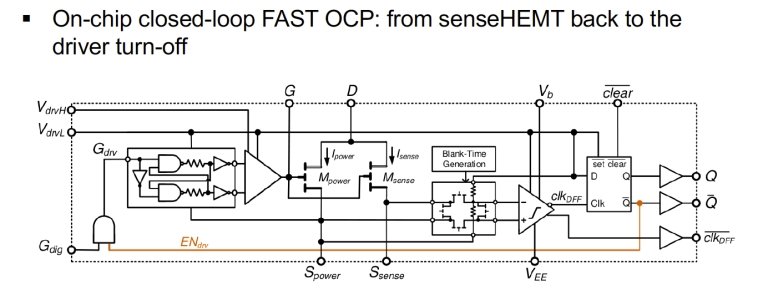

多伦多大学 Trescases 团队实现的 GaN IC 集成的一个有趣例子是过流检测电路与功率 HEMT 的集成。2该电路使用 SenseHEMT 进行电流感应、基于图腾柱的栅极驱动器和一组逻辑电路来实现闭环过流保护 (OCP)。OCP 等故障检测对于过压和过流容限较差的快速开关 GaN 器件至关重要。虽然这种集成也可以通过与 Si BCD 芯片共同封装的两芯片方法来完成,但单片集成有助于缩短保护响应时间。同时,还实现了面积效率以及更简单的装配过程。

该 OCP 电路(如图 5 所示)是在 200V SOI 上 GaN 工艺上实现的。它具有可调节电流限制和可编程消隐时间。

图 5:采用 GaN 的集成过流检测电路

图 5:采用 GaN 的集成过流检测电路

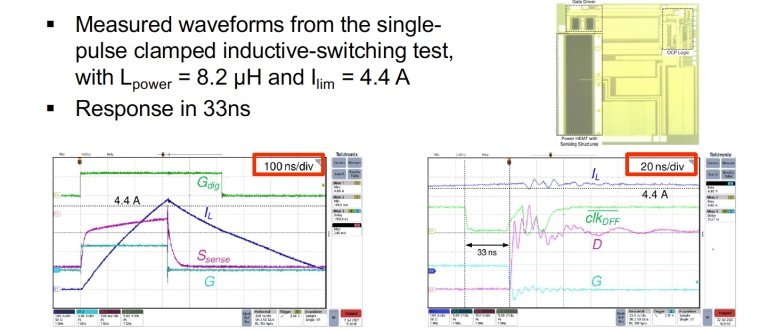

单脉冲钳位电感开关测试的测量波形如图 6 所示。响应时间为 33 ns。这是 GaN 功率器件实现的最快 OCP 电路响应时间之一。

图 6:显示集成 GaN IC 的 OCP 响应时间的波形

图 6:显示集成 GaN IC 的 OCP 响应时间的波形

GaN 集成面临多项挑战。当前的集成水平可能受到多种因素的限制,例如泄漏、工艺稳定性、成本、产量以及缺乏完全开发的 PDK/建模生态系统。目前光刻水平远高于Si CMOS。有助于加速 GaN PMIC 开发的关键突破包括创建可行的 PMOS 器件和更高比电阻的电阻器。如图 7 所示,预计 1 级集成将成为数据中心和电动汽车等约 10 kW 或更高功率级别应用的主流。随着工艺稳定性和产量的提高,2 级和 3 级集成将在低于 1 kW 的范围内得到更多采用,这对于电源适配器非常有用。

图 7:集成 GaN IC 的预期应用空间

图 7:集成 GaN IC 的预期应用空间

以上就是关于氮化镓(GaN)功率集成电路(IC)开发的优势与挑战的所有内容,看完之后想必你对氮化镓(GaN)功率IC已经有了大致的了解,浮思特科技专注在新能源汽车、电力新能源、家用电器、触控显示,4大领域,为客户提供功率IC产品选型采购的一站式服务,是一家拥有核心技术的电子元器件供应商和解决方案商。

-

氮化镓(GaN)功率IC在电机逆变器中的应用: 优势、实际应用案例、设计考量2025-03-12 2596

-

有关氮化镓半导体的常见错误观念2023-06-25 28334

-

GaN功率半导体(氮化镓)的系统集成优势介绍2023-06-19 19705

-

GaN功率集成电路在关键应用中的系统级影响2023-06-16 751

-

什么是氮化镓功率芯片?2023-06-15 2470

-

论文研究氮化镓GaN功率集成技术.zip2023-01-13 801

-

请问氮化镓GaN是什么?2021-06-16 2857

-

什么是氮化镓(GaN)?2019-07-31 8021

-

氮化镓GaN技术助力电源管理革新2018-11-20 2102

-

IFWS 2018:氮化镓功率电子器件技术分会在深圳召开2018-11-05 5438

全部0条评论

快来发表一下你的评论吧 !