奕斯伟计算“教育小脑”以边缘计算+AI技术助力教育场景智能化升级

电子说

描述

4月19日-21日,第83届中国教育装备展示会在重庆举办。作为核心计算设备及算法提供者,奕斯伟计算“教育小脑”边缘智能站助力智慧实验厂商展示了基于AI技术的智慧实验考试、教学场景解决方案。

奕斯伟计算“教育小脑”边缘智能站是以边缘计算+AI技术为核心打造的聚集高效率、高性价比的理化生实验教学和考试等场景的智能化方案,助力教育设备客户实现数字化、智能化升级。

以教育小脑为核心的理化生智能实验方案特点:

边缘计算、实时分析:依托边缘算力,基于需求灵活配置,实现高效实时分析;

通用化设计、跨平台开发:标准Restful接口设计,可输出多模态算法结果,支持各类实验应用的跨平台开发;

快速开发、快速迭代:内置基础开发框架,简化开发流程、缩短开发周期、标准化开发提升代码质量;

云边协同、远程运维:远程设备管理、OTA升级,有效降低运维成本。

贴近科学 覆盖全面

教育小脑紧贴学科需求,在教学、练习、考试各个环节实现AI赋能,支持AI教学实时赋分、考试结束离线后集中评分等模式。

内置算法目前已支持100+种实验器材检测,近100种实验操作行为识别,40+完整大纲要求必做理化生实验,能提供实时分析,可采用多模态算法识别结果,便于客户直接对接应用。

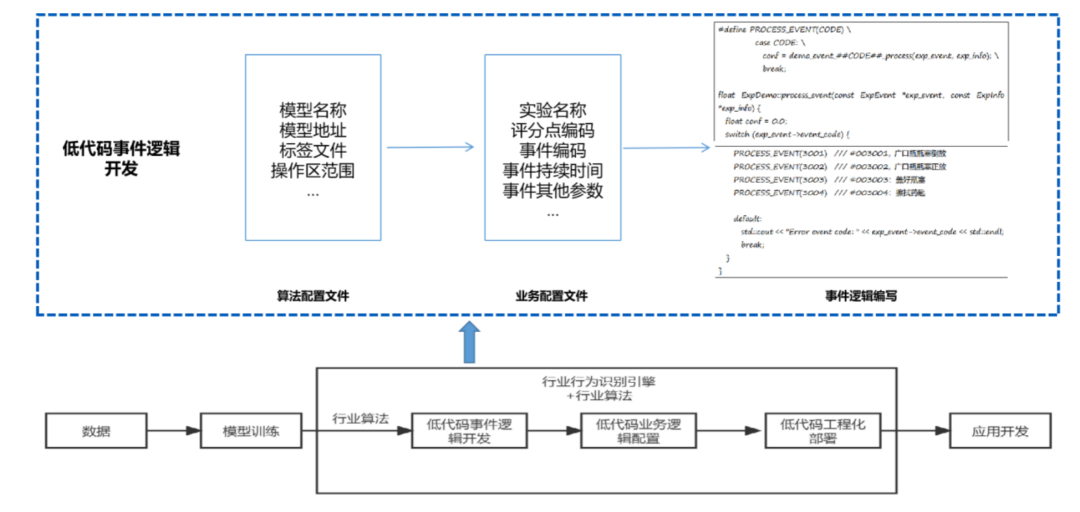

低代码快速开发 助力厂商高性价比、高效开发算法

除教育小脑内置算法外,客户开发人员可利用内置AI开发框架快速开发算法。内置的AI开发框架对理化生实验算法开发过程中涉及的推拉流、前后处理、算法平滑、对外接口等通用部分进行标准化封装,开发人员只需关注事件逻辑本身的编码,可大大提升开发效率和开发质量。

奕斯伟计算“教育小脑”行业算法开发流程

RISC-V边缘计算SoC 助力下一代教育小脑

搭载奕斯伟计算自研RISC-V边缘计算芯片EIC7700的下一代教育小脑即将推出,以更优性能助力客户智能化转型。

EIC7700在多项指标层面均实现了“进化”。EIC7700采用4核64位支持乱序执行RISC-V处理器及自研高能效NPU矩阵和矢量计算模块,支持大语言模型;DNN提供13.3TOPS INT8算力,可满足分类、检测、分割、追踪相关的各类需求;具备强大视频编解码能力,支持32路1080P 30帧的视频解码能力和13路1080P 30帧的视频编码能力,可与推理功能并行,图像信号处理器(ISP)可提供图像增强、动态对比度增强、畸变校正等多种图像处理硬件加速功能;拥有丰富的多媒体输入输出、PCIe、以太网等外部接口。

搭载EIC7700的新一代教育小脑针对教育场景下的AI应用,在计算算子、软件工具等方面做了专门优化,同时搭配奕斯伟计算自研AI智慧实验框架及算法,可提供性能更优、性价比更高的智慧教育解决方案。

2024世界数字教育大会上,中国科学院院士、教育部党组书记及部长怀进鹏指出:智能化是教育变革的重要引擎,我们将实施人工智能赋能行动,促进智能技术与教育教学(AI for Education)、科学研究(AI for Science)、社会(AI for Society)的深度融合,为学习型社会、智能教育和数字技术发展提供有效的行动支撑。这也是奕斯伟计算“教育小脑”解决方案助力客户要实现的重要目标。

-

奕斯伟计算和日本物联网与AI解决方案企业IoTBank签署战略合作协议2026-02-09 470

-

奕斯伟计算与Canonical签署许可协议,推动开源软硬件生态融合2025-12-26 1017

-

AI 边缘计算网关:开启智能新时代的钥匙—龙兴物联2025-08-09 1729

-

AI赋能边缘网关:开启智能时代的新蓝海2025-02-15 1482

-

奕斯伟计算通过季丰电子AEC-Q100认证测试2025-02-13 1626

-

奕斯伟计算公司在最新的RISC-V边缘计算SoC中将SiFive CPU、Imagination GPU 和自有NPU 结合集成2024-06-26 1545

-

奕斯伟计算:边缘计算SoC芯片EIC7700X,支持全栈浮点计算,全面加速生成式大模型2024-05-17 4481

-

奕斯伟计算展出应用于多场景的RISC-V架构芯片与方案2023-08-24 2042

-

奕斯伟计算即将亮相RISC-V中国峰会2023-08-22 1489

-

奕斯伟计算在RISC-V的战略布局2022-08-26 4242

-

瑞芯微芯片助力电力设备快速智能化数字化升级2022-07-25 2494

-

HarmonyOS现身中国教育装备展 助力教育信息化产业升级2021-04-23 1515

-

EdgeBoard FZ5 边缘AI计算盒及计算卡2020-08-31 2669

-

2018英特尔智慧教育峰会 以人工智能和边缘计算推动智慧教育2018-05-24 2258

全部0条评论

快来发表一下你的评论吧 !