利用 Ga-FIB 洞察 SiC 和 GaN 功率半导体结

描述

尽管传统高压平面 MOSFET 取得了进步,但由于阻断或漏源击穿电压因厚度、掺杂和几何形状而变化,因此局限性仍然存在。本文将讲解超级结 MOSFET(例如意法半导体的 MDmesh 技术)通过晶圆上又深又窄的沟槽来应对这些挑战。

01

该技术非常适合开关模式电源,采用超级结多漏极结构来降低漏源压降。高漏电或软击穿电压等问题可能是由块状形成中的污染物或缺陷引起的。因此,多尺度和多模态关联显微镜工作流程对于缺陷定位和分析至关重要,需要先进的硬件和软件解决方案来进行有效的样品研究。

功率半导体器件在感应加热、电动汽车和可再生能源等应用中因其效率和多功能性而受到重视,它们依赖于碳化硅和氮化镓等材料。与硅相比,这些材料具有较宽的禁带宽度和优异的性能,实现更高的击穿电压。

由高温、过流和过压等因素引起的运行故障需要彻底了解结效应和结构,这对于 SiC 在线监测、缺陷定位和可靠性分析至关重要。对于 GaN,可通过电子束感应电流 (EBIC) 等技术检测的位错带来了挑战,突出表明需要采用整体方法来表征功率半导体,以确保各种应用中的可靠性。

02

蔡司和 Kleindiek Nanotechnik 的开创性联合解决方案

在半导体的制造过程中,各种杂质往往会在晶格中引入缺陷,导致局部区域出现高电阻或高导电率。为了进行有效的故障分析,访问地下断层点并了解构造和连接剖面至关重要。在这些情况下,铣削对于器件制造中精确蚀刻半导体晶圆至关重要,这有助于以高度受控的方式去除层。

Zeiss 和 Kleindiek Nanotechnik 提出的技术由多个要素组成,其中 Zeiss Crossbeam 聚焦离子束扫描电子显微镜 (FIB-SEM) 用于铣削和成像。然后使用 Object Research Systems Inc. 的 Zeiss Atlas 5 和 Dragonfly Pro 软件来处理和可视化断层扫描数据。此外,Zeiss GeminiSEM 300 与 Kleindiek Nanotechnik PS8 Prober Shuttle 和 Keithley 4200-SCS 参数分析仪配对,可用于 EBIC 测量。

03

该解决方案如何帮助芯片制造商并提供进一步的见解

通过将被动电压对比 (PVC) SEM 成像与连续 FIB 材料去除相结合,FIB-SEM 断层扫描不仅可以可视化设备架构,还可以以 3D 形式可视化植入物形状。这用于连接点健康状况的 2D EBIC 调查,以进行故障分析、流程开发和监控。

根据 Zeiss 的说法,“EBIC 测量是在设备表面的 FIB 斜切处进行的。这种切割使器件保持功能,从而实现电接触,从而通过改变栅极电压来研究器件中几乎任何位置的结行为成为可能。”

FIB-SEM 断层扫描是分析硅或 SiC 功率器件电气故障的有用工具。它提供种植体形状的精确 3D 成像并表征有问题的区域。此外,它还通过提供有关各种植入区域的尺寸、均匀性和对准的信息来帮助工艺开发和监控。该数据对于解释单个横截面中可访问连接点的 2D EBIC 结果非常有价值。值得注意的是,这项研究并未包括对 GaN 器件的评估。

据观察,高能 Ga-FIB 铣削对硅基和 SiC 功率器件中的 SEM 掺杂剂对比成像和 EBIC 测量的影响可以忽略不计。这一发现使芯片制造商能够继续采用现有的 Ga-FIB 铣削工具和技术,而无需采用成本更高且维护密集的等离子 FIB 工具。

“这两种技术结合起来不仅可以告诉我们 pn 结的制造和植入物的去向,还可以告诉我们它的原位性能,”Kleindiek Nanotech 的发言人说。“这样的结果可以提供制造反馈以及功率器件实时运行的信息。这些对于 TCAD 仿真、器件性能和可靠性分析的总体验证非常有用。”

04

使用的显微镜技术

使用了多种显微镜技术,将它们结合起来可以产生理想的结果。SEM、FIB 和 SEM 原位电探测技术是使用的一些主要技术,其中使用 FIB-SEM 断层扫描的成熟技术完成掺杂剂区域的 3D 可视化,以补充 EBIC 的 2D 结检查。在掺杂成像中,研究人员最大限度地利用了 PVC,这是一种 3D 成像技术。

FIB-SEM 断层扫描利用二次电子成像以 3D 方式可视化电活性注入区域,而 EBIC 捕获 pn 结处的耗尽区状态,这些技术相互补充。

“PVC 是结点内置电势的函数;有些人可能将其称为结两侧不同电子亲和力的特性,”研究人员说。“结的负电[p侧]能够比正电[n侧]发射更多的二次电子。当您用电子束扫描结的两侧时,您会得到一张图像,其中黑色区域表示 n 型区域。该掺杂剂分析提供了植入物去向的图片以及 SEM 的分辨率。

“我们的断层扫描技术可以以 3D 方式观察这些植入物的分布,这是任何其他方法都无法实现的——整个设备可以被重建,”他们补充道。

05

铣削工艺按其技术规范进行

使用 30 kV 30 nA Ga-FIB 探针以与芯片表面成 36° 的角度切割硅基 IGBT 和 SiC 基 MOSFET 器件的横截面。硅 IGBT 的最终尺寸为 330 × 100 µm 2 , SiC MOSFET 的尺寸为100 × 20 µm 2 。使用气态 Pt 和 C 前驱体在横截面上沉积铂 (Pt) 和碳 (C) 保护层。在 FIB-SEM 断层扫描期间切割基准线以实现精确的切片厚度控制。

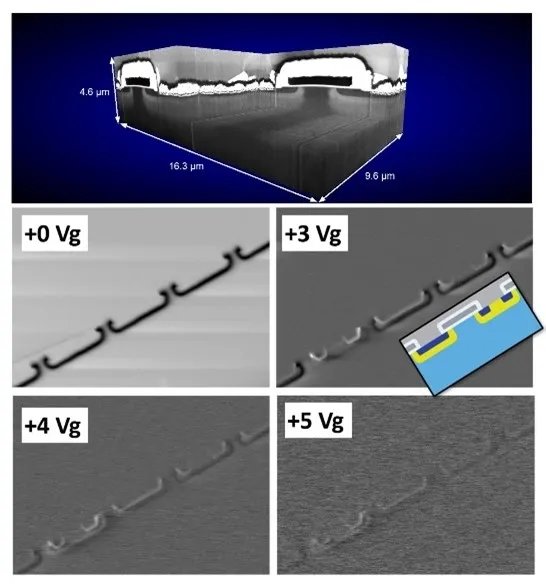

在感兴趣的体积前面铣削出一个大沟槽,并在自动化过程中去除厚度为 50 nm(硅 IGBT)或 30 nm(SiC MOSFET)的切片。每个切片后记录 SEM 图像,形成硅 IGBT 的 1,120 个切片的数据集 (38.5 × 13.4 × 56.0 µm 3)和 320 个 SiC MOSFET 切片(16.3 × 4.6 × 9.6 µm 3)。

当谈到 2D 掺杂剂成像和 2D EBIC 时,研究人员指出,“FIB 铣削方法的 EBIC 替代方案是机械切片,然后进行广泛的氩离子束抛光。” 另一方面,对于 3D 掺杂剂成像,“没有任何铣削方法可以替代使用 Ga 或其他离子种类的 FIB 铣削。”

06

束损伤和 Ga+ 扩散对模型的影响

研究表明,在功率器件中,Ga-FIB引起的表面非晶化和Ga注入并不是影响掺杂剂对比成像和EBIC的重要因素。

采用 EBIC 成像的 FIB-SEM 断层扫描

采用 EBIC 成像的 FIB-SEM 断层扫描上图中的顶部描绘了从 SiC MOSFET 捕获的FIB-SEM 断层扫描数据集。为了揭示器件内复杂的结构和掺杂剂分布,大约三分之一的体积被选择性地去除。

图中的 SiC 样品经过原位 EBIC 成像,以观察与栅极电压相关的耗尽区。+4-Vg 图像覆盖了各个注入区域,显示出随着栅极电压的增加,P 阱和 N CSL 外延层之间的耗尽区逐渐减弱。值得注意的是,N+源极/P阱层在此过程中变得越来越明显。

Zeiss 和 Kleindiek Nanotechnik 联合解决方案提供了一种分析 SiC 和 GaN 器件中功率半导体结的创新方法。通过将 FIB-SEM 断层扫描与先进的软件工具相结合,该技术可以对植入物形状进行精确的 3D 成像,从而为设备架构和连接健康状况提供有价值的见解。

在倾斜 FIB 切割处包含 EBIC 测量可以增强对电气行为的理解。这种综合方法可帮助芯片制造商进行缺陷定位、工艺开发和监控,从而提高功率半导体器件在各种应用中的可靠性。

以上就是关于如何利用 Ga-FIB 洞察 SiC 和 GaN 功率半导体结的全部内容分享。浮思特科技专注在新能源汽车、电力新能源、家用电器、触控显示,4大领域,主要供应功率半导体元器件:IGBT/IGBT模块、单片机、AC-DC芯片、IPM等。

-

第三代半导体材料盛行,GaN与SiC如何撬动新型功率器件2017-06-16 3761

-

报名 | 宽禁带半导体(SiC、GaN)电力电子技术应用交流会2017-07-11 5043

-

SiC GaN有什么功能?2019-07-31 3764

-

为什么GaN会在射频应用中脱颖而出?2019-08-01 2770

-

GaN和SiC区别2022-08-12 10138

-

什么是基于SiC和GaN的功率半导体器件?2023-02-21 10231

-

GaN功率半导体在快速充电市场的应用2023-06-19 1624

-

半桥GaN功率半导体应用设计2023-06-21 1760

-

利用仿真来估计功率半导体的结温2010-02-05 781

-

功率半导体材料GaN和SiC使用新趋势2012-07-02 1952

-

功率半导体的革命:SiC与GaN的共舞2013-03-07 5532

-

基于SiC或GaN的功率半导体应用设计2021-04-06 4661

-

SiC 和 GaN 功率半导体市场趋势,2019 年以来发生了什么变化?2020-11-16 3149

-

GaN和SiC功率半导体市场有望在2027年达45亿美元2021-05-21 2864

-

具有SiC和GaN的高功率2022-07-27 1532

全部0条评论

快来发表一下你的评论吧 !