晶体管级异质集成技术及其实用案例分析

描述

00 引言

近几十年来,半导体技术的飞速发展为信息技术革命提供了强大的技术支撑,在此期间指导半导体器件研发及其产业化发展的国际半导体技术发展路线图发挥了重要作用。国际半导体技术发展路线图不断得到滚动修订,是国际半导体工业界广泛认同的对未来半导体技术发展的最佳预测。2016年,国际半导体技术发展路线图被修订为国际器件与系统路线图,这一调整充分反映出基于摩尔定律的单纯器件技术发展遇到瓶颈,器件与系统的联动发展已成为半导体技术发展的主题。针对这一发展趋势,美国在上世纪九十年代就成立了微系统技术办公室(MTO),其重点工作就是推进半导体器件与系统的融合发展,满足系统应用对器件技术不断增长的需求。本文围绕后摩尔时代半导体微波器件技术的发展,介绍了开发的基于外延层转移的晶体管级异质集成技术,并结合南京电子器件研究所(NEDI)的工作,展示了该技术在典型微波功率器件和电路工艺中的应用。

01 后摩尔时代半导体微波器件技术的主要发展趋势

后摩尔时代半导体技术的发展主要有延续摩尔和超越摩尔两条路径。延续摩尔就是通过寻找新的物理机理、发现新的材料、设计新的器件结构,将器件的工艺能力推向更高的节点,满足电路芯片更高性能和更高集成度等发展需求。如采用碳纳米管研制的晶体管[1],由于材料性能优势,相比于同样栅长的SiCMOS可实现更高的速度和更低的功耗,有望通过新的半导体材料提升器件的工艺节点。超越摩尔则是在摩尔定律充分发展的基础上通过异类集成实现电路性能和功能的提升。异类集成的方法很多,在Si集成电路领域,更多的是通过晶圆级封装(WLP)的三维堆叠来实现,目前已有标准工艺,并实现了量产。这种三维集成不仅仅是同类功能电路晶圆的堆叠提升集成度,同时也可以是不同功能电路晶圆的堆叠,实现电路功能的增加,甚至构成片上系统(SOC),这一技术将成为后摩尔时代Si集成电路工艺技术发展的主流。

半导体微波器件是半导体器件大家族中的重要一员,后摩尔时代半导体微波器件的发展也同样存在SiCMOS遇到的瓶颈。不同于Si元素半导体,作为半导体微波器件发展主体的GaAs、InP、GaN等化合物半导体材料有非常丰富的异质结,异质结的采用可显著提升器件的频率、功率、线性等微波性能,大大拓展各种半导体衬底材料的应用空间。尽管如此,由于晶格失配、热失配以及外延生长工艺等因素的影响,高性能化合物半导体异质结的形成也受到种种限制,阻碍了单一化合物半导体器件微波性能的进一步提升。

类似于Si集成电路,后摩尔时代半导体微波器件技术也将沿着延续摩尔和超越摩尔两条路径发展。一方面将继续通过新型半导体材料[2]、新型异质结[3]、新的器件结构[4]提升器件的微波性能,另一方面则通过异类集成实现电路性能和功能的提升。 在异类集成方面,美国国防高级研究计划局(DAR-PA)近十多年来持续支持了“硅上化合物半导体材料(COSMOS,2008年)”、“多样化可用异类集成技术(DAHI,2012年)”和“通用异类集成和IP复用策略(CHIPS,2017年)”等多个重大项目[5-7]的研究,突破了异类集成关键技术,建立了异类集成标准工艺平台[8],为产品开发奠定了技术基础。欧盟也于2015年启动INSIGHT项目,旨在研发与Si CMOS相兼容的III-V族材料生产工艺以及在Si器件上的异类集成技术,面向超大功率、超宽带的微波毫米波应用,在实现高集成度和低功耗的同时,提升电路的工作带宽、输出功率和效率等微波性能。

半导体微波器件的异类集成又有两种不同技术发展方向,一种是类似于Si电路的圆片到圆片(Wafer to wafer)或芯片到晶圆(Die to wafer)的三维堆叠集成技术,另一种则是更充分体现半导体微波器件特点的晶体管级异质集成技术。为区分两类不同集成技术,前一种多称为三维异构集成,后一种则称为异质集成。这两种不同技术发展方向其技术特点有明显区别,前一类针对芯片间的集成,后一类则深入到不同材料、不同结构晶体管的集成。下面将重点介绍半导体微波器件异类集成技术中晶体管级异质集成技术的发展情况以及南京电子器件研究所在此技术方向的研究进展。

02 基于外延层转移的晶体管级异质集成微波器件技术

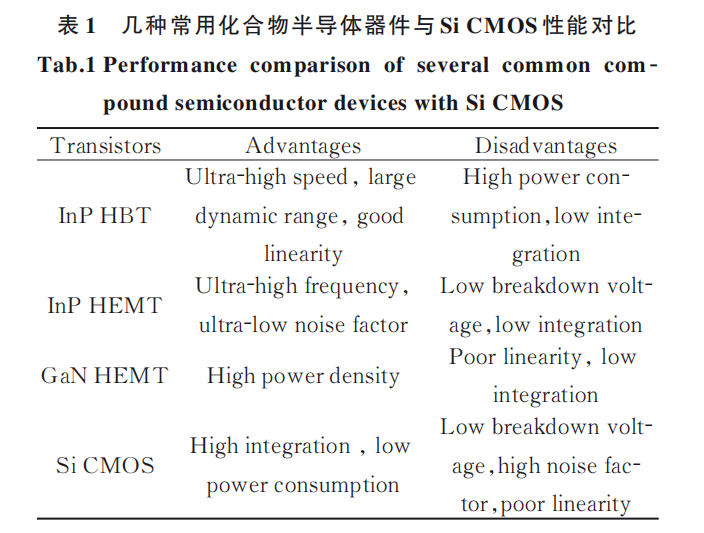

化合物半导体微波器件的典型特点是不同结型器件性能差异明显,表1给出了几种常用的化合物半导体微波器件与Si CMOS性能对比,另外化合物半导体还拥有GaAs PIN二极管、GaAs超突变结变容管等多种功能器件,晶体管级异质集成就是根据微波性能和功能需要,选择性能最合适的半导体器件集成到某一特定半导体衬底上,化合物半导体衬底本身由于其导热等性能差异,也是可选的集成对象,从而获得单一器件技术难以实现的器件或电路性能,摆脱在各类器件技术间权衡取舍的困境。不同于芯片到晶圆以及圆片到圆片的三维异构集成,晶体管级异质集成针对单个晶体管,集成精度达到微米级。

晶体管级异质集成技术其工艺途径主要有外延生长和外延层转移两种,外延生长异质集成典型的应用范例如微波接收系统所用的限幅低噪声放大器电路、光通信系统中应用的光探测器与跨阻放大器单片集成的光电集成电路(OEIC)等。外延生长异质集成技术涉及到多种结构异质结的依次生长、不同结型晶体管的制作,其工艺难度显而易见。不同结型器件工艺的兼容性问题还会影响器件性能,特别是芯片生产成本会明显增加。外延层转移晶体管级异质集成技术,是将完成主要正面工艺的外延层通过剥离转移并键合到另外一个也已完成主要正面工艺的晶圆上,最后互连起来完成整个电路的加工。外延层转移集成工艺可有效规避外延生长集成工艺存在的弊端,实现高性能、高集成目标。化合物半导体微波器件有GaAs pHEMT、GaN HEMT等平面结构器件与InP HBT、GaAs PIN等纵向结构器件两大类。平面结构器件其微波性能与外延层下高阻衬底的厚度密切相关,因此需开发介质键合工艺来保证器件的微波性能不受影响。基于InP HBT、GaAs PIN等纵向结构器件的微波电路,为减小电路损耗,有源器件均采用准平面结构制作在半绝缘衬底上。针对纵向结构器件的晶体管级异质集成,则完全可以恢复其纵向特征,通过金属键合到半绝缘衬底上,进一步提升器件的微波性能。介质键合和金属键合的工艺温度都不高,均属于低温键合。

近年来在各国多个重点计划的推动下,国际上晶体管级异质集成技术的研究也异彩纷呈。2017年德国FBH研究所采用外延层剥离转移介质键合工艺,研制出InP HBT与Si CMOS异质集成的328 GHz频率源,该芯片集成了SiGe VCO和InP放大器及倍频器,功耗和输出功率优于SiGe工艺电路[9]。2019年美国Teledyne公司报道了基于外延层转移工艺的W波段相控阵收发芯片[10],该芯片由0.25μm InP HBT与0.13μm Si CMOS异质集成而成,芯片集成了移相器、放大器和低噪放等多个功能。该芯片在90GHz饱和输出功率16dBm,同时直流功耗仅为885mW。其直流功耗、发射增益、噪声特别是输出功率等性能,均不同程度优于SiGe BiCMOS工艺芯片。近十多年来NEDI在国内率先开展了外延层转移异质集成技术研究,2015年实现了GaAs pHEMT与Si CMOS异质集成数控开关芯片之后,2017年实现了InP HBT与SiCMOS异质集成量化降速芯片[11],该电路工作速率13GHz,对低频和高频数据信号降速比达到1∶16,功耗小于1.2W,相较采用InP HBT工艺芯片功耗降低40%,相较采用40nm Si CMOS工艺芯片灵敏度和动态范围分别改善15dB和20dB。下面将给出NEDI在这一技术方向研究的新进展,并系统介绍介质键合和金属键合两套外延层转移异质集成工艺在典型微波器件和电路工艺中的应用。

2.1介质键合晶体管级异质集成工艺

基于SiC衬底的GaNHEMT微波功率器件是近二十多年发展起来的新一代半导体微波器件技术,充分体现材料性能优势的GaN微波功率器件和电路产品已在电子信息装备和移动通信基站等领域得到规模应用。目前工程应用的GaN HEMT其输出功率密度普遍低于10W/mm,而GaN HEMT已验证的最高输出功率密度可达到41.4W/mm[4],GaN微波功率器件性能还有巨大提升空间。散热是制约GaN HEMT输出功率密度提升的瓶颈,异质集成金刚石GaN微波功率器件是解决这一瓶颈问题的有效途径[12],基于介质键合的金刚石GaN HEMT是外延层转移晶体管级异质集成技术的一个典型应用。

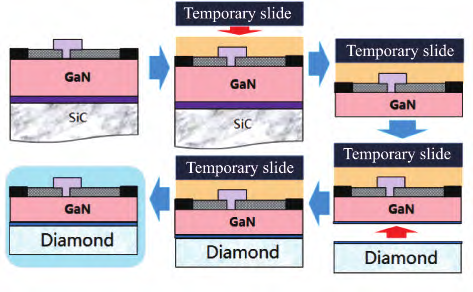

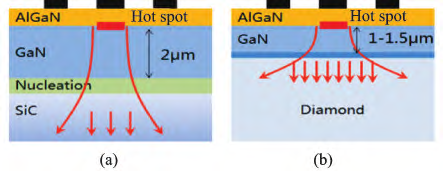

介质键合金刚石GaN HEMT具体工艺过程示意图如图1所示。先完成GaN器件工艺,然后去除SiC衬底并键合到高导热多晶金刚石上。该工艺在低温条件下完成,缓解了GaN与金刚石存在的严重热失配;先器件后键合,可充分发挥SiC衬底GaN HEMT工艺成熟以及金刚石导热衬底单独制备所带来的各自性能优势。当然该工艺也存在键合界面空洞率及界面热阻控制等工艺难题,需要重点攻克。在金刚石GaN HEMT研制方面,NEDI开展了多年研究,近年来突破了金刚石衬底GaN微波功率器件内部热传输机制、GaN外延层表面纳米级抛光以及金刚石衬底与GaN外延层低温键合等关键技术,目前已实现的界面热阻优于40m^2K/GW,这一结果距离国外报道的介质键合最好水平还有提升空间[13]。图2是完成工艺的金刚石GaN HEMT与现有SiC衬底GaN HEMT结构示意图。

图 1 金刚石 GaN HEMT 异质集成器件工艺流程示意图

图 2 (a) SiC 衬 底 GaN HEMT 与 (b) 金 刚 石 衬 底 GaN HEMT 结构示意图

基于该工艺研制出典型栅宽金刚石GaN HEMT,8×50μm栅宽、20μm栅间距的0.25μm栅长的GaN HEMT,在10GHz负载牵引,80V工作下,输出功率密度15.36W/mm,功率增益14.95dB,功率附加效率(PAE)55.3%。

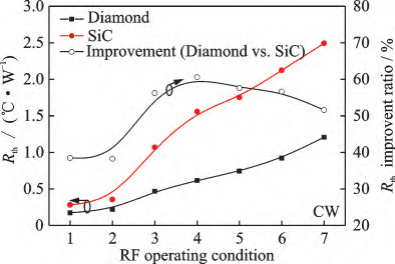

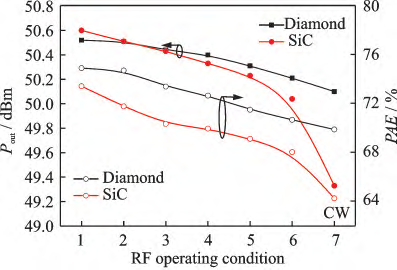

基于该工艺研制出22.4mm栅宽管芯,管芯栅栅间距为53μm,单指栅宽为350μm,芯片尺寸4.25mm×1.00mm,两种器件的装配和电路匹配一致,射频工作条件从窄脉宽到连续波(CW),脉宽/占空比分别为50μs/10%、100μs/10%、1ms/10%、3ms/10%、3ms/30%、5ms/50%以及CW共7种条件,工作频率1.5GHz,工作电压28V,输入功率40dBm。图3给出了金刚石衬底GaN HEMT与SiC衬底GaN HEMT两种工艺22.4mm栅宽器件在不同工作状态下热阻变化情况,可以看出两种工艺器件热阻(Rth)从窄脉宽到连续波均增大7~9倍。但相对于SiC衬底GaN HEMT器件,金刚石GaN HEMT热阻明显改善,在器件工作脉宽超过1ms的高热耗下工作时,热阻下降幅度超过50%,验证了金刚石衬底GaN HEMT热阻改善效果。

图3两种工艺22.4 mm栅宽器件在不同工作状态下热阻变化情况 图4给出了两种器件在上述的窄脉宽到连续波不同工作条件下输出功率和功率附加效率的对比(输入功率均为40dBm),可以看出金刚石衬底GaN HEMT器件输出功率(Pout)、PAE分别下降0.42dB和5.0个百分点,对应SiC衬底GaN HEMT器件Pout、PAE分别下降1.27dB、9.2个百分点,连续波工作条件下金刚石衬底GaN HEMT器件Pout、PAE相当于SiC衬底GaN HEMT器件分别改善0.77dB和5.6个百分点,这一结果也进一步展示了金刚石GaN HEMT的散热效果。

单位毫米栅宽器件输出功率密度是表征器件性能水平的关键指标,不仅决定器件和电路的输出功率能力,同时还对器件和电路的工作带宽、效率等性能有重要影响。更大的输出功率、更高的工作频率、更高的效率是固态微波功率器件技术不懈努力的目标。金刚石GaN异质集成可有效改善现有SiC衬底GaN HEMT的散热问题,结合GaN HEMT的AlGaN/GaN异质结材料生长、管芯结构设计及关键工艺的优化,提高GaN HEMT高压工作的可靠性,可推进GaN HEMT器件向更高输出功率密度的技术发展,为超大功率器件以及更高性能电路的实现提供工艺保证。另外热管理技术也是固态微波功率器件研究永恒的主题,金刚石GaN异质集成将为长脉宽、高占空比、连续波、大功率等高热耗应用电子信息系统的散热和可靠性提升提供强有力的技术支撑。

图 4 两种工艺 22.4 mm 栅宽器件在不同工作状态下输出功率和效率变化情况

介质键合晶体管级异质集成技术在射频多功能电路的研制中有多种应用,典型的如GaAs低噪声pHEMT与GaN HEMT功率放大电路单片集成实现的射频前端电路,可充分发挥GaAs低噪声pHEMT低噪声、低功耗以及GaNHEMT高功率各自性能优势,解决单一GaN HEMT工艺前端电路存在的功耗大等难题。

2.2金属键合晶体管级异质集成工艺

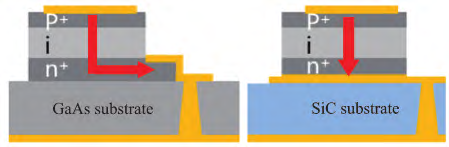

限幅器是射频前端电路的一个重要功能电路,耐功率能力、限幅电平以及插入损耗是限幅器相互制约的关键性能指标。高耐功率能力要求PIN管芯具有较小的导通电阻,这需要增大结面积实现,结面积增大将引入较大的结电容,导致限幅电平和插入损耗增加,同时还将影响电路的工作带宽。系统应用的限幅器多为单片形式,目前的限幅器电路主要采用GaAs衬底的GaAs PIN通过准平面结构实现。基于GaAs PIN与高导热的SiC衬底金属键合的异质集成限幅器,可恢复GaAs PIN的纵向结构,同时利用SiC的高导热性,提高现有GaAs PIN限幅器性能水平。

GaAs PIN与SiC的异质集成工艺与金刚石GaN HEMT基本一致,主要不同点在于键合前GaAs PIN需完成阴极欧姆接触工艺,SiC衬底上需制备好金属电极,GaAs PIN与SiC衬底通过金属直接键合,两者的套刻误差可控制在1μm以内。图5为常规GaAs衬底PIN与异质集成SiC衬底GaAsPIN结构示意图。

图 5 常规GaAs衬底PIN与异质集成SiC衬底GaAs PIN结构示意图

针对研制的两种PIN建立了器件模型,表2给出了两种不同结构PIN的导通电阻、结电容以及两者乘积的比较,两种管芯的阳极尺寸一致,可以看出异质集成器件导通电阻明显降低,结电容也有一定程度下降,这均为限幅器插损、限幅电平、耐功率能力等性能提升奠定了基础。

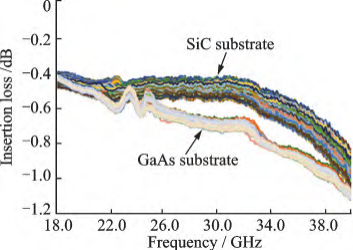

对采用该工艺研制的18~40GHz限幅电路进行了微波性能测试。图6给出了两种工艺电路插入损耗测试结果的分布情况,可以看出与常规GaAs衬底GaAs PIN限幅电路相比,GaAs PIN与SiC衬底异质集成电路损耗小约0.2dB。限幅电平和耐功率能力测试结果表明两种电路限幅电平基本一致,异质集成工艺电路耐功率能力提高3dB以上。

图 6 两种工艺 18~40 GHz 限幅器电路插入损耗在片测试结果比较

金属键合晶体管级异质集成技术在射频多功能电路的研制中有多种应用,典型的如限幅低噪声放大器电路,相对于通过外延依次生长低噪声pHEMT和PIN两种异质结材料实现的限幅低噪声放大电路,采用金属键合异质集成技术,GaAsPIN可采用MOCVD技术生长,外延片成本可降低,细线条的GaAs pHEMT单独加工,工艺成品率可提高,在实现限幅器性能提升的同时可有效降低芯片生产成本。另外在SiC衬底GaN上采用金属键合集成GaAs PIN和采用介质键合集成GaAs pHEMT,可实现高性能的射频前端电路,凸显晶体管异质集成技术在多功能电路研制方面的技术优势。

03 结论

后摩尔时代单一半导体微波器件技术的发展受到限制,通过不同技术途径异类集成各具特色的半导体器件及半导体衬底实现器件或电路性能与功能提升成为后摩尔时代半导体微波器件技术发展的主流。介绍了基于外延层转移工艺的晶体管级异质集成技术,展示了开发的分别适用于平面和纵向两类不同结构器件的介质键合和金属键合两套工艺,采用这两套工艺分别研制出金刚石衬底GaN HEMT微波功率器件和SiC衬底GaAs PIN限幅器电路。测试结果表明,与常规的SiC衬底GaN HEMT相比,金刚石GaN HEMT器件散热特性明显改善,高热耗工作下器件热阻减小超过50%,器件连续波工作输出功率和功率附加效率分别提高0.77dB和5.6个百分点。与常规的GaAs衬底GaAs PIN限幅器相比,研制的18~40GHz SiC衬底GaAs PIN限幅器电路限幅电平基本一致、插入损耗改善约0.2dB、耐功率能力提高3dB以上,研制结果显示出外延层转移晶体管级异质集成技术广阔的应用前景。

04 文章信息 文章题目:晶体管级异质集成技术及其典型应用 作者与单位:陈堂胜1,2, 戴家赟1,2,吴立枢1,2,孔月婵1,2,周书同1,2,齐志央1,钟世昌1,2,凌志健1 1 南京电子器件研究所,南京;2 固态微波器件与电路全国重点实验室,南京; 审核编辑:黄飞

-

在特殊类型晶体管的时候如何分析?2024-01-21 8643

-

晶体管和集成块的识别2011-05-21 8294

-

晶体管参数测量技术报告2012-08-02 2773

-

异质结双极晶体管2012-08-20 2493

-

如何加速晶体管的水平输出级2014-09-22 2577

-

概述晶体管2019-05-05 2830

-

什么是GaN透明晶体管?2020-11-27 2910

-

什么是晶体管 晶体管的分类及主要参数2023-02-03 2563

-

什么是达林顿晶体管?2023-02-16 2091

-

氮化镓功率晶体管与Si SJMOS和SiC MOS晶体管对分分析哪个好?2023-02-27 14205

-

不同类型的晶体管及其功能2023-08-02 4156

-

单级晶体管放大电路故障诊断分析方法2010-04-24 1182

-

大功率晶体管驱动电路的设计及其应用2009-07-09 4718

-

异质结双极晶体管,异质结双极晶体管是什么意思2010-03-05 5770

-

芯片上如何集成晶体管 晶体管的结构特点有哪些2023-02-19 6233

全部0条评论

快来发表一下你的评论吧 !