构建高性能计算芯片

描述

本文编译自:Semiengineering

全球领先的超大规模云数据中心公司——Amazon, Google, Meta, Microsoft, Oracle, Akamai ——正在推出专门针对云计算的异构多核架构,对整个芯片行业的高性能 CPU 开发产生了影响。

这些芯片都不太可能进行商业销售。它们针对特定的数据类型和工作负载进行了优化,设计预算庞大,但可以通过提高性能和降低功耗来实现合理化。目标是在更小的面积上容纳更多的计算能力,同时降低冷却成本,而实现这一目标的最佳途径就是采用定制化架构、紧密集成的微架构和精心设计的数据流。

这一趋势始于近十年前,当时 AMD 开始采用异构架构和加速处理单元,取代了过去的同质多核 CPU 模式,但起步缓慢。此后,异构架构开始兴起,紧随为移动消费设备设计的脚步,这些设备需要处理非常紧凑的占地面积以及严格的功耗和散热要求。

Quadric营销副总裁 Steve Roddy 表示:“英特尔等行业巨头的单片芯片几乎在每个产品代码中都配备了 AI NPU。” “当然,人工智能先驱 NVIDIA 长期以来一直在其大获成功的数据中心产品中混合使用 CPU、CUDA内核和Tensor内核。未来几年向 chiplet 的转变将彻底巩固这一过渡,因为指定 chiplet 组合的系统购买者可以挑选为相关设计插座量身定制的计算和互连类型。"

这很大程度上归因于物理学和由此产生的经济学。随着扩展优势的缩小,以及先进封装技术的成熟 --它允许在设计中添加更多的定制功能,而过去这些功能受限于掩膜尺寸--每瓦特和每美元性能的竞争已进入白热化阶段。

"西门子 EDA IC 部门市场总监 Neil Hand 说:"如今,每个人都在构建自己的架构,尤其是数据中心企业,而处理器架构很大程度上取决于工作负载的情况。"与此同时,这些开发人员也在询问加速的最佳途径是什么,因为有很多方法可以做到这一点。你可以选择使用具有多个内核的并行路线,这在某些情况下行不通,但在另一些情况下却很有效。与此同时,应用对内存带宽的限制越来越大,因此你会发现一些高性能计算公司开始把所有精力都花在内存控制器上。还有一些公司会说:'这实际上是一个分解问题,我们要走加速器路线,拥有独立的内核。'但我不认为存在一刀切的做法。"

Roddy 指出,这些新型超级芯片内的 CPU 内核仍然遵循高性能 CPU 设计的久经考验的原则——快速、deep pipelines,在追踪指针方面极其有效——但这不再是设计团队的唯一关注点。 “这些大型 CPU 现在与其他可编程引擎共享空间——GPU 和通用可编程 NPU,可加速人工智能工作负载,”他说。 “与大众消费设备中高度专业化的 SoC 的一个显着区别是,避免使用硬连线逻辑块(加速器)来执行人工智能工作负载中的视频转码或矩阵加速等任务。为数据中心设计的设备需要保持可编程性,以响应各种工作负载,而不仅仅是消费类设备中的单一已知功能。”

然而,所有这些都需要更多的分析,设计届正在继续推动流程中的更多步骤。 “无论是因为工具,还是通过仿真或虚拟原型,你都拥有了了解数据的工具。”Hand说。 “此外,该行业已经发展壮大,其专业化程度足以证明所花费用的合理性。第一部分是为了降低制造新硬件的风险,因为你有工具来了解情况,你不必为了安全而制造'一刀切'的产品。现在,市场已经开始分化,它的重要性足以让你花钱去做。此外,现在也有了这样做的方法。现在,通过生态系统、技术和其他一切因素的综合作用,竞争变得容易多了。对于高性能计算公司来说,最初的目标是:'我们只需获得一个良好的平台,让我们可以按照自己的方式对其进行维度化,然后再放入一些加速器。所以我们开始看到人工智能加速器和视频加速器,然后一些更深奥的公司开始追求机器学习。这意味着什么?这意味着他们需要非常高的 MAC 性能。他们会将处理器架构聚焦于此,这就是他们的差异化之道。"

再加上RISC-V 和可重复使用的芯粒和硬 IP,架构开始看起来与几年前大为不同。"如果你看看现在的数据中心和数据中心中的整个软件堆栈,在堆栈中添加一些东西并不像以前那样困难,你必须重建整个数据中心。"如今变得重要的是进行系统级分析的能力。应用的系统级协同设计已变得非常重要,而且由于高性能计算已不再像以前那样容易获得。这是一个带轮子的数据中心。

许多人认为,应该开发新的架构,以克服几代 CPU 所面临的内存挑战。"Fraunhofer IIS 自适应系统工程部高效电子学部门主管 Andy Heinig 说:"对 AI/ML 的需求将加速开发新的特定应用架构的进程。"传统的 CPU 如果能提供更好的内存接口来解决内存问题,就能成为这场革命的一部分。如果 CPU 能够提供这种新的内存架构,那么 AI/ML 加速器就能与 CPU 一起成为数据中心的最佳解决方案。然后,CPU 负责需要灵活性的经典任务,而加速器则为非常具体的任务提供最佳性能。"

例如,Arm 直接与多个超大规模企业合作开发基于 Neoverse 的计算解决方案,以实现高性能、定制灵活性以及强大的软件和硬件生态系统。通过这种方式已生产出了公开发布的芯片,如 AWS Graviton 和 Nitro 处理器、谷歌的 Mt. Evans DPU、微软 Azure 的 Cobalt 100、NVIDIA 的 Grace CPU Superchip 和阿里巴巴的倚天 710。

“我们从这些和其他设计合作伙伴那里学到了很多东西,” Arm基础设施业务线产品管理高级总监 Brian Jeff 说道。 “我们塑造高性能 CPU 和平台开发的主要方式之一是更深入地了解基础设施工作负载,从而实现特定的架构和微架构增强,尤其是 CPU 管线的前端和 CMN 网状结构。"

但捕获该工作负载并为其开发芯片架构并不总是那么简单。对于人工智能训练和推理来说尤其如此,因为它们可能会随着算法的变化而变化。

"Synopsys公司接口IP首席产品经理Priyank Shukla表示:"目前正在训练不同的模型,例如Meta公司公开的Llama模型和Chat GPT模型。"所有这些模型都有一个模式和一定数量的参数。以 GPT-3 为例,它有 1,750 亿个参数。每个参数的宽度为 2 字节,即 16 位。你需要在 2 个字节中存储这么多信息--1750 亿个参数,相当于 3500 亿字节的内存。该内存需要存储在共享该模型的所有加速器中,而该模型需要放置在加速器的结构中,参数需要放置在与该加速器相关的内存中。因此,你需要一个能接收更大模型并对其进行处理的结构。你可以以不同的方式实现该模型,即实现该算法的方式。有些工作可以串行方式进行,有些工作可以并行方式进行。以串行方式进行的工作需要与高速缓存保持一致,并将延迟降到最低。这种以串行方式进行的工作将在一个机架内进行分工,以便将延迟降到最低。以并行方式进行的工作将通过扩展网络在不同机架之间进行分配。我们看到系统人员正在创建这一模型和算法,并在定制硬件中加以实现。

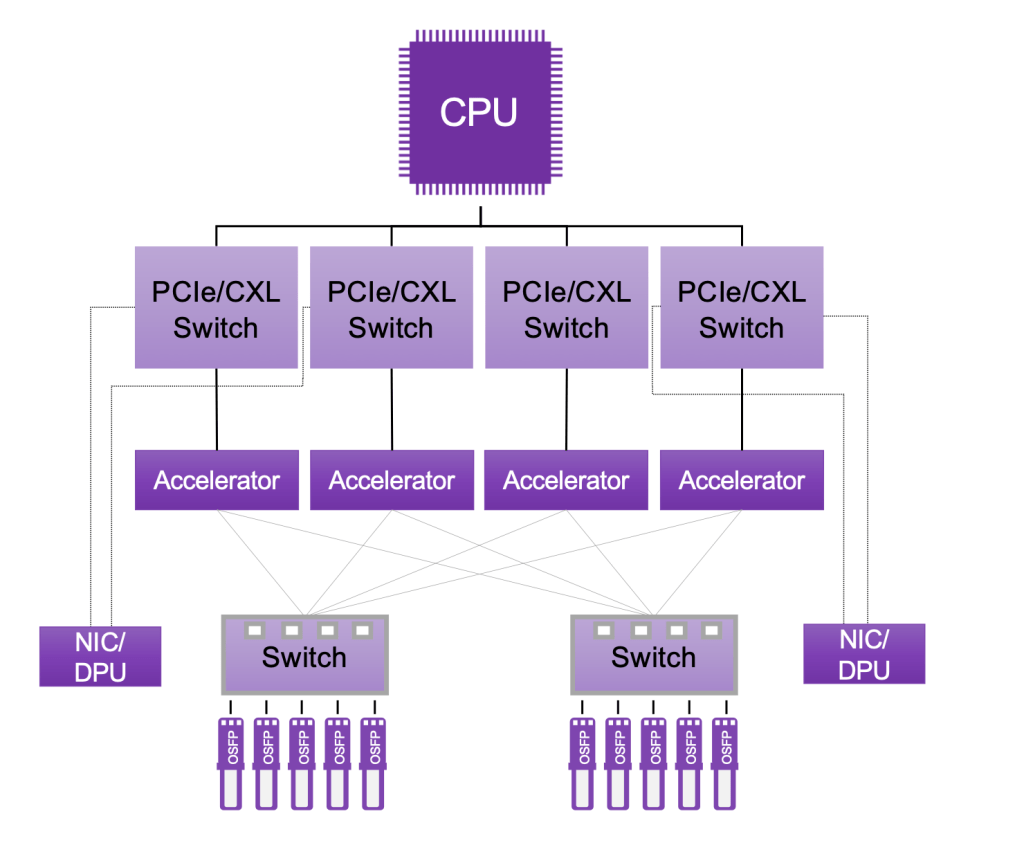

图 1:机器学习优化的服务器机架。来源:新思科技

组装各种处理元件并非易事。 Synopsys ASIP 工具产品经理 Patrick Verbist 表示:“它们是异构多核架构,通常是通用 CPU 和 GPU 的组合,具体取决于公司类型,因为他们偏爱其中之一。” 。 “还有具有固定功能的 RTL 加速器,它们混合在这些异构多核架构中。这些加速器运行的应用程序负载类型通常包括数据操作、矩阵乘法引擎、激活函数、参数压缩/解压缩、图的权重等。但所有这些事情之间的一个共同点与大规模的运营有关。通常,这些计算是在标准或自定义数据类型上完成的。许多处理架构通常都支持 Int 16,但如果您只需处理 16 位数据,您就不想浪费 32 位数据路径中的 16 位。你必须定制它。因此,加速器不仅需要运行浮点 32 数据类型,还需要支持 int 8 和/或 int 16,可能是半精度 float、自定义 int 或自定义 float 类型的数据类型,并且功能单元(运算符)通常是向量加法器、向量乘法器、加法器树和激活函数的组合。这些激活函数通常是超越函数,例如指数或双曲函数、平方根、大规模除法,但是是矢量化的并且具有单周期吞吐量要求,因为每个周期,您都希望对这些东西开始新的操作。对于此类加速器,在异构性的影响下,我们看到许多客户使用 ASIP(特定于应用程序的指令处理器)作为该异构空间中的块之一。 ASIP 允许您自定义运算符,因此数据路径和指令集仅以比常规 DSP 更有效的方式执行有限的操作集。”

DSP 通常不会被执行,它的用途太通用了。另一方面,固定功能 RTL 可能不够灵活,这就产生了这样的空间:“是的,我们需要比固定功能 RTL 更灵活、但比通用 DSP 不太灵活的东西。”这就是 ASIP 发挥作用的地方。如果你看看 GPU,你会发现 GPU 在某种程度上也是通用的。它必须支持各种工作负载,但不是所有工作负载。这就是 ASIP 发挥作用的地方,以支持灵活性和可编程性。您需要这种灵活性来支持一系列计算算法,以适应不断变化的软件或 AI 图形要求,以及 AI 算法本身不断变化的要求。”

西门子的 Hand 认为计算工作量是一项艰巨的挑战。“为了解决这个问题,垂直整合的公司正在以这种方式投资高性能计算,因为高性能计算与人工智能没有太大不同,你只能处理你看到的数据模式,” Hand 说。 “如果你是亚马逊或微软这样的公司,那么你就可以获得大量的跟踪数据,而无需窥探任何数据,并且你知道机器的瓶颈在哪里。你可以使用这些信息并说,‘我们看到我们获得了内存带宽,我们必须对此采取一些措施,或者这是一个网络带宽问题,或者,这是一个人工智能吞吐量问题,而我们正陷入这些领域.'这实际上与边缘发生的挑战没有什么不同。边缘的目标是不同的,我们经常看着它说,‘我能摆脱什么?我不需要什么?或者,“我可以在哪里缩小功率范围?”而在数据中心,您会问,‘我如何才能推送更多数据,以及如何以不烧坏设备的方式做到这一点?随着设备变得越来越大,我怎样才能以可扩展的方式做到这一点?”

Hand 相信向多芯片的转变将推动许多有趣的发展,并且已经被 AMD 和 Nvidia 等公司所采用。 “现在您可以开始为这些高性能计算应用程序提供一些有趣的即插即用组件,在很大程度上,您可以开始说,‘我用于该应用程序的互连芯片是什么?该应用程序的处理模具是什么?它在构建标准计算机之间提供了一个中间立场,无需进行太多更改。我能做些什么?我可以放入不同的进程、不同的网卡、不同的 DIMM。作为云提供商,我可以做的事情是有限的,以实现差异化。另一方面,像 Microsoft 和 Azure 这样的大型云提供商会说,‘我可以构建自己的完整 SOC,做任何我喜欢做的事情。我可以去建造它。但你现在可以得到这个中等基础,比方说,你决定生物计算数据中心有市场,有足够多的人进入这个领域,你可以赚一些钱。您可以组装 3D IC 并使其在该环境中工作吗?看看会发生什么将会很有趣,因为这将降低进入门槛。我们已经看到它被苹果、英特尔、AMD 和 Nvidia 等公司使用,作为一种在无需测试巨大芯片的情况下获得更快旋转速度和更多品种的方法,我认为这将产生更大的影响比人们意识到的高性能计算。当你开始将它们与环境的完整数字孪生之类的东西结合起来时,你可以开始了解环境中的工作负载,了解瓶颈,然后尝试不同的分区,然后下推。”

Arm 的 Jeff 还发现数据中心芯片架构正在发生变化,以适应 AI/ML 功能。 “CPU 上的推理非常重要,我们看到我们的合作伙伴利用我们的 SVE 管道、矩阵数学增强功能和数据类型来运行推理。我们还看到人工智能加速器通过高速相干接口的紧密耦合开始发挥作用,并且 DPU 正在扩展其带宽和智能以将节点连接在一起。”

多模块不可避免

芯片行业清楚地意识到,对于许多计算密集型应用来说,单芯片解决方案已变得不切实际。过去十年的一个大问题是,多芯片解决方案的转变何时才会成为主流。 Synopsys 研发总监 Sutirtha Kabir 表示:“整个行业正处于一个拐点,你无法再回避这个问题了。” “我们在后台谈论摩尔定律和‘SysMoore’,但设计人员必须在 CPU 和 GPU 中添加更多功能,但由于光罩尺寸限制、产量限制以及所有这些限制,他们根本无法做到这一点芯片。多芯片芯片在这里是不可避免的,这带来了一些有趣的考虑。第一,拿一张纸并将其折叠。这基本上就是多芯片的一个例子。你拿一个芯片,把它折叠起来,如果你能巧妙地设计它,你可以认为你实际上可以大大缩短时序,而不是有很长的时序路径。如果你从顶部芯片到底部芯片,你所经历的可能只是芯片中的少量布线,但它们大多是凸块到凸块或键合到凸块。”

多芯片设计所面临的挑战包括:要弄清楚有多少条路径需要同步、时序是应该放在两个芯片之间还是应该单独关闭、L1 是应该放在顶部芯片还是底部芯片上--以及是否可以增加 L4。

Kabir 解释说:"从三维角度来看,现在的楼层规划变得非常有趣。"你可以把一栋单层房屋改建成三层或四层。但随之而来的还有其他设计挑战。你不能再忽视散热问题了。散热曾经是印刷电路板(PCB)的事情,而现在系统设计师们认为这些芯片非常热。黄仁勋最近在 SNUG 上说,你把室温的水从一端放进去,另一端就会变成按摩浴缸的温度。他是在开玩笑,但事实是,从温度的角度来看,这些芯片的温度很高,如果你在平面规划时不考虑到这一点,你的处理器就会被烧毁。这意味着你必须更早地开始这样做。在三维平面规划方面,当涉及到工作负载时,你如何知道自己已经分析了多芯片的不同工作负载,并确保即使在没有网表的情况下也能考虑到红外、热和时序等关键影响?我们称之为零网表阶段。这些考虑因素都变得非常有趣,因为你再也无法避免做多芯片,所以从代工厂的角度、从 EDA 的角度,这些都是生态系统的前沿和中心,而设计人员则处于中间位置。

与数据中心芯片的热问题相关的是低功耗设计

"这些数据中心耗电量巨大,"Ansys 产品营销总监 Marc Swinnen 说。"我当时正在旧金山参加 ISSCC,我们的展台就在英伟达公司旁边,英伟达公司正在展示其人工智能训练箱--一个装有八个芯片、大量风扇和散热片的大箱子。我们问它的耗电量有多大,他们说:'哦,最高时有 1 万瓦,但平均也有 6000 瓦。'功率真是越来越疯狂了。

Arm公司的Jeff也认为,应对数据中心芯片新挑战的最佳方法是采用完整的系统方法,包括指令集架构、软件生态系统和特定优化、CPU微架构、结构、系统内存管理和中断控制,以及封装内和芯片外I/O。"完整的系统方法使我们能够与合作伙伴合作,根据现代工作负载和工艺节点定制 SoC 设计,同时利用基于chiplet的设计方法"。

这种定制芯片设计方法使数据中心运营商能够优化其电力成本和计算效率。"Jeff 说:"我们 Neoverse N 系列的高效率使每个插槽的内核数从 128c 到 192c 甚至更高。"这些相同的 N 系列产品可以在更小的空间内扩展到 DPU 和 6g L2 设计以及边缘服务器。我们的 V 系列产品面向云计算,具有更高的每线程性能和更高的矢量性能(用于人工智能推理和视频转码等工作负载),同时还能提供高效率。加速器附件的广泛选择使我们的合作伙伴能够在为其工作负载量身定制的 SoC 中将定制处理和云原生计算正确地结合在一起。"

结论

鉴于高性能计算的演进特性,特别是由于数据中心的优化方式涉及多个不同方面,所有这一切的最终结果几乎都无法预测。" Hand表示:"在网络应用爆发之初,人们开始在数据中心内进行南北向和东西向路由选择,这改变了所有的网络交换架构,因为这是一大瓶颈。"这导致了对数据中心的整体重新思考。类似的事情也发生在内存方面,当你开始集成光学技术和一些更智能的内存时,你会发现这将会是非常有趣的事情。

Hand 提到了几年前的一次英特尔开发者大会,当时该公司解释了如何利用硅光子学中的表面发射光学技术将内存与数据中心机架中的存储分离开来。"他说:"他们有一个统一的内存结构,可以在服务器之间共享,也可以从不同的服务器分配内存。"因此,数据中心的拓扑结构开始变得非常有趣。即使在机架中,你看英伟达的人工智能系统结构也不像传统的服务器机架。最大的变化是,人们可以看到它,如果有市场,你就可以构建它。我们一直认为,架构的关键在于核心是否快速。我们从'内核快不快'变成了'我有足够的内核吗'。但问题远不止于此。一旦你开始打破冯-诺依曼架构,开始使用不同的内存流,开始关注内存内计算,它就会变得非常酷。然后你会说,'高性能计算到底意味着什么?

本文编译自:Semiengineering 特别鸣谢!

-

纵行科技发布了全新的纯国产芯片ZTG1826A,这款ZETA芯片高性能,低功耗,低成本,欢迎来撩纵行科技 2022-11-16

-

FPGA构建高性能DSP2011-02-17 3286

-

高性能计算机的发展历史是怎样的?2019-09-10 4454

-

HPC高性能计算知识介绍2020-05-29 2789

-

高性能计算软件具有哪些缺陷?2021-08-30 1610

-

基于ZU3EG的低功耗高性能嵌入式AI高性能计算模组2021-12-14 2943

-

什么是高性能计算2009-05-24 5292

-

英特尔将为高性能计算研制“超级芯片”2012-04-02 1286

-

高性能计算发展与应用2016-03-24 604

-

云计算与高性能计算的区别及联系2021-06-26 3944

-

鲲鹏Validated认证帮助密码模块构建全面的高性能密码计算服务2022-10-10 3672

-

芯品# 高性能计算芯片2024-06-27 8354

-

云计算厂家使用WDS分布式存储构建其高性能超融合一体机2024-09-23 1070

-

高性能计算面临的芯片挑战2025-05-27 1231

-

使用树莓派构建 Slurm 高性能计算集群:分步指南!2025-06-17 1953

全部0条评论

快来发表一下你的评论吧 !