基于FPGA设计的BRAM内部结构

可编程逻辑

1395人已加入

描述

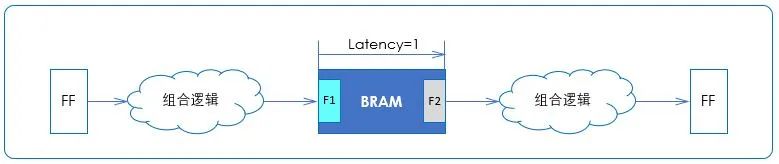

在FPGA设计中,我们往往会遇到如下图所示路径。图中FF、F1和F2均为触发器,其中FF为Slice中的触发器,F1和F2为BRAM内部触发器。在高速时钟频率下,这种路径的最大缺陷是未使用F2,使得BRAM从输入到输出的Latency为1。为什么F2对BRAM时序性能如此重要?这就要从BRAM内部结构说起。

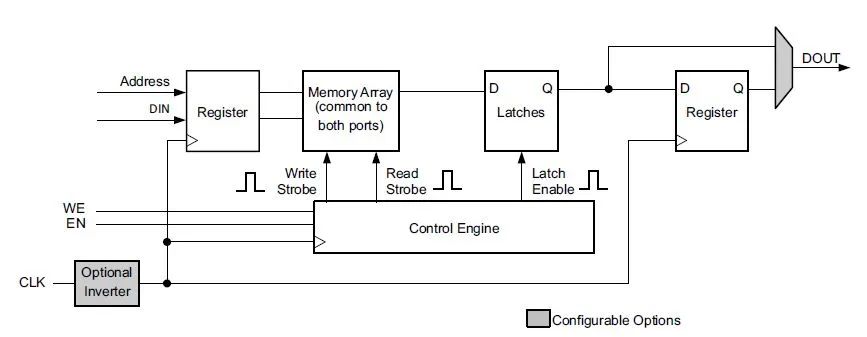

BRAM内部结构如下图所示,无论是7系列FPGA,还是UltraScale/UltraScale+,亦或是Versal,BRAM内部结构是一致的。该结构呈现如下几个特征:(1)所有输入信号(除时钟外)无论是数据信号还是控制信号,进入BRAM内部之后都会先过一级流水寄存器(2)BRAM的输出数据信号可以从图中的锁存器(Latch)输出,也可以从末级触发器输出(3)输入时钟可以是上升沿采样,也可以是下降沿采样,默认上升沿采样。采样沿的转换在BRAM内部完成。基于这些特征,我们可以得出结论:BRAM从输入到到输出Latency最小为1,最大为2。

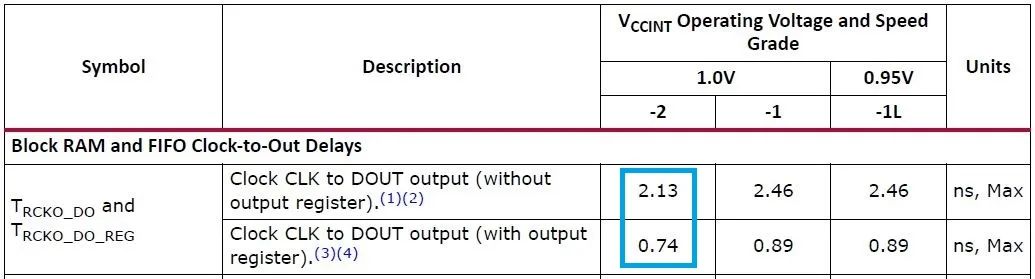

再看末级触发器对BRAM时序性能的影响,下图依次展示了7系列FPGA、UltraScale+和Versal芯片在未使用和使用末级触发器两种情形下时钟到输出的延迟。以-2芯片为例,可以看到7系列由2.13降至0.74,降幅达65.3%;UltraScale+从1.02降至0.29,降幅达71.5%;Versal芯片从0.797降至0.234,降幅达70.6%。以400M时钟为例,对应时钟周期为2.5ns,延迟从0.797降至0.234,减小了0.563,对应时钟周期的22.5%,这还是很可观的。

审核编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

MOSFET和IGBT内部结构与应用2023-11-03 2607

-

FPGA的BRAM资源使用优化策略2023-08-30 5743

-

fpga内部主要结构及其功能分析(Kintex-7FPGA内部结构)2023-08-24 3556

-

交叉导轨的内部结构2023-08-16 2462

-

FPGA设计中BRAM的知识科普2023-08-15 8270

-

FPGA内部结构的详细介绍2020-09-17 1401

-

信号在fpga内部结构上运行的最大频率是?2019-01-30 4404

-

元件的内部结构2017-03-04 1411

-

学fpga的内部结构和各接口实验怎么学2014-05-10 2754

-

8051内部结构2013-12-17 3726

-

伺服电机内部结构2010-02-25 5053

-

蓄电池内部结构2009-11-16 5611

-

MAX782内部结构框图2009-11-14 1130

-

芯片封装内部结构2008-06-11 91841

全部0条评论

快来发表一下你的评论吧 !