基本DC-DC降压转换器电路设计

电源/新能源

描述

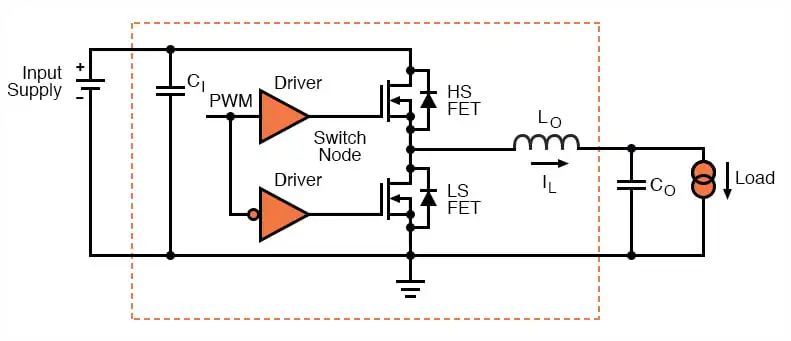

基本 DC-DC 降压转换器电路

在开始之前,我们先回顾一下DC-DC降压转换器的电路:

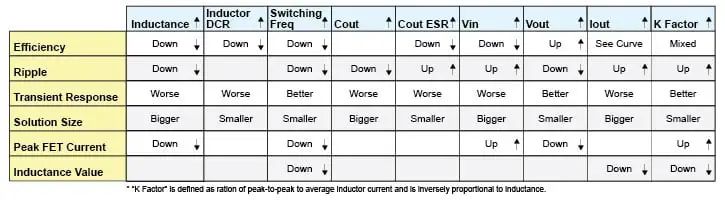

降压转换器中的元件权衡

了解您面临的设计权衡非常重要。

为了帮助您,我开发了降压设计中“什么影响什么”的矩阵:

乔治·比纳的《什么影响什么》。

主要的权衡是电感(与 k 因子成反比,即峰峰值与平均电感电流之比)、输出电容和开关频率的选择,以实现足够的纹波和瞬态响应。

设计人员绝对应该利用稳压器 IC 制造商的设计工具来确定元件值并进行电路仿真。

了解您的电容器

确保电容器在工作频率下具有电容,并了解其自谐振频率在哪里。

陶瓷在宽频率范围内表现良好,但电容相对较低。通常,一种电容器类型无法覆盖整个频率范围,必须并联使用两种类型(例如陶瓷电容器和电解电容器),并且陶瓷电容器更靠近电路。

施加偏置电压后,电容器也会损失大量额定电容。

信任但验证:芯片和组件

在第三方制造的带有微小、未标记元件的 PCB 上,您必须相信电路板填充器安装了正确的元件。确保您的信任没有被放错地方。

如果您已将芯片发送给制造商进行故障分析,请不要等待结果。如今芯片的质量水平非常高,而且芯片不太可能是坏的。该分析也需要一些时间。与此同时,您可能会发现真正的问题。

如果您使用的是数字芯片,请验证您更改的设置实际上已写入芯片中,而不仅仅是写入 GUI 中。

考虑测试和测量

在没有用示波器验证的情况下,不要假设直流电压是稳定的。

测量纹波的过程涉及很多内容,而执行该过程的适当设备非常昂贵。虽然最好使用精美的差分探头,但您也可以使用单端探头 - 只需确保地线非常短并连接到V out旁边。

使用 1x 探针(您可以自己构建)。10 倍探头不具备您所需的灵敏度。

高频尖峰通过电感器的寄生电容耦合到输出。您可能需要减慢上部 MOSFET 的开启速度,以减少底部 MOSFET 的振铃或dv/dt杂散开启,尽管这会降低效率。

分析您的输入电容

输入电容比输出电容更难理解,但可能需要它来满足输入噪声要求并确保您的电路不会缺乏电流。

输入电容器具有较大的纹波电流,在 50% 占空比时达到峰值,产生热量并缩短电容器的使用寿命。确保电流在其规格范围内。当您在 中添加更多并联C时,需要进行一个基本权衡,因为不断降低的 ESR 将导致更高的纹波电流和更多的热量。为了真正降低输入纹波电流,您可能需要串联电感器。

随着占空比越高,从C in汲取的电流也越高,从而导致芯片上的V in压降更多 — 如果V in已经很低,因为您更接近达到较低的V in限制,则这一点变得很重要 — 您可能需要在这些情况下添加C。

提前考虑 PCB 布局

了解电流路径和高电流环路最小化的基础知识。学校教授了很多有关前向电路路径的知识,但对返回路径却一无所知,返回路径显示为完美的接地符号!进行布局,使返回电流可以遵循其自然路径(最小化环路)。

保持电源路径电感较低。通过它们的脉冲电流会产生电压尖峰和辐射 EMI。高功率过孔是可以的,但应该了解它们的特性。

了解电路节点的阻抗水平并相应地保护它们。例如,误差放大器的求和节点具有高阻抗并且对噪声敏感——将其隔离并使其变小。

尊重模拟、数字和电源接地之间的划分,并提供自然的返回路径。星形接地可避免通过与敏感低电平电路共享的接地路径运行大的脉冲电流。

了解(并尊重)你的极限

确保遵守热降额曲线——在高温下,最大电流和功耗总是从“标题”值降低。

确保引脚电压永远不会超出工作规格,无论是引脚对地还是引脚对引脚。例如,在其引脚对地规范内为一个引脚通电,但违反其引脚对引脚规范而对不同引脚进行供电可能会烧毁芯片。

注意控制器芯片的最小/最大可控打开和关闭时间,并确保您的操作不会太接近其限制。

审核编辑:黄飞

-

降压型DC-DC转换器与升压型DC-DC转换器的输出纹波差异2024-04-24 3312

-

DC/DC转换器电路设计的技巧分享2023-12-19 772

-

ADP1821降压DC-DC转换器电路图2023-12-16 3423

-

DC-DC转换器电路图 Boost升压型DC-DC转换器的工作原理2023-09-19 5746

-

DC-DC降压转换器PCB布局的技巧2023-06-19 3272

-

DC-DC降压转换器工作原理! #硬声创作季学习硬声知识 2022-10-30

-

DC-DC降压转换器工作原理!#电路原理学习电子知识 2022-10-20

-

DC-DC转换器和AC-DC转换器的区别及功能2021-11-17 7228

-

非隔离式的DC-DC转换器解析2020-12-09 5650

-

DC-DC降压转换器电路布局与设计和实践2019-07-11 13587

-

电子书:DC-DC 转换器的应用与设计方案2019-03-14 7731

-

DC/DC转换器电路设计的原理和技巧2018-09-29 3888

-

关于DC/DC转换器电路设计的技巧2018-03-27 4067

-

DC-DC转换器2010-03-09 4129

全部0条评论

快来发表一下你的评论吧 !