通过实例,走近PLD

FPGA/ASIC技术

描述

电子发烧友网:PLD设计,相信对很多人而言都不陌生。当然也有对它不是那么了解的人,那么即使你没有深入接触过PLD,我们也可以让你可以在短短的几十分钟内初步学会PLD设计! 通过对本文的学习,你将迅速走进PLD世界。不信吗? 那我们就慢慢往下看。本文主要通过分别采用VHDL、Verilog-HDL和原理图输入方式设计一个简单的三人表决器,并下载到PLD实验板进行仿真、运行。

三人表决器的主要功能介绍:三个人分别拨动开关SW1、SW2、SW3来表达自己的观点(如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方))。表决结果用LED(高电平亮)显示,如果决议通过那么实验板上L2(黄灯)亮;如果不通过那么实验板上L1(红灯)亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮。功能虽然简单,但是大家可以从这个实验中学习到PLD的设计输入,仿真,下载等一系列完整的过程。

本次设计采用的软件:Max plusII 10.2 软件;硬件设施:PC机一台,JX002B型实验板,电源,下载电缆。

软硬件均准备好以后,就可以开始我们的设计了。下面是我们的具体实施过程:

一.采用原理图设计输入三人表决器

我们根据三人表决器的直值表,可以通过卡诺图化简可以得到:

L2=SW1SW2 SW1SW3 SW2SW3

L1=_L2

那么我们可以在MAX plusII中用原理图实现上面的三人表决器

下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过:

(1)打开MAX plusII

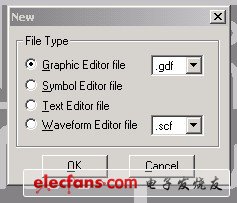

(2)新建一个图形文件:File菜单>new

新建文件时选择Graphic Editor file

点OK

(3)输入设计文件

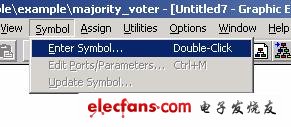

我们现在在图形文件中输入电路,我们这个电路需要AND2、OR3、NOT三个逻辑门电路和输入输出端,你可以

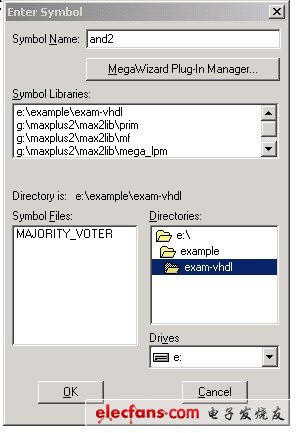

Symbol ->Enter Symbol(或者双击空白处)

弹出窗口:

在Symbol Name中输入and2,点OK

同样可以加入or3、input、output、not

对input、output,鼠标左键双击PIN_NAME,那么PIN_NAME被选中,并且变黑,然后输入你要改的名字,如SW1

【关于“采用原理图设计输入三人表决器”详细部分请参考:PLD设计速成(2)-采用原理图设计三人表决器】

二.采用VHDL设计输入三人表决器

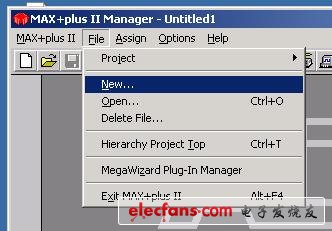

打开MAX plusII,在开始菜单内选择MAX PLUS II 项,开始运行MAX PLUS II(如下图)

你最好把图标放到桌面上,以后直接双击MAX PLUS II图标就可以运行软件了

在MAX PLUSII上点右键,选择发送到->桌面快捷方式(如下图),那么你桌面上就看到MAX PLUS II了。

3.2 新建VHDL文档

(图形和verilog-HDL设计的过程见后面的部分)

FILE->NEW

【关于“采用VHDL设计输入三人表决器”详细部分请参考:PLD设计速成(3)-采用VHDL设计输入三人表决器】

三.采用VerilogHDL输入三人表决器

下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过:

(1)打开MAX plusII

(2)新建

新建一个verilog-HDL文件(Text Editor File类型)

(3)输入设计文件

其中SW12,SW13,SW23为中间变量

module majority_voter(SW1,SW2,SW3,L1,L2);

output L1,L2;

input SW1,SW2,SW3;

and(SW12,SW1,SW2);

and(SW13,SW1,SW3);

and(SW23,SW2,SW3);

or(L2,SW12,SW13,SW23);

//SW12、SW23、SW13是中间变量

not(L1,L2);

endmodule

(4)保存文件

保存为majority_voter.v,注意Automatic Extension选.v

并把文件设为当前工程(同前)

四.波形仿真

此过程主要是用软件来仿真你的设计,看看结果是否符合你的设计要求

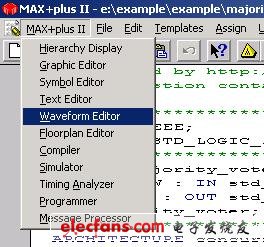

编译好以后,打开波形编辑器,MAX PLUSII->Waveform Editor

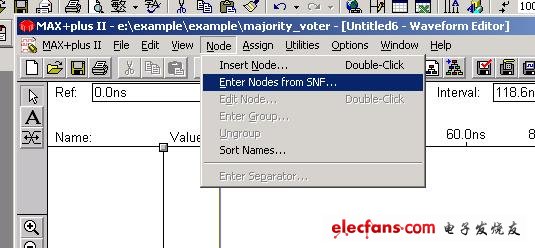

载入端口,Node->Enter Nodes from SNF

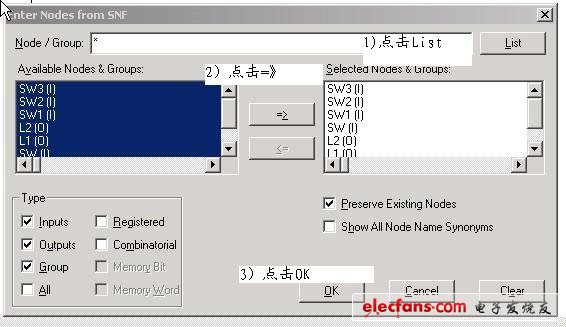

将弹出下面窗口,你按下面步骤操作:

点List,将出现端口列表,你默认是选择全部,你也可以通过左键和Ctrl组合来选择你想要的信号。

点=>将你的信号加入SNF文件中

点OK

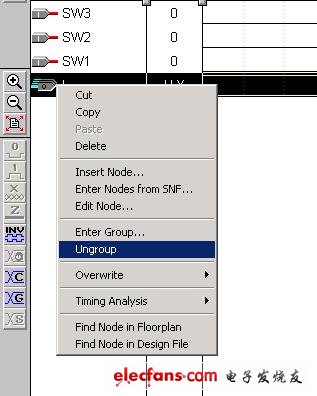

为了方便观察,我们把信号展开

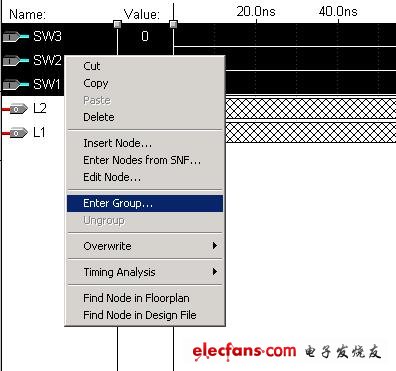

如果需要再次合并可以按住SHIFT键,用鼠标左键选上要合并的信号,再点右键->Enter Group

【关于“波形仿真”详细部分请参考:PLD设计速成(5)-波形仿真】

五.编译和布线

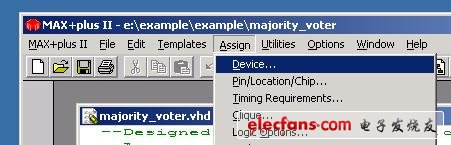

我们先要指定所用芯片的型号,

菜单:Assign->Device

如下图

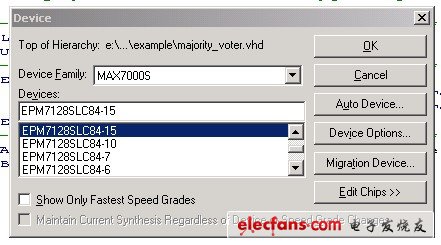

将弹出一窗口

(注意把show only fastest speed grades前的钩去掉,否则看不到EPM7128SLC84-15)

在Debice Family 中选择MAX7000S

DEVICE选择EPM7128SLC84-15

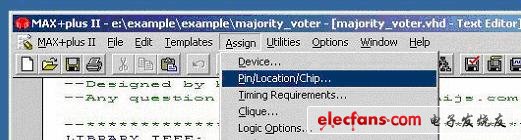

再指定芯片的管脚(也就是把你设计的IO口如L1,L2指定到芯片对应的管脚上如10,9)

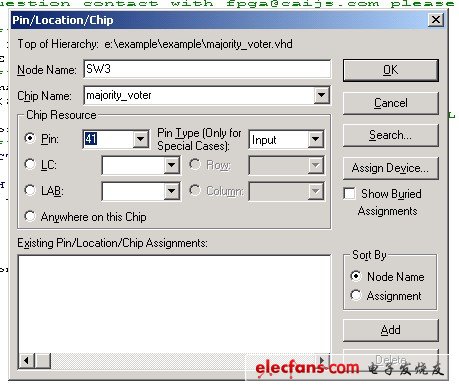

Assign->Pin/Location/Chip(也可以在空白处点右键,选Assign->Pin/Location/Chip)

将弹出下图窗口:

【关于“编译和布线”详细部分请参考:PLD设计速成(6)-编译和布线】

六.安装下载电缆的驱动程序

MAX plusII 软件的驱动设置

在Win98下运行MAX plusII可以自动检测到ByteBlasterMV(ByteBlaster)下载电缆,但在WIN2000、WINXP下无法自动检测到它的存在。如何在WIN2000和WINXP平台下安装使用ByteBlasterMV并口下载电缆呢?

WIN2000

1)在控制面板中选择“添加/删除硬件”

2)选择“添加/排除设备故障”,下一步

3)选择“添加新设备”,下一步

【关于“安装下载电缆的驱动程序”详细部分请参考:PLD设计速成(7)-安装下载电缆的驱动程序】

七.下载验证

( 注意:本次实验采用的JX002B实验板已经将下载电缆的电路都做在了实验板上,所以只需要一根并口延长线即可,实际使用中一般都使用标准的下载电缆(ByteblasterMV、ByteblasterII)和并口相连,下载电缆再和PLD芯片相连)

在下载前,还要进行以下步骤:

A:将JX002B实验板的电源开关拨到OFF(上方)

B:将并口下载电缆母端插到JX002B实验的25针下载口上,并口电缆公端插到电脑的打印口上,参考下面四张图(不可能插错,否则插不上)

并口电缆母端

并口电缆公端

JX002B实验的25针下载口

【关于“下载验证”详细部分请参考:PLD设计速成(8)-下载验证】

关于三人表决器的整个设计、仿真及运行过程就到此结束了。想要了解更多的话,继续关注我们电子发烧友网,更多精彩内容等着你!

-

什么是PLD的定义和应用 PLD与FPGA的区别和联系2025-02-01 6606

-

PLD芯片的工作原理解析2025-01-20 1527

-

PLD/FPGA基本使用问题2024-04-12 911

-

采用PLD实现视频接口设计2019-05-14 2273

-

基于PLD的视频接口2018-12-28 2245

-

PLD的应用2012-11-19 2909

-

关于PLD器件2012-10-30 2285

-

PLD/FPGA的分类和使用有哪些?2012-02-27 5072

-

PLD Programming Using VHDL2012-01-17 691

-

PLD设计方法及步骤2010-09-18 5106

-

PLD练习实例参考2009-10-09 3311

-

PLD练习参考实例2006-05-26 729

全部0条评论

快来发表一下你的评论吧 !