S参数去嵌:在高速电路设计与测试中的精确化探索

描述

背景

在高速电路设计与测试领域,S参数(散射参数)扮演着至关重要的角色。然而,由于实际测试环境中存在的夹具、连接线等非电路元件的影响,直接测量得到的S参数往往无法真实反映电路本身的性能。因此,S参数去嵌技术的出现,为高速电路设计师们提供了一种有效的方法,用于从测量数据中剥离非电路元件的影响,从而获取更为准确的电路性能参数。

原理分析

S参数去嵌技术的核心在于通过数学方法,将被测件(DUT)与测试工具组成的复合系统的S参数进行分解,以提取出被测件本身的S参数。这一过程需要深入了解测试夹具的电气特性,以及其与被测件之间的相互作用。通过精确建模和计算,可以去除夹具对测量结果的影响,得到更为接近真实情况的电路性能参数。

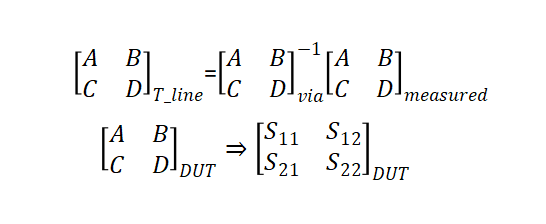

在S参数去嵌的过程中,选择合适的去嵌方法和算法至关重要。目前,常用的去嵌方法包括开路-短路去嵌法、负载线去嵌法等。这些方法的基本原理是通过在测试电路中引入已知特性的元件(如开路、短路或特定负载),从而得到与测试相关的S参数。例如C的拓扑由A和B组成,通过乘以逆矩阵的操作,在C的总体的A参数左边乘以一个过孔的A参数的逆矩阵就可以得到真正的传输线的A参数,最后再转换回S参数。

发展与挑战

在高速电路设计中,S参数去嵌技术的应用范围广泛。无论是对于单个元件的性能评估,还是对于复杂电路系统的优化设计,S参数去嵌都能提供更为准确和可靠的数据支持。通过去嵌处理后的S参数,设计师们可以更加精确地了解电路的性能特性,如传输损耗、反射系数、串扰等,从而进行更为有效的优化和设计。

值得一提的是,随着计算机技术不断发展,基于软件的S参数去嵌工具也日益成熟。这些工具能够自动化地完成去嵌过程,大大提高工作效率和精度。同时,一些先进的去嵌算法和技术的出现,也为S参数去嵌技术的发展注入了新的活力。

然而,尽管S参数去嵌技术在高速电路设计中取得了显著的进展,但仍存在一些挑战和待解决的问题。例如,对于复杂的多端口电路系统,如何准确地进行去嵌处理仍然是一个难题。此外,随着电路工作频率的不断提高,对去嵌技术的精度和速度也提出了更高的要求。

SIDesigner 仿真实例

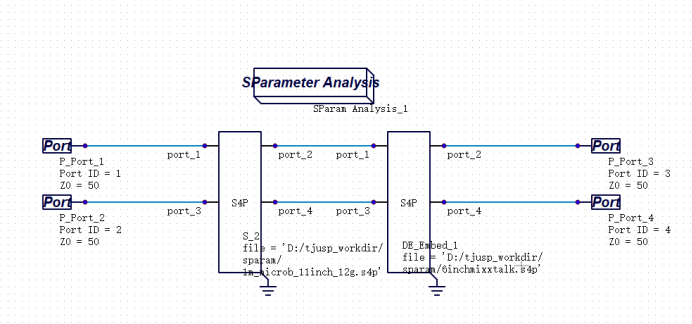

巨霖的SIDesigner提供了DE_Embed器件,可以实现S参数去嵌的功能,能够精确剥离非电路元件影响,为高速电路设计提供准确数据支持,助力电路性能优化与升级。

(S参数去嵌电路图)

审核编辑:刘清

-

模拟示波器在电路设计与调试中的应用2025-03-31 841

-

《典型电子电路设计与测试》阅读体验2025-02-18 1970

-

一个高速电路设计中不可忽略的重要因素—趋肤效应2024-02-29 1973

-

S参数去嵌之DK DF值拟合方案流程与仿真测试拟合过程2023-08-30 7950

-

使用PLTS去嵌方法和探针校准片SLOT校准测试结果对比2022-12-08 13754

-

高速电路设计指南2022-09-13 913

-

模拟电路原理在高速数字电路设计的应用分析《高速数字电路设计教材》2018-09-10 1784

-

华为高速电路设计教材2018-01-22 41075

-

高速DAC自动化测试系统2017-04-18 3385

-

华为《高速数字电路设计教材》2014-09-01 30215

-

Perl语言在电路设计中的应用2012-01-11 2898

-

S参数在射频电路中的问题理解2011-08-24 9024

-

流水线技术在高速数字电路设计中的应用2010-07-17 962

-

高速数字电路设计教程2010-06-23 1217

全部0条评论

快来发表一下你的评论吧 !