芯片设计流程及各步骤使用工具简介

EDA/IC设计

描述

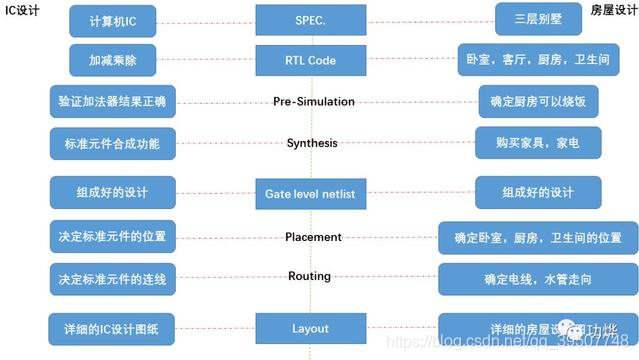

IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。 有人将IC设计和房屋设计做了比较详细的类比:

一、前端设计的主要流程:

1、规格制定 芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。 2、详细设计 Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。 3、HDL编码 使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。 语言输入工具:

Summit 公司的 VisualHDL

Mentor 公司的 Renoir

图形输入工具:

Cadence的composer

viewlogic的viewdraw

4、仿真验证 仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。看设计是否精确地满足了规格中的所有要求。规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。 仿真工具: Verilog HDL:

Mentor公司的Modelsim

Synopsys公司的VCS

Cadence公司的NC-Verilog、Verilog—XL

VHDL:

Mentor公司的Modelsim

Synopsys公司的VSS

Cadence公司的NC-VHDL、Leapfrog

它们均可以对RTL级的代码进行设计验证。逻辑综合之前的该部分仿真称为前仿真,也即功能仿真/行为仿真/逻辑仿真。接下来在版图设计完成之后还要再进行一次仿真,称为后仿真,也即时序仿真 。 5、逻辑综合 仿真验证通过,进行逻辑综合。逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。 逻辑综合工具:

Synopsys的Design Compiler、Behavial Compiler、DC-Expert

Cadence的buildgates、Envisia Ambit

Mentor的Leonardo

6、STA Static Timing Analysis(STA),静态时序分析,这也属于验证范畴,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation)。这个是数字电路基础知识,一个寄存器出现这两个时序违例时,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。 STA工具:

Synopsys的Prime Time。

Cadence的Pearl、Tempus

Mentor的SST Velocity

7、形式验证 这也是验证范畴,它是从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。 形式验证工具:

Synopsys的Formality。

Cadence的LEC、FormalCheck

Mentor的FormalPro

前端设计的流程到这里就结束了。从设计程度上来讲,前端设计的结果就是得到了芯片的门级网表电路。

二、Backend design flow后端设计流程 :

1、DFT Design For Test,可测性设计。芯片内部往往都自带测试电路,DFT的目的就是在设计的时候就考虑将来的测试。DFT的常见方法就是,在设计中插入扫描链,将非扫描单元(如寄存器)变为扫描单元。关于DFT,有些书上有详细介绍,对照图片就好理解一点。 DFT工具:

BSCAN技术– 测试IO pad,主要实现工具是:Mentor的BSDArchit、sysnopsy的BSD Compiler;

MBIST技术– 测试mem,主要实现工具是:Mentor的MBISTArchitect 、Tessent mbist;

ATPG 技术– 测试std-logic,主要实现工具是:产生ATPG使用Mentor的 TestKompress 、synopsys TetraMAX,插入scan chain主要使用synopsys 的DFT compiler。

2、布局规划(FloorPlan) 布局规划就是放置芯片的宏单元模块,在总体上确定各种功能电路的摆放位置,如IP模块,RAM,I/O引脚等等。布局规划能直接影响芯片最终的面积。 布局规划工具:

Synopsys的Astro、Physical Compiler、IC Compiler

Cadence的Encounter、PKS、Silicon Ensemble、Design Planner

3、CTS Clock Tree Synthesis,时钟树综合,简单点说就是时钟的布线。由于时钟信号在数字芯片的全局指挥作用,它的分布应该是对称式的连到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。这也是为什么时钟信号需要单独布线的原因。 CTS工具:

Synopsys的Clock Tree Compiler

Cadence的CT-Gen

4、布线(Place & Route) 布线就是将前端提供的网表(netlist),实现成版图(layout),包括各种标准单元(基本逻辑门电路)之间的走线。比如我们平常听到的0.13um工艺,或者说90nm工艺,实际上就是这里金属布线可以达到的最小宽度,从微观上看就是MOS管的沟道长度。 布线工具:

Synopsys的Astro、Physical Compiler、IC Compiler

Cadence的Encounter、PKS、Silicon Ensemble、Design Planner

5、寄生参数提取 由于导线本身存在的电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射。这些效应会产生信号完整性问题,导致信号电压波动和变化,如果严重就会导致信号失真错误。提取寄生参数进行再次的分析验证,分析信号完整性问题是非常重要的。 寄生参数提取工具:

Synopsys的Star-RCXT

Mentor的Calibre xRC

Cadence的 Assure RCX

6、物理版图验证 对布线完成的版图我们还需要进行功能和时序上的验证,验证项目很多,如:

LVS(Layout Vs Schematic)验证:简单说,就是版图与逻辑综合后的门级电路图的对比验证

DRC(Design Rule Checking):设计规则检查,检查连线间距,连线宽度等是否满足工艺要求

常用的LVS/DRC工具:

Synopsys的Hercules

Cadence的Dracula、diva、assura

Mentor的Calibre

版图验证部分,我们还需要进行时序仿真,也就是之前说的后仿真。这次的仿真不再是简单的功能仿真,而是需要考虑实际的时延等因素。 后仿真工具:和前仿真工具一样。 实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性设计)问题,在此不说了。 物理版图验证完成也就是整个芯片设计阶段完成,下面的就是芯片制造了。物理版图以GDSII的文件格式交给芯片代工厂(称为Foundry)在晶圆硅片上做出实际的电路,再进行封装和测试,就得到了我们实际看见的芯片。

审核编辑:黄飞

-

HarmonyOS开发案例:【生活健康app之编写通用工具类】(5)2024-05-11 1260

-

芯片设计流程及工具2020-02-12 3633

-

ZYNQ芯片开发流程的简介2021-01-26 3944

-

LEDA工具简介2021-07-27 1515

-

STM32CubeIDE软件的基本设计流程和设计步骤是怎样的?2021-12-07 1367

-

电源设计流程简介2009-10-14 453

-

自制便捷式多用工具2009-09-09 578

-

泰科电子多款应用工具简介2010-03-16 1381

-

GetInfo_U盘主控芯片型号识别专用工具2015-11-04 1558

-

Labview2013各工具包的功能简介2015-11-20 1365

-

芯片制造工艺流程步骤2021-12-15 46665

-

芯片制造工艺流程步骤是什么2021-12-22 36225

-

集成电路基本的工艺流程步骤2022-02-01 34461

-

SYNWIT MCU 时钟计算应用工具2023-10-17 1234

-

如何在AMD Vivado™ Design Tool中用工程模式使用DFX流程?2024-04-17 2552

全部0条评论

快来发表一下你的评论吧 !