智能手机主宰CMOS兴衰?!

市场分析

2人已加入

描述

电子发烧友网讯:本文主要阐述了以下内容:2012年半导体国际研讨会开展的非常成功,虽说百家争鸣,但不难看出一点:未来CMOS的发展将取决于智能手机,换句话说,也就是智能手机将会成为CMOS未来发展的最大应用市场。

对于那些未能参加研讨会的人,我为他们总结了自己对本次会议的10大见解。

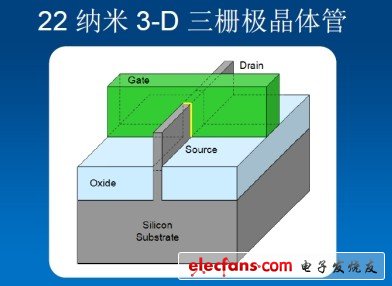

1.Intel的22nm 3D三栅极晶体管是令人印象深刻的工程。在一个300mm的晶片上将近有1万亿个鳍状结构片(大约相当于在每一个CPU上就有30亿个鳍状结构片;每一个鳍状结构片的最大宽度也只有6-9nm,大约只占12-18硅晶格距。)这将是有史以来最小的横向特性图案, 就算是对高容量CMOS制造业而言也是一样的。对22nm的CPU而言,几乎每片鳍状结构都是很重要的。因为如果CPU上任何一个鳍状结构受到损坏,那这个CPU就卖不出去了。我仍相信,拥有三栅极技术能使得Intel在未来5年中领先于同行。

2. Intel目前在三栅极CPU方面有所发展,虽然说产量不高,但是这种情况随着三栅极技术的出现会有所改善的。在ICs行业,性能历来就比成本和功耗更重要。然而,生产商和智能手机芯片设计工程师很快就指出:毫无疑问,移动SOCs中使用了硅技术,并且成为行业领先产品。对于制造英特尔智能手机处理器芯片(如Medfield和Cedar Trail)而言,在产品的成本、功耗和性能方面上,用28 nm的生产远比用32nm的要好得多。生产时,也会有一套丰富的28nmIP核设计过程,比如基带的集成以及在单个28nm集成电路SOC上的应用处理器。我能感受到制造公司和设计公司在回应Intel的大胆声明(“无生产线模式正在逐步崩溃”)时就曾正式指出了这点。

3.在会议之前,逆向工程公司Chipworks曾报道说Intel的鳍状结构外形是一个不规则的四边形形状,并且那一点无论是在会前、会中或会后都是一个关键的主题。专家们都一致认为,理想的FinFETs应该有一个矩形翅片,并且产量问题可能会导致Intel在技术周期结尾时改变鳍状结构的形状(由于日程安排的疏忽,所以导致未能改变)。令人惊讶的是:在Intel的paper Q/A中,当要Chris Auth对鳍状结构加以介绍时, 他给大家的回答是“性能”(降低外部电阻)。最开始,人们对其模型的假设是确定一个与清除的间隔的散热片材料相关的产量问题。普遍的共识是,fin profile(尽管对Intel来说是好事)对手机部件而言将有太多变化。这些手机部件发展不快速,包装也不完整(通常是专门为在最坏的情况下设计的,98%产量都是这样的)。大多数人认为,如果做到14nm,那么Intel就能做成一个矩形鳍状外形了。

4.对一般散装不规则形状的FinFET(具有单个n和pFET工作功能,并且可以通过整晕掺杂设计点来调整阈值电压)进行了讨论。达成了对Intel某些方面的一致认识(这些方面包括:设计出发点、对其工作和应用到市场时总结的经验教训进行的讨论)。主要包括以下几点:

a.由于它会导致关断泄漏,所以对在底部形成的非完全耗尽晶体管、鳍状结构较厚的部分有着高度关注。Intel只报道低于1nA/um的泄漏情况。1nA/um,这对中央处理器来说是一个适当的目标,但智能手机设备需要在10pA/um范围内为总处于首/尾功的率门控装置降低约100倍的泄漏。

b.另外一种降低关断泄漏的方法是添加栅极功函数。然而,想要在3D结构上添加四个或更多功函数并不是一件简单的事(仅是双阈值电压类型的话,就只要2n和2p)。这对移动市场而言,是件非常成本高并且很复杂的事。

c.在设计方面的话,会议集中讨论了bulk-only FinFET方法。这种方法很有可能需要对系统进行再分配。一般而言,电源管理单元、射频甚至模拟电路都需要关断芯片。对低成本移动解决方案而言,单芯片SOC几乎是必需的,因此FinFET应该想中国3G SOC市场一样在大范围内不具备足够的吸引力。

5.仪器专家对FinFET器件的看法有好有坏:

a.“好”:理想的FinFET器件具有卓越的DIBL和顶端设备的摆幅(当顶级设备的阀值低,并且其电流由顶部的鳍状结构决定时,Intel公布的数字是令人印象深刻的);

b.“坏”:真正的FinFET元件子鳍泄漏和高翅片高度控制晶体管的变化,掺杂鳍,鳍的形状和所有的3-D工艺步骤的设备和工艺工程师普遍认同,“理想的FinFET元件是伟大的,但生产FinFET元件失去了一些平面器件相比的优势,当然这取决于如何实施。”

真正的FinFETs在体积上受到sub-fin泄漏和高晶体管变异(由鳍状结构高度控制、鳍状结构参杂度、鳍状结构形状和所有的3D流程步骤导致的)的影响。设备和工艺工程师普遍同意,“理想FinFETs非常棒,但是实际生产中的FinFETs相比平面设备而言却失去绝对优势”,这取决于如何实现。

6.在此次会议上,我们看到了许多关于FinFET器件的研究论文。移动手机领域里的专家们明确表示,“成本将比市场所能承受的要高。”这些技术看起来挺有趣的,比如说为$200的CPU配上 $1,000的服务器芯片,但“我的高端手机芯片只卖20美元”或者是说“普通的手机芯片到销售价在$1到$5之间。”

7. 20nm和14nm的微影成本也是一个热门话题。行业普遍认为,20nm双重图案的价值是可观的,并且以50nm的金属间距和70nm的栅极间距而言,14nm三重图案在技术上是可行的,但在手机市场中,它并不划算。业界将转向昂贵的间距缩放和专注于制造更好的芯片,比如像20-28nm级别的。

8.随着第三代iPad的出现,我们应该更重视GPU的功耗、性能和成本指标。苹果的A5X芯片的峰值功率大约为5W,而其中大约80%左右是为GPU供电的。 与CPU相比,GPU模片区面积也更大一些。毫无疑问,在与平板电脑市场竞争时,A5X将是其“新标杆”。

9.加州大学伯克利分校的Tsu-Jae King Liu教授论述了从平面CMOS发展到“end of the CMOS”经历了一个怎样的历程。今年6月,IBM还发表了一篇关于“将平面延长至14nm”的文章。跟王教授一样,其他的专家也认为,平面的CMOS也终按将end of the CMOS模式发展。 FinFETs肯定有更好的静电分析,但用高制程变动和大量的设计限制来移植和设计,依旧是一个重大问题,特别是对手机市场而言。就像硅技术一样,在SOC内部进行IP设计以及如何利用新技术使得IP生态系统的设计能快速设置都是很重要的。 (这点在今年早些时候发表的“怎样在芯片之战中大获全胜?”一文中也有提到)

在2012年的热门产品中,可以看到相关的2个例证:新一代iPad不使用旧的应变硅或高电介质金属门;由于Snapdragon以超低价和更少硅技术特性与LTE的结合,使得高通在新的三星Galaxy S3上赢得为通信SoC设计的机会。

10.会议结束时,我们一致认为:“在未来很长一段时间内,想要超越这个伟大的会议是非常困难的。”

电子发烧友网编辑论:

一直以来,CMOS芯片因其制造成本较低、效率较高以及数据传输速度较快等优势,在越来越多的产品及应用领域得到更广泛的应用,市场更青睐于采用CMOS传感器。就目前来看,智能手机市场仍然是未来CMOS传感器的最大应用市场领域,去年份额便占据了总体CMOS出货量的79%之多。另外笔记本电脑普遍装备摄像头,电视会议将成为CMOS的第二大应用市场。除此之外,CMOS传感器在安防监控领域、汽车系统等两个增长型市场中的应用也不断上升。

——电子发烧友版权所有,转载请注明出处!

打开APP阅读更多精彩内容

在最近召开的2012年半导体国际研讨会上, 该会议围绕CMOS技术的未来开展。会议的重点是展现英特尔首个新技术——22nm 3D三栅极晶体管,其中一个座谈小组还就FinFET设备技术进行了研究。令人惊讶的是,大家却有着截然不同的观点,并且这些观点都可以说是有理有据的。我从来没有在该行业内见过大家的观点竟有如此大的差异。然而,也有可能是,没有哪个专家的观点是对的或是错的。显而易见,每个专家都是用不同的“价值标准”来衡量的。我把这个“价值标准”定义为衡量芯片的指标(如:成本、功率和性能)以及芯片设计指标(如:设计成本、复杂性和投放到市场的时间)。

对于那些未能参加研讨会的人,我为他们总结了自己对本次会议的10大见解。

1.Intel的22nm 3D三栅极晶体管是令人印象深刻的工程。在一个300mm的晶片上将近有1万亿个鳍状结构片(大约相当于在每一个CPU上就有30亿个鳍状结构片;每一个鳍状结构片的最大宽度也只有6-9nm,大约只占12-18硅晶格距。)这将是有史以来最小的横向特性图案, 就算是对高容量CMOS制造业而言也是一样的。对22nm的CPU而言,几乎每片鳍状结构都是很重要的。因为如果CPU上任何一个鳍状结构受到损坏,那这个CPU就卖不出去了。我仍相信,拥有三栅极技术能使得Intel在未来5年中领先于同行。

2. Intel目前在三栅极CPU方面有所发展,虽然说产量不高,但是这种情况随着三栅极技术的出现会有所改善的。在ICs行业,性能历来就比成本和功耗更重要。然而,生产商和智能手机芯片设计工程师很快就指出:毫无疑问,移动SOCs中使用了硅技术,并且成为行业领先产品。对于制造英特尔智能手机处理器芯片(如Medfield和Cedar Trail)而言,在产品的成本、功耗和性能方面上,用28 nm的生产远比用32nm的要好得多。生产时,也会有一套丰富的28nmIP核设计过程,比如基带的集成以及在单个28nm集成电路SOC上的应用处理器。我能感受到制造公司和设计公司在回应Intel的大胆声明(“无生产线模式正在逐步崩溃”)时就曾正式指出了这点。

3.在会议之前,逆向工程公司Chipworks曾报道说Intel的鳍状结构外形是一个不规则的四边形形状,并且那一点无论是在会前、会中或会后都是一个关键的主题。专家们都一致认为,理想的FinFETs应该有一个矩形翅片,并且产量问题可能会导致Intel在技术周期结尾时改变鳍状结构的形状(由于日程安排的疏忽,所以导致未能改变)。令人惊讶的是:在Intel的paper Q/A中,当要Chris Auth对鳍状结构加以介绍时, 他给大家的回答是“性能”(降低外部电阻)。最开始,人们对其模型的假设是确定一个与清除的间隔的散热片材料相关的产量问题。普遍的共识是,fin profile(尽管对Intel来说是好事)对手机部件而言将有太多变化。这些手机部件发展不快速,包装也不完整(通常是专门为在最坏的情况下设计的,98%产量都是这样的)。大多数人认为,如果做到14nm,那么Intel就能做成一个矩形鳍状外形了。

4.对一般散装不规则形状的FinFET(具有单个n和pFET工作功能,并且可以通过整晕掺杂设计点来调整阈值电压)进行了讨论。达成了对Intel某些方面的一致认识(这些方面包括:设计出发点、对其工作和应用到市场时总结的经验教训进行的讨论)。主要包括以下几点:

a.由于它会导致关断泄漏,所以对在底部形成的非完全耗尽晶体管、鳍状结构较厚的部分有着高度关注。Intel只报道低于1nA/um的泄漏情况。1nA/um,这对中央处理器来说是一个适当的目标,但智能手机设备需要在10pA/um范围内为总处于首/尾功的率门控装置降低约100倍的泄漏。

b.另外一种降低关断泄漏的方法是添加栅极功函数。然而,想要在3D结构上添加四个或更多功函数并不是一件简单的事(仅是双阈值电压类型的话,就只要2n和2p)。这对移动市场而言,是件非常成本高并且很复杂的事。

c.在设计方面的话,会议集中讨论了bulk-only FinFET方法。这种方法很有可能需要对系统进行再分配。一般而言,电源管理单元、射频甚至模拟电路都需要关断芯片。对低成本移动解决方案而言,单芯片SOC几乎是必需的,因此FinFET应该想中国3G SOC市场一样在大范围内不具备足够的吸引力。

5.仪器专家对FinFET器件的看法有好有坏:

a.“好”:理想的FinFET器件具有卓越的DIBL和顶端设备的摆幅(当顶级设备的阀值低,并且其电流由顶部的鳍状结构决定时,Intel公布的数字是令人印象深刻的);

b.“坏”:真正的FinFET元件子鳍泄漏和高翅片高度控制晶体管的变化,掺杂鳍,鳍的形状和所有的3-D工艺步骤的设备和工艺工程师普遍认同,“理想的FinFET元件是伟大的,但生产FinFET元件失去了一些平面器件相比的优势,当然这取决于如何实施。”

真正的FinFETs在体积上受到sub-fin泄漏和高晶体管变异(由鳍状结构高度控制、鳍状结构参杂度、鳍状结构形状和所有的3D流程步骤导致的)的影响。设备和工艺工程师普遍同意,“理想FinFETs非常棒,但是实际生产中的FinFETs相比平面设备而言却失去绝对优势”,这取决于如何实现。

6.在此次会议上,我们看到了许多关于FinFET器件的研究论文。移动手机领域里的专家们明确表示,“成本将比市场所能承受的要高。”这些技术看起来挺有趣的,比如说为$200的CPU配上 $1,000的服务器芯片,但“我的高端手机芯片只卖20美元”或者是说“普通的手机芯片到销售价在$1到$5之间。”

7. 20nm和14nm的微影成本也是一个热门话题。行业普遍认为,20nm双重图案的价值是可观的,并且以50nm的金属间距和70nm的栅极间距而言,14nm三重图案在技术上是可行的,但在手机市场中,它并不划算。业界将转向昂贵的间距缩放和专注于制造更好的芯片,比如像20-28nm级别的。

8.随着第三代iPad的出现,我们应该更重视GPU的功耗、性能和成本指标。苹果的A5X芯片的峰值功率大约为5W,而其中大约80%左右是为GPU供电的。 与CPU相比,GPU模片区面积也更大一些。毫无疑问,在与平板电脑市场竞争时,A5X将是其“新标杆”。

9.加州大学伯克利分校的Tsu-Jae King Liu教授论述了从平面CMOS发展到“end of the CMOS”经历了一个怎样的历程。今年6月,IBM还发表了一篇关于“将平面延长至14nm”的文章。跟王教授一样,其他的专家也认为,平面的CMOS也终按将end of the CMOS模式发展。 FinFETs肯定有更好的静电分析,但用高制程变动和大量的设计限制来移植和设计,依旧是一个重大问题,特别是对手机市场而言。就像硅技术一样,在SOC内部进行IP设计以及如何利用新技术使得IP生态系统的设计能快速设置都是很重要的。 (这点在今年早些时候发表的“怎样在芯片之战中大获全胜?”一文中也有提到)

在2012年的热门产品中,可以看到相关的2个例证:新一代iPad不使用旧的应变硅或高电介质金属门;由于Snapdragon以超低价和更少硅技术特性与LTE的结合,使得高通在新的三星Galaxy S3上赢得为通信SoC设计的机会。

10.会议结束时,我们一致认为:“在未来很长一段时间内,想要超越这个伟大的会议是非常困难的。”

电子发烧友网编辑论:

一直以来,CMOS芯片因其制造成本较低、效率较高以及数据传输速度较快等优势,在越来越多的产品及应用领域得到更广泛的应用,市场更青睐于采用CMOS传感器。就目前来看,智能手机市场仍然是未来CMOS传感器的最大应用市场领域,去年份额便占据了总体CMOS出货量的79%之多。另外笔记本电脑普遍装备摄像头,电视会议将成为CMOS的第二大应用市场。除此之外,CMOS传感器在安防监控领域、汽车系统等两个增长型市场中的应用也不断上升。

——电子发烧友版权所有,转载请注明出处!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

评论(0)

发评论

-

dplion

2012-07-01

0 回复 举报很经典啊。 收起回复

dplion

2012-07-01

0 回复 举报很经典啊。 收起回复

-

议智能手机+平板电脑,商机?!2012-01-06 3381

-

智能手机基础知识讲解2012-08-15 49462

-

基于IMS的双模智能手机系统的设计2012-08-20 2171

-

智能手机2013-06-23 5685

-

求智能手机的结构资料2013-08-30 3224

-

智能手机如何判断人脸的贴近2013-09-30 5037

-

高端智能手机和PCB2014-05-17 20917

-

模拟智能手机2016-09-26 3505

-

pads智能手机培训2017-09-27 2444

-

你怎么定义智能手机壳,觉得高科技+手机壳=智能手机壳吗?!2018-01-05 5753

-

自动对焦在智能手机的应用2019-07-16 3962

-

智能手机怎么才能更加智能?2019-08-20 3976

-

如何设计智能手机省电系统?2019-11-05 2635

-

请问如何去设计一种智能手机系统?2021-04-25 2369

-

使用电脑的USB端口对智能手机充电2021-09-14 3716

全部0条评论

快来发表一下你的评论吧 !