InterfaceDesinger 使用案例

描述

时钟输出

易灵思所有的GPIO都可以用作时钟输出。这里我们提供两种时钟输出方式。

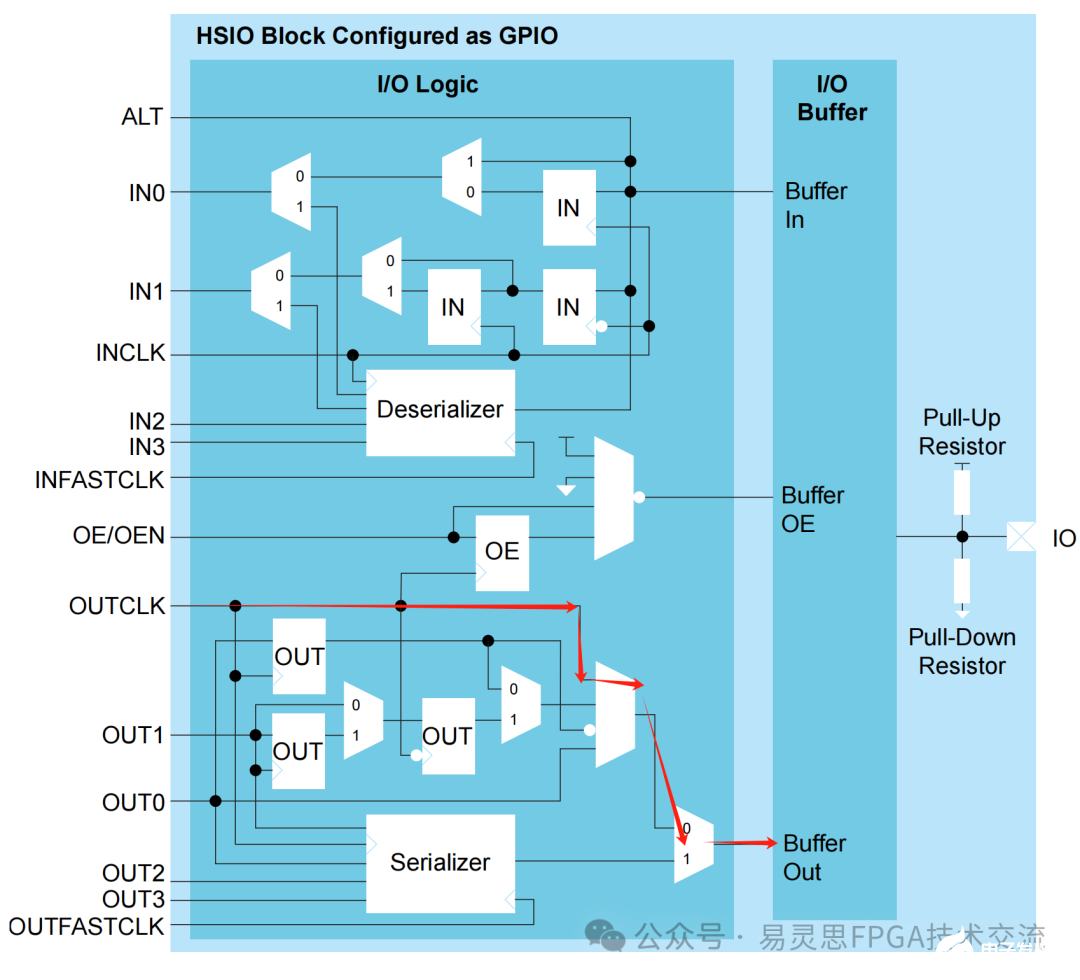

方法一:把时钟设置为clkout模式。下图选自钛金系列ds上的IO框图 。从图片上可以看到OUTCLK的路径。

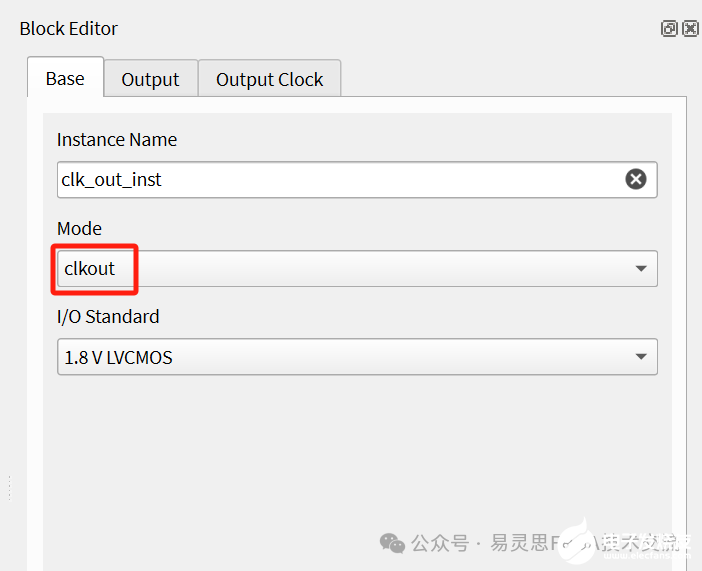

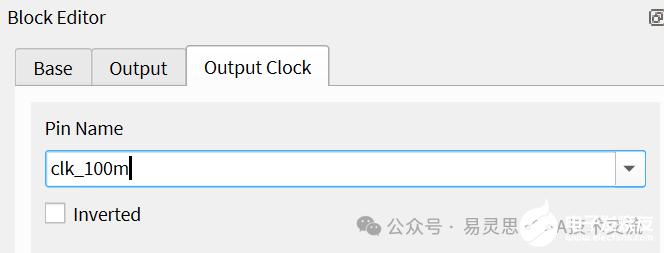

在添加 GPIO时,设置Mode为clkout,并在output Clock中输入时钟名。

这里需要 注意的是,时钟名不能从core直接输出,而只能使用interface中使用的时钟,如PLL输出的时钟或者GCLK输入的时钟。比如我们在代码中定义了一个IO,如下:

module clk_test(...output clk_100m,...);

如果直接把代码中定义的clk_100m直接配置给interface的GPIO,这时软件会报错。

方法二:

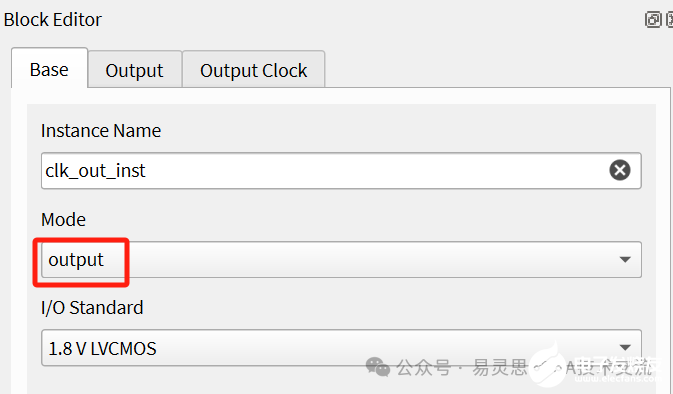

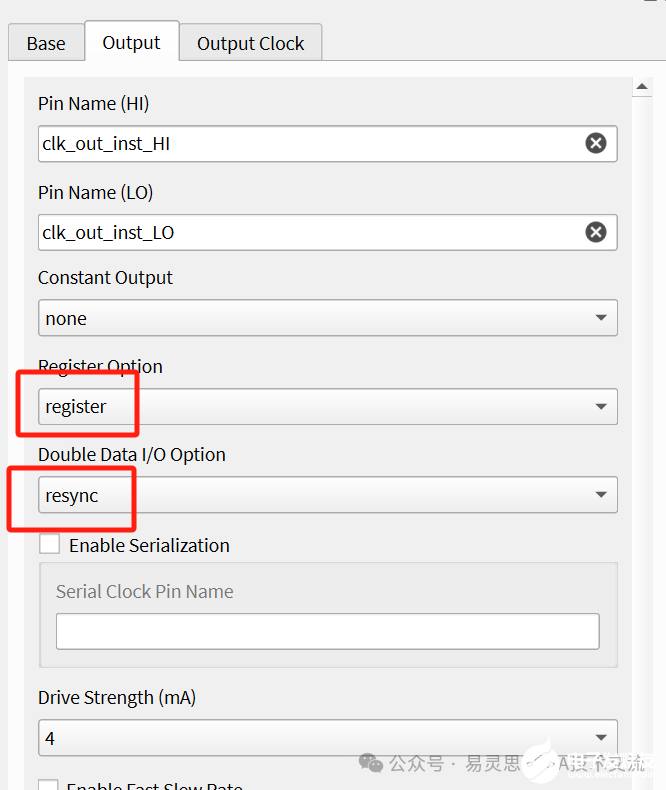

通过DDIO的方式设置时钟输出。IO模式设置为output,并打开Register Option及Double Data I/O Option,并指定时钟。

程序内部分别对DDIO的高低位分部赋值为1或者0.

assign clk_out_inst_HI = 1'b1;assign clk_out_inst_LO = 1'b0;

对于两种方式的使用,Trion有很大一部分的GPIO不支持DDIO,只能使用第一种方式,钛金所有的GPIO都支持DDIO;另外在源同步时钟数据输出时,DDIO的方式可以保证数据和时钟的延时一致,所以易灵思推荐使用DDIO的方式。

Efinity处理三态端口问题

我们在处理三态门时一般都是用下面的语句;

inout bidr_pad;wire in;wire out;wire o_oe;assign bidr_pad= o_en ? out :z;assign in = bidr_pad;

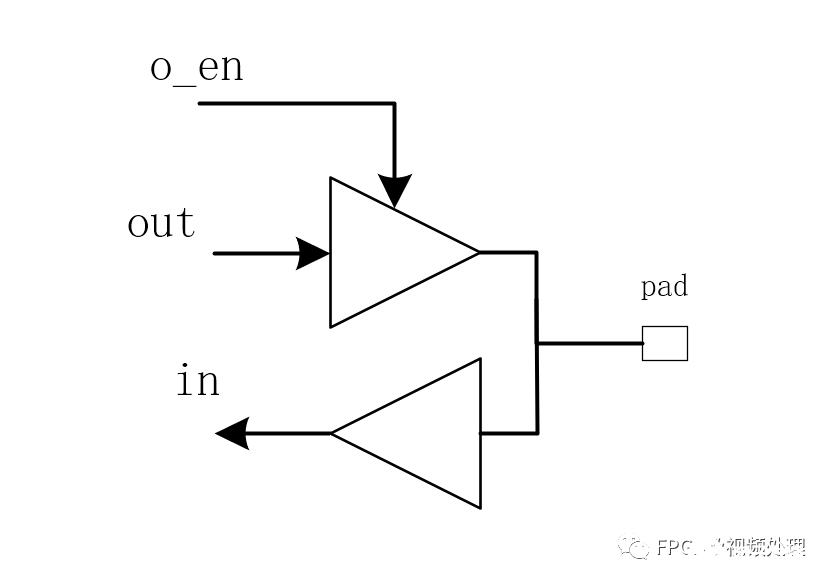

其实它对应的硬件结构就是下面的框图。它涉及到3个信号:in,out,o_en。

当o_en = 1时,out可以通过out buf输出到pad上,同时会反馈到in;

当o_en = 0时,out buf就是高阻态。in的信号就是通过外部pad通过in buf输入进来。

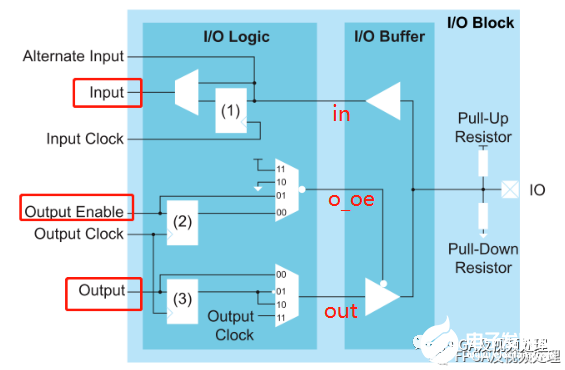

最初使用Efinity,因为架构差异,很多人被inout的使用难住了。这里来说明一下。在易灵思的产品架构中,原有的rtl代码都是针对fabric的,也就逻辑部分。而IO被认为是外设。如下图I/O Buffer部分相对于fabric是外设,它是在Efinity的interface Designer中设置的。这样在rtl只需要定义:

input in;output out;output o_oe;

有了上面的认知,我们就容易理解在efinity中怎样添加三态。

添加三态门的过程如下:

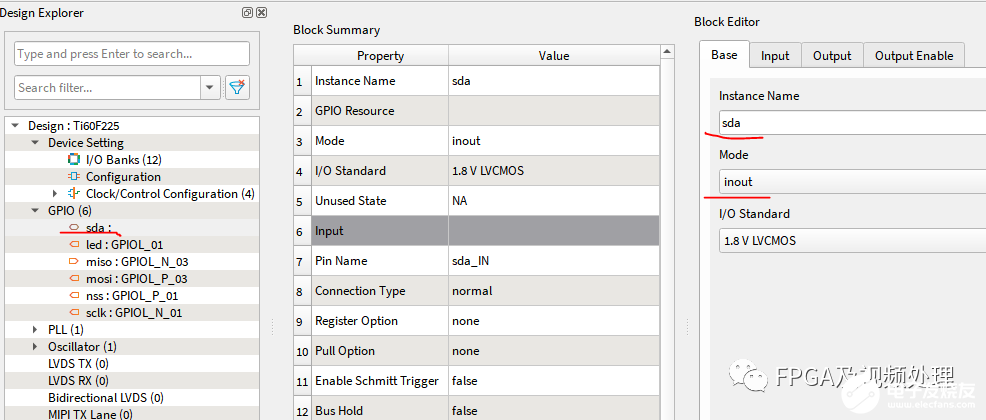

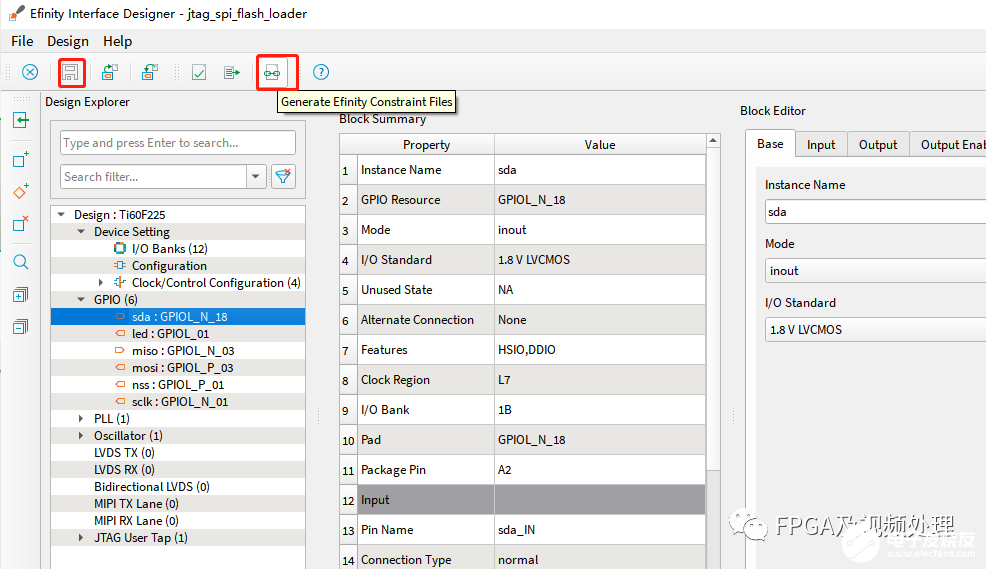

我们在interface中添加一个gpio,命名为sda,把Mode,选择为inout,

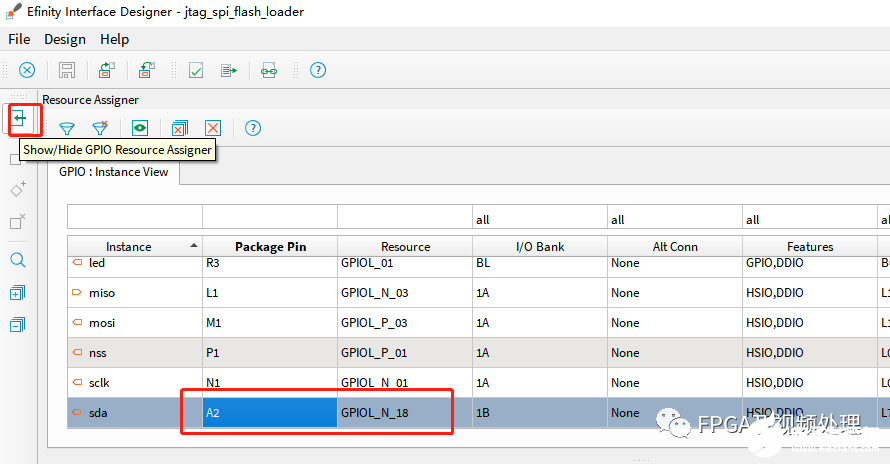

点击show/Hide GPIO Resource Assigner,打开IO分配界面分配IO.

点击保存和Generate Efintiy Constraint Files.

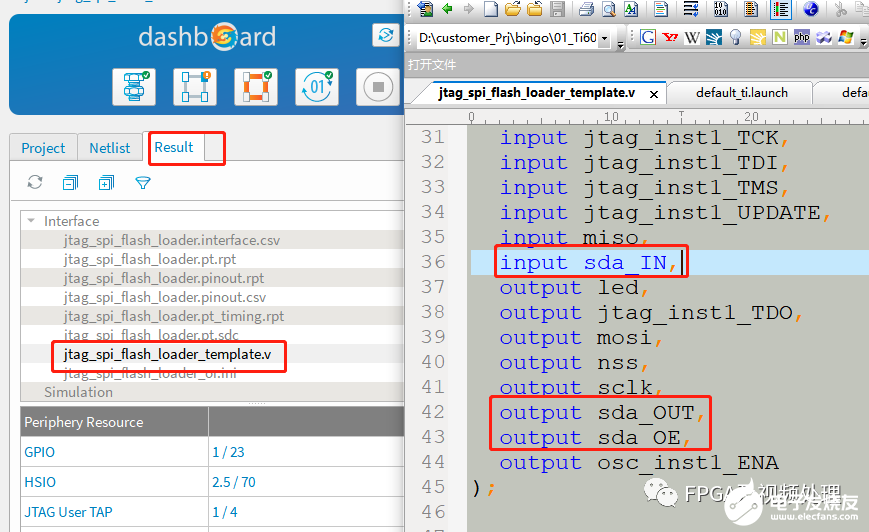

打开工程面板下面的Result下的 xxx_template.v,可以看到里面添加了

Input sda_IN,output sda_OE,output sda_OUT

三个信号,把这三个信号复制到工程文件的顶层中去,这样就定义好了一个inout,可以直接全用了。

另外如果要添加IO寄存可以根据实际需要去选择,同时要注意为寄存器选择准确的时钟。

这样就不用再写assign sda = oe ? sda_out :z; 这样的语句,因为oe就是sda_OE, sda_out对应的就是接口生成的sda_OUT。

在Efinity的.v文件中不支持inout 双向口的定义,另外Efinity也不支持‘z’这种定义。

全部0条评论

快来发表一下你的评论吧 !