基于FPGA的AES256光纤加密设计案例实现

描述

概述

近年来,信息安全应用于生活中的各个领域.在光通信系统中,往往对速率有着较高的追求。其中对光模块,光纤通信中的传输算法,传输的模式以及光波段选取有密切关联。传统的光通信系统在于保证传输带宽和吞吐量而并未考虑到对信息安全的保护。随着对带宽,速率等要求日益增加,高速通信已经成为基本的要求。光纤通信因其具有低损耗,高抗干扰性,从而广泛得到应用。近几年由于大量用户数据的泄露,造成了极大的损失,使得信息安全成为人们关注的焦点。

目前光纤加密的研究多采用量子加密的方法,本人在中科大量子物理实验室下属机构问天量子实习发现,目前国内外在实际工程上存在很多漏洞,无法做到光纤通信中的绝对安全,实现军用和民用任重道远。华为传输加密解决方案,采用L1层加密技术,对业务层透明,采用高强度的美学256算法,确保各行业的数据安全性。此方案虽然实现简单,但缺点是吞吐量小、端口少、速率低。

对于AES算法的硬件实现,国内外研究学者大部分是基于FPGA的硬件实现。解放军理工大学的吕游等人研究高级加密标准俄歇算法的设计原理,并通过加密部分和密钥拓展共用 S 盒以减少资源占用,然后在FPGA上完成加密部分的优化实现,其加密模块的最大吞吐率可达到1.326 Gbit/s,消耗1507个乐(1 BLM=1 LE=0.5 Slice)。埃及开罗德国大学的Mazen ei Maraghi,Salma Hesham等人研究速度与面积优化的俄歇算法的FPGA实现,利用循环迭代的方法减少逻辑资源的消耗,在FPGA芯片Xilinx Virtex 5 XC5VLX 50上实现,使用了 303个可编程逻辑单元(切片)、加密速度为1.33 Gbit/s...通过分析国内外ASE在硬件上实现的研究现状,我们想要用FPGA硬件实现,达到5 Gbps的传输速率,这是完全可行的。

主要创新点

1. AES加密算法在上的实现

最常用的数据加密方式是软件加密,即在通用微处理器上编程实现,但其加密速度普遍不高,算法实现的效率较低,安全性和可靠性有限,很多时候不能满足用户的需求。因此,需要更加快速,更加安全可靠的加密实现方式来满足人们在一些场合下的数据保密要求。

由于我们传输的速率达到5 Gbps、这种GTP高速接口下若使用FPGA+ARM架构(如Zynq)、通过手臂完成加密算法将会使得我们效率大大降低,因此串行通信实现俄歇加密算法已经不能满足我们的需求,故我们采用纯Pl端FPGA设计来实现加密算法。FPGA设计加密算法具有安全性高,加密速度快,开发周期短,开发成本较低,可重配,可靠性高以及移植性好等优点。

2. AES算法在光纤链路上的算法移植

算法移植通常是通过成熟的库函数进行调用,该串行方式下一个时钟周期只能完成一条指令的实现,算法移植相对简单,不会出现异步跨时钟域处理高速数据等问题.我们选择纯Pl端完成算法移植,在一个时钟周期下,既要完成算法的数据输出,也要考虑到此刻光纤链路中传输状态。因此我们的效率虽然大大提升,但对我们的设计是一个巨大的挑战。

针对速率匹配,数据对接,缓冲设计等问题,我们分别进行了模块化设计,分别对其进行仿真和上板测试。在软件调试部分有详细的分析和设计介绍。证明我们的算法移植是成功的。

3.针对AES算法在光纤发送端进行特定的帧定制

在算法移植过程中,我们针对俄歇算法对光纤协议进行了帧定制。传统的帧传输是对数据流进行传输,对固定长度的数据流加上帧头帧尾进行判断。一旦丢包,整个帧全部丢弃,造成了极大的浪费。

我们对原始的这种光纤帧协议进行了定制,在原来每一帧的基础上,内部对其封装了四个子帧,每一个子帧由128位组成(原因是我们每次加密的数据是128位)。对于每一个子帧,帧头为起始的16位数据,具有和其他112位数据不一样的脉宽长度,便于后续的帧解析。

通过我们的设计,即使传输过程中丢包,只会影响该当次的128位数据,且该设计给我们帧解析,加密算法的解码提供了便利的平台。

4.接收端对帧数据恢复

光纤接收端设计部分除了会面临数据流缓冲,高速率通信中异步跨时钟域处理等问题,还要剥离原始子帧结构,并且去除光纤本身的帧头帧尾。除了我们的加密数据,奥罗拉协议本身还会不定期发送一些无效数据,我们要对其进行数据恢复,并且拼接光纤链路中的16位数据,封装成一个个的128位加密数据.这也是我们设计的一大难点。

5.高速通信中时序约束和信号完整性分析

对于GTP高速接口,我们对其做时序约束是非常有必要的。除此之外,还要要用专业的软件对光口进行测速,并对其信号质量进行分析和评估。

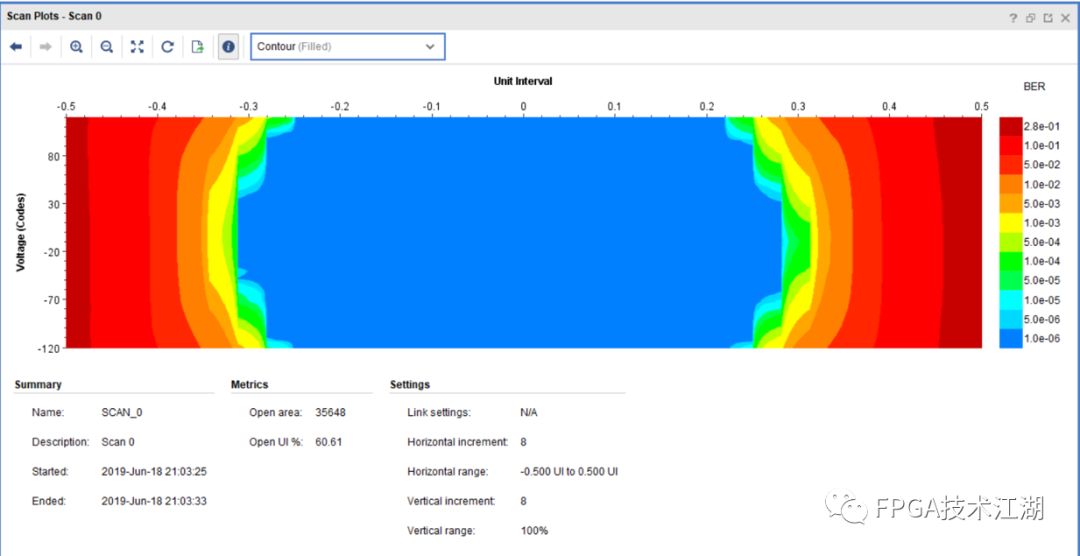

我们使用Seiral I/O分析仪连接到艾伯特核,验证高速串行通道的状态.从眼图上可以观察出码间串扰和噪声的影响较小,数字信号整体的特征良好,从而判断出系统具有非常良好的性能。

作品的难点与创新点部分设计,将会在第四部分(软件设计与流程)中详细的阐述。

系统架构

1.AES加密算法

俄歇算法属于对称密码体制中的一种分组密码,有AES-128、192 和 256 三种密钥长度。以AES-256算法为例,算法的分组长度是256 位,密钥长度同样是256 位,在分组或密钥长度不足256位时,需按照相应的补位规则补足256位。

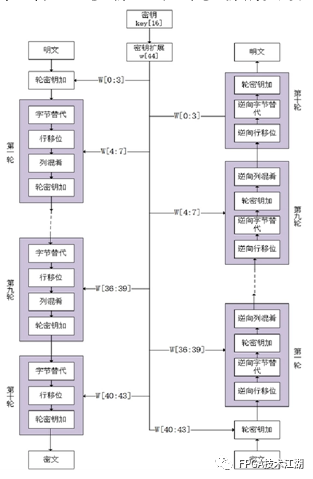

在算法中有多轮的重复的变换称为轮变换,轮变换有三种类型,分别为初始轮、重复轮和最终轮.每一轮中又包括:字节代换、行移位、列混合和子密钥加几个步骤,而最终轮没有列混合这一步骤。这几个步骤的大致过程如下,如图3-1。

图3-1:俄歇加解密过程

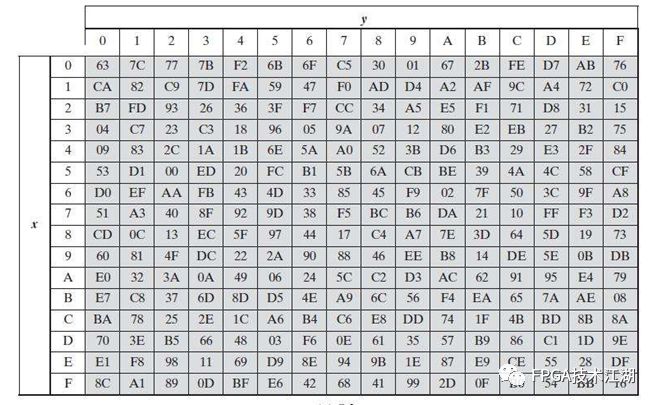

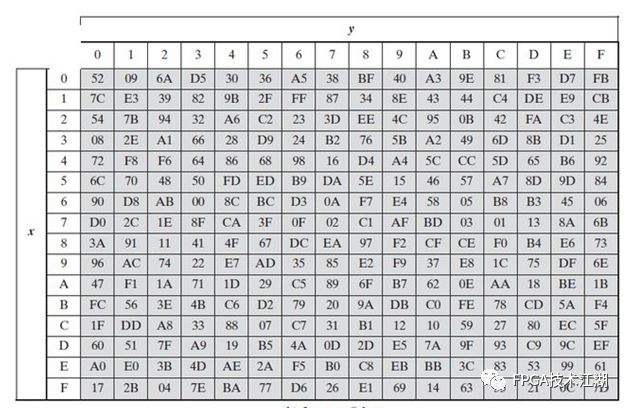

如图3-2和图3-3所示所示为S盒,逆S盒。字节代换是通过字节代换表(S)盒)对数据矩阵进行非线性代换,行移位是以字节为单位对数据矩阵进行有序的循环移位,列混合是将列混合矩阵与数据矩阵进行一种矩阵乘法运算,子密钥加是将数据矩阵与子密钥矩阵进行按位的异或运算,子密钥按照特定的密钥扩展方法生成。由于属于对称密码体制,算法的解密即为加密的逆运算。

图3-2:S盒构造

图3-3:逆S盒构造

2.AES加密算法在硬件上的优化

2.1字节替换与行位移

在俄歇算法迭代的过程中第一步就是进行字节替代,它属于非线性变换.按照它的替换规则,输入A对应唯一的输出B、这中间的运算过程如果用硬件组合逻辑实现的话,会浪费大量的逻辑资源,而且也需要一定运算的时间。既然输入和输出一一对应,输入为8位字节,那么输出最多也就256种情况,而且对应规则也知道,所以我们可以先用其他软件,如MATLAB计算出输入和输出的置换表:输入的低四位对应列地址,高四位对用行地址的16*16的置换表.这样通过输入的8位二进制数可以快速查找到对应的8位二进制数。相应的在解密的过程中,也可以用置换表的方式完成逆字节的替换。这种优化方法可以减少逻辑资源的消耗,也提高了运算速度。

按照AES算法,进行完字节替换后,紧接着是行位移.但是我们可以在进行字节替换时同时进行行变换,如输入A矩阵的第3行,即第5、8、10、15字节,对应输出新的矩阵B的第8、5、15、10字节,这样就可以同时完成字节替换和行位移,节省时间和资源。

2.2列混淆

完成字节替换和行位移后进行列混淆,列混淆就是通过输入矩阵的列重新加权再组合形成新的输出矩阵。在这个计算过程中,加法运算等价于异或运算,乘法可以进行优化。乘法运算则需要分为两种情况考虑:如果8位二进制数BIJ最高位为1、与02做乘法运算时,需要先左移一位,然后与00011011进行异或运算;如果它的最高位为0、与02做乘法运算时,只需要左移一位。而所有的数都能分解成02不同次幂的和,所以可以做一个02乘法查找表,这样任何一个数都可以通过先分解成02的不同幂和,在通过查找表找到对应的值,这样就完成了乘法的优化。在解密的过程也是一样,通过查找表的方法优化乘法。这样仅用一个查找表的资源完成了多次组合逻辑运算,极大的减少了逻辑资源的消耗。

2.3轮迭代内部流水线结构

俄歇算法加密过程包括 10 轮迭代,每轮迭代的组合逻辑模块包括AddRoundkey,SubBytes与漂流,混合柱,密钥扩展。前面在每轮迭代之间引入了流水线,但单次轮迭代内部中仍有 3 个组合逻辑模块,为了降低延迟,所以在轮迭代内部引入流水线结构提升加密速度。

我们在加密过程中,加密算法消耗的实际时间为68个时钟周期,以100米晶振为例,一次编码过程仅消耗680 ns,保证了我们实际传输过程中在安全保密的基础上,还能实现高速率通信。

2.4极光光纤链路协议

西林公司针对高速数据传输开发了一种轻量级的可定制的链路层协议--奥罗拉协议。协议内部集成了与其相应的GTP收发器,通过连接多个GTP可以实现传输带宽的拓展,同时它也可以被上层的自定义协议或者其他行业标准协议采用。

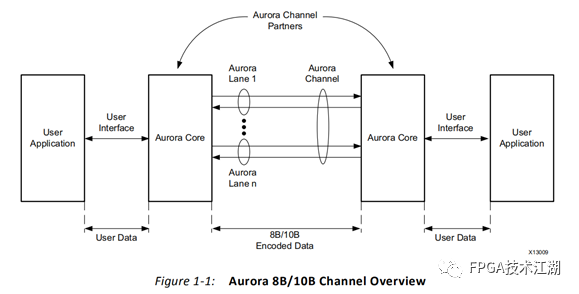

奥罗拉协议描述了用户数据在Aurora 8B/10B通道(频道)之间的传输过程。一个Aurora 8B/10B通道(频道)包含一个或者多个链路(里)、每个链路都是一个全双工的串行通路。Aurora 8B/10B通道上的通信双方被称为通道对(频道合伙人),如图3-4。

图3-4:奥罗拉链路框架

奥罗拉协议通用数据链路速率在480 Mb/s到84.48 Gb/。该协议具有如此强大的功能,究其原因是其内部有一个专用硬核,这个硬核专门用来进行数据的高速传输,并且它的传输方式可以由用户根据实际需求来设置为全双工或者单工。该硬核主要利用GTP收发器来进行数据的传输。

奥罗拉协议主要对物理层接口、初始化和错误处理机制、数据排列、链路层以及流程控制作了定义和要求。其中物理层接口讲述了电气特性和时钟编码等;初始化和错误处理机制则定义了单通道和多通道两种情况下,数据传送之前对通道进行初始化的步骤,同时介绍了在遇到错误代码传输时该如何应对处理的机制。数据排列描述了数据在通过一个通道后,如何在多个串行链路中进行传输。链路层定义了一个用户数据单元如何开始传送以及如何结束传送,同时还描述了在数据传输过程中如何暂停数据流并插入更高优先级数据的过程.除此之外,链路层还提供了当出现接收器和发射器在时钟速率上出现差异问题时该如何解决的方案措施。最后,流程控制则是规定了链路层流程控制机制,以及上层用户流程控制信息的传输机制。

我们之所以选择奥罗拉协议,放弃了PCIe,SRIO 2.0,UDP等协议,考虑到以下一些因素:奥罗拉协议除了可以达到很高传输速率外,在链路数目选择的灵活性,协议的可定制性上,远远超过了上述的协议。由于我们需要用到奥罗拉协议传输加密数据,故冗余信息越少越好,否则对冗余信息加密将造成很大的带宽损失.奥罗拉协议的可定制性主要表现在:

1.可以很方便的使用AXI 4-流进行帧传输/流传输;

2.可附加16位的加扰器/解扰器 ;

3.可选16位/32位的启联校验 ;

4.支持热拔插(热插拔)等方面。

4.硬件电路设计

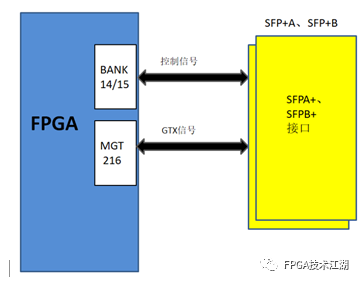

我们硬件电路设计主要体现在SFP+光口与FPGA板卡之间的设计。如图3-5所示。

图3-5:FPGA与SFP+连接设计

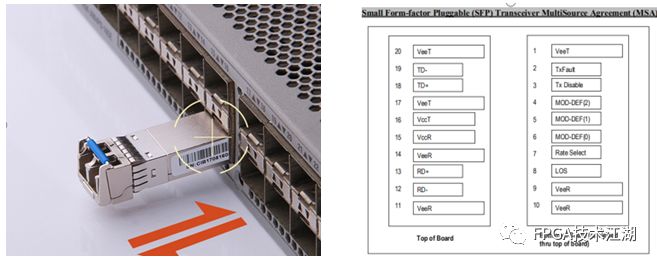

首先我们介绍所使用的光模块。图3-6所示为我们使用的SFP光口实物图与引脚图。使用的SFP+的光模块支持8B/10B,也可支持64b/66B的长波(1310 nm)的单模光纤(SMF),有效传输距离为2M到10公里。事实上最高可达到25公里。光口支持SFP-MSA协议,选用的光模块支持10 GBase-LR/LW。

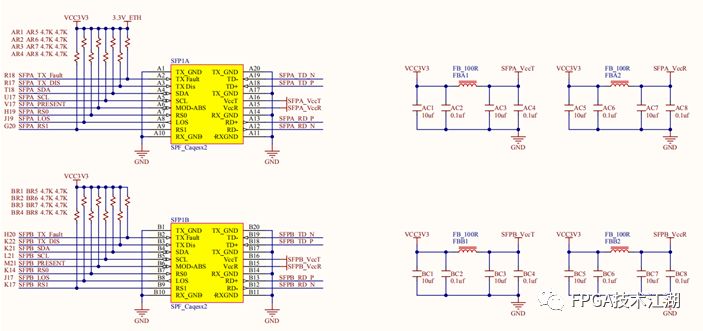

图3-6:SFP+实物图与引脚图 FPGA与SFP+光口的电路的原理图设计如图3-7所示。

图3-7 :FPGA与SFP+光口连接图

设计演示

艾伯特(综合误码率测试仪)是西林提供的用于调试FPGA芯片内高速串行接口的工具。它通过JTAG总线提供了FPGA到Vivado串行I/O分析仪的通道.通过艾伯特用户可以定制线速率、参考时钟速率、参考时钟来源,总线宽度。它同时还额外需要一个系统时钟,这个时钟可以来自GTX收发器或者其它FPGA管脚。

使用艾伯特进行GTP通道的验证有以下三个步骤:

1.生成艾伯特核:根据硬件高速串行总线的需求来定制和生成伊伯核。

2.使用上一步的艾伯特核自动生成艾伯特参考设计并生成钻头文件。

3.使用Seiral I/O分析仪连接到艾伯特核,并验证高速串行通道的状态。

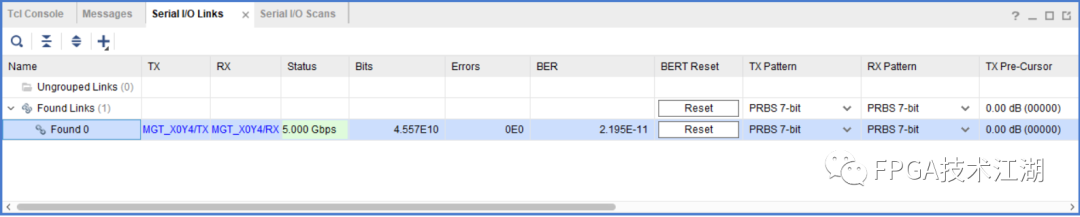

我们在维瓦多中生成该测试工具,对SFP+光口实际发出的数据进行测速和信号完整性分析。如图5-1所示。我们可以在图的正下方观察到该链路的实际速率为5 Gbps、速率完全满足我们的设计需求;误码率越低,颜色越偏向蓝色(深蓝色);当误码率越高,颜色越偏向红色,眼图张开的大小就代表信号质量的好坏。我们通过观察眼图可以发现,蓝色区域很大,且角度张开合理。结合图5-2,通过5 Gbps速率的光纤传输4.557E10位数据后,误码率仅为2.195E-11,远低于官方规定的误码率1.E-10标准,可以得出结论:信号完整性分析良好,信号质量传输可靠。

图5-1 :二维眼扫描眼图

图5-2 :误码率结果图

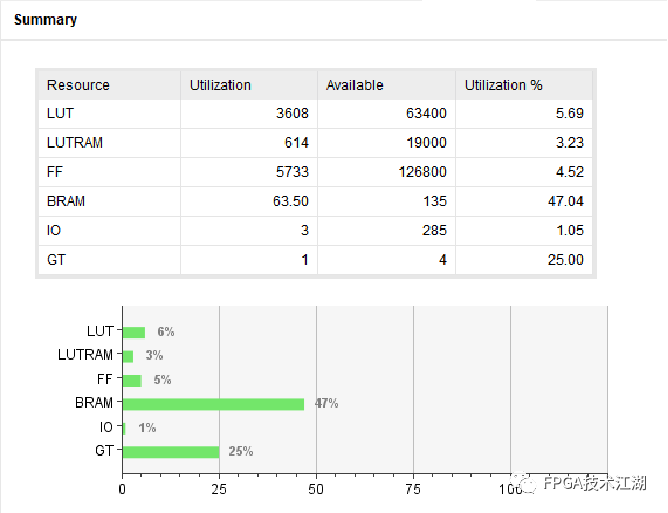

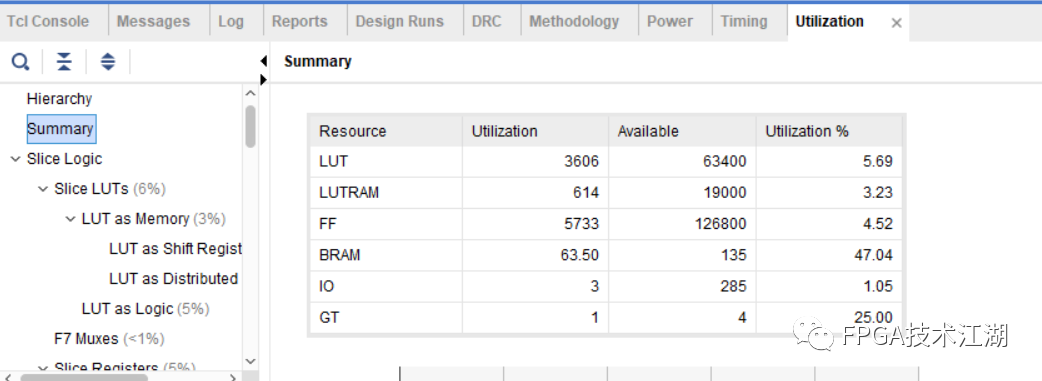

同时我们通过算法在硬件上的优化,可以占用很少的资源到达所需要求,如图5-3和图5-4所示,可以看出很低的资源利用率。

图5-3:发送端资源利用率统计图

图5-4:接收端资源利用率统计图

审核编辑:刘清

-

AES加密流程2025-10-23 277

-

基于FPGA的AES256光纤加密设计2024-06-19 932

-

基于 FPGA 的光纤混沌加密系统2024-04-26 1915

-

aes加密破解难度2021-08-09 4503

-

AES 256加密认证芯片介绍 带加密认证功能的EEPROM2020-10-14 4184

-

DKT加密芯片AES256的数据手册免费下载2019-10-22 1254

-

基于FPGA实现AES算法数据加密方案2018-12-30 6777

-

xilinx FPGA bit 文件加密2018-12-01 6238

-

嵌入式AES加密IP核设计2017-09-07 950

-

用C 语言描述AES256 加密算法2017-01-13 2810

-

转:熟悉AES加密2016-07-09 7222

-

【FPGA参赛作品】基于FPGA的AES分组加密系统2012-06-12 4524

-

基于FPGA的AES加密算法的高速实现2010-01-25 830

全部0条评论

快来发表一下你的评论吧 !