森丸电子推出针对集成无源器件需求的IPD工艺方案平台

描述

集成无源互连

无源互连是电子系统实现功能中必不可少的一部分。随着更高算力,更高带宽传输,更高集成度模组等技术的不断演进,对无源集成也提出了更高的要求。

Intel等国际先进的高算力运算芯片厂家宣布即将开始导入玻璃基板的量产化,引领基于玻璃的半导体产业链急速发展。国内外众多厂商间掀起一股技术浪潮。基于玻璃基底的全制程工艺解决方案,正成为支持半导体产业进一步发展的关键领域。

玻璃的优势

玻璃作为一个日常生活中非常常见的一种材料,因为其耐冷热性,塑形可加工性,电绝缘性,以及性能稳定,是许多日用品的常用材料。而随着高算力,高传输带宽,高集成度模组的不断发展,对无源互连集成度提出更高要求,需要在半导体器件和封装行业,除了单晶硅(Si)和有机树脂类材料之外,需要寻找更适合高集成无源互连的新型材料。而玻璃正是在这种应用的强力驱动下,成为集成无源互连方案中最具竞争力的一种选择。

玻璃的电性能是选择玻璃作为无源基材的主要原因之一。相比较于硅,玻璃具有极佳绝缘性能的优势。在高频率传输或无线射频/毫米波等领域,尤其能体现其优越的性能。玻璃的机械和热稳定性好,且在几十年来的应用中使之形成非常成熟的高精度、高质量、高平整度、大尺寸的加工能力,非常适合进行大规模集成电路薄膜工艺。近些年来在TGV玻璃通孔工艺在工程技术和高效率生产方面中的逐步成熟,进一步推动玻璃基底成为无源互连领域应用的最具竞争力的集成解决方案选择。

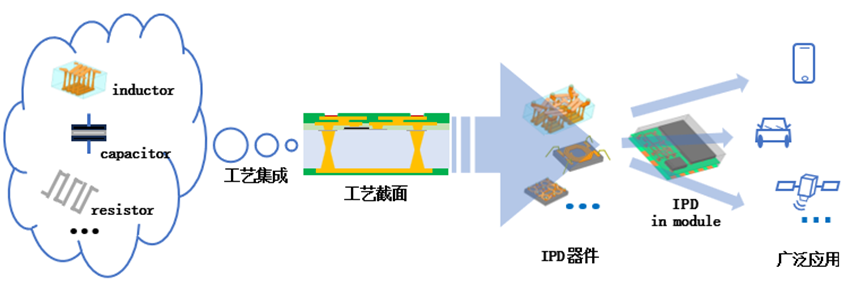

玻璃在半导体无源互连的应用内容丰富。其首当其冲的便是IPD集成无源器件应用。集成无源器件在射频,模拟,电源管理,物联网应用等等SIP模组中已经得到大规模应用。随着玻璃集成无源器件对性能和集成度的进一步提升,将获得更广泛的市场应用,帮助实现更多的无源集成化的模组方案。

玻璃集成无源器件(Glass IPD)

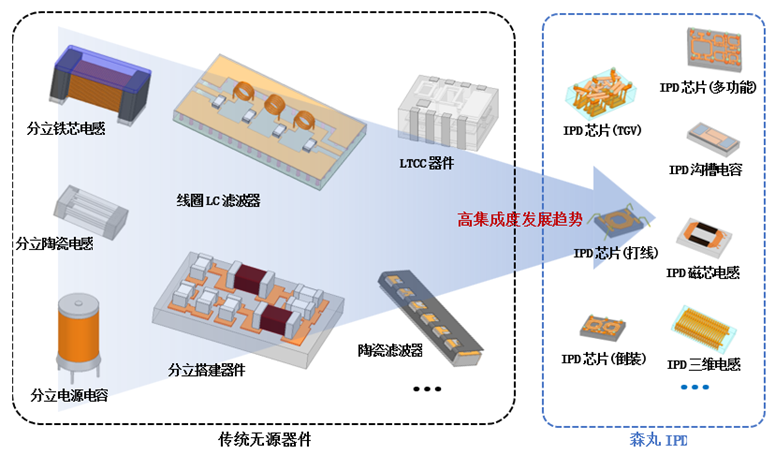

IPD集成无源器件是实现高性能小型化模组的必要条件。传统无源器件普遍使用厚膜等工艺,加工精度及器件尺寸都难以同主芯片进行共同封装应用。只有通过无源器件的小型化和芯片化,才能实现高集成度的模组。

IPD技术通过选用适合无源需求的基底材料,集合MEMS和先进封装工艺制程,半导体薄膜沉积及图形化工艺,实现无源器件的小型化。

而基于玻璃及玻璃通孔TGV的特性,则可以进一步实现更高性能和集成度的无源器件应用:例如射频器件,毫米波无源电路,射频天线,高性能电容,磁芯电感,高隔离度变压器等等。基于这些无源能力的TGV IPD工艺平台,可实现全面无源集成。下面通过一些典型器件加以说明。

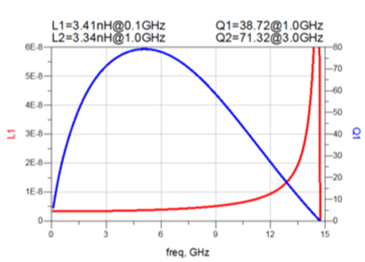

基于TGV 工艺的射频电感优势

基于TGV工艺的三维环绕螺线电感,其使用玻璃基底,绝缘性能好,损耗更低;玻璃介电常数低, 一般为Si基的三分之一,使其寄生电容效应低;另外玻璃基底本身成本较低,有经济效益优势。利用TGV可充分利用基底垂直空间,实现3D电感,通孔的截面积大,损耗低,电感Q值高,电感占用平面面积较小,集成度高。

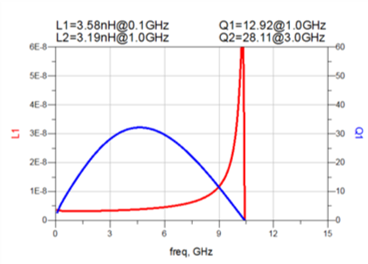

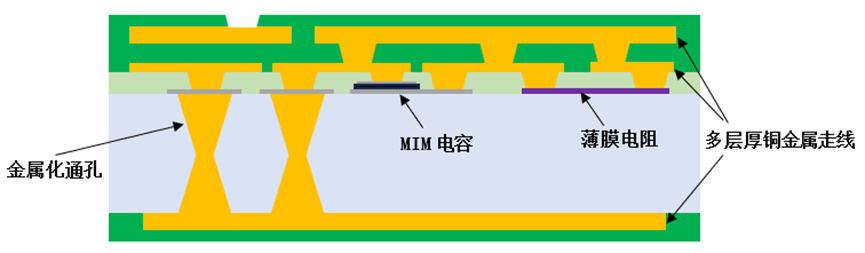

2D高阻硅IPD电感性能

TGV IPD电感性能, Q值高>50%

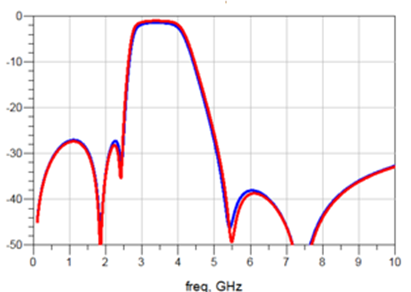

TGV IPD vs 2D IPD 滤波器性能对比,插损低>30%

基于TGV工艺的毫米波无源优势

基于TGV IPD工艺,还可应用于毫米波无源器件领域。使用玻璃基底,绝缘性能好,尤其是在毫米波频段其低损耗优势更明显。TGV IPD使用薄膜工艺,加工工艺精度高,适合高频率器件对电路尺寸精度的高要求。相对共烧陶瓷等厚膜工艺,TGV IPD金属粗糙度更低,毫米波频段下具有更低损耗表现。

基于TGV工艺的螺旋天线

使用TGV工艺也可高效率实现螺旋天线。TGV成孔工艺相对机械成孔更高精度且更可靠,可实现更紧密螺旋。玻璃基天线AiP(Antenna in Packaging)封装也是天线集成的高效率方案。

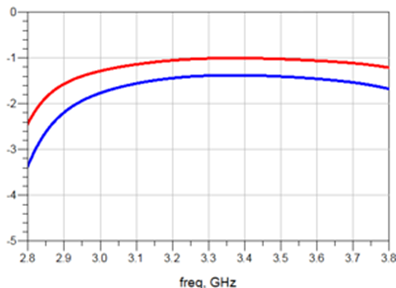

基于TGV工艺的电容

基于玻璃衬底的电容,由于其高绝缘性,可避免衬底漏电,帮助提升电容绝缘能力。下图可见Si上电容由于硅基半导体特性带来的对电容Q值性能的影响,明显低于玻璃基底的绝缘性能。另外,利用玻璃通孔,可实现背面连接,降低电感寄生。利用玻璃通孔能力还可增加表面积,实现更高的电容密度。

Glass vs Si 电容性能对比

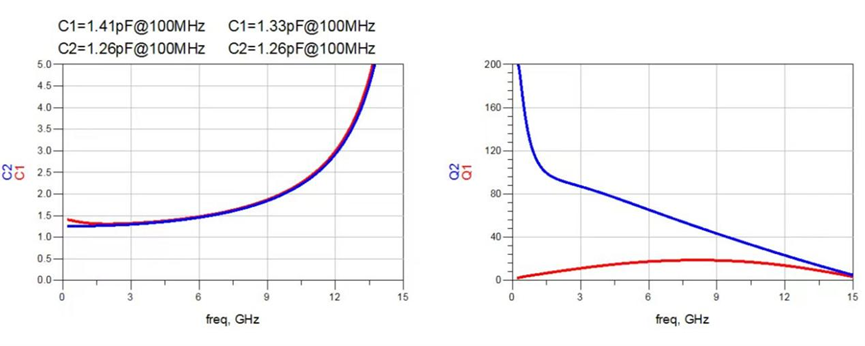

森丸电子IPD方案

森丸电子作为国内较早实现TGV通孔制备到实现产品化完整半导体工艺能力的团队,在其玻璃基底上,建立了兼有高阻硅,平面玻璃和TGV IPD的多种工艺实现平台。此平台结合了金属/氧化物/氮化物等薄膜的沉积、玻璃通孔及金属化、湿法及干法刻蚀、多层厚金属连接、深硅刻蚀、CMP抛光等工艺,并结合AOI外观检测、探针台电性能检测及各类过程检测等测试能力,实现了高精度的平板电容和高Q值电感。一个典型的森丸电子IPD工艺截面如下图所示:

森丸TGV-IPD工艺方案界面图

基于高阻硅基底的CMOS方案或GaAs基底的IPD工艺方案,需要兼顾其主平台对其他主产品工艺的需求,其工艺材料、厚度、层数等各种客观因数的限制,无法做到针对IPD集成无源器件的最优化工艺方案。

森丸IPD是专业的IPD工艺方案平台,仅针对集成无源器件需求而定制开发。森丸团队对无源器件需求的深刻理解,针对最优性能的工艺制程,兼具成本、性能、可靠性和灵活性优势,是当前IPD工艺方案中最具竞争力的平台。

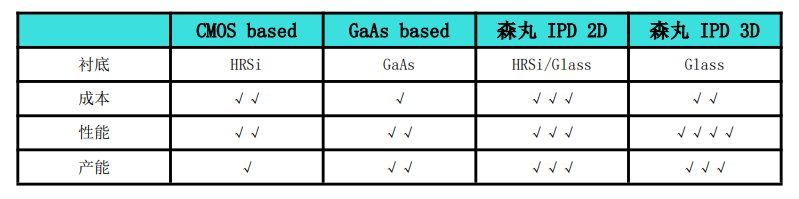

根据如下表,简略对比不同方案,仅供参考;

审核编辑:刘清

-

工艺设计套件推进创新2018-10-26 2180

-

集成无源器件的作用是什么?2019-07-31 4599

-

集成无源器件有什么优势?2019-08-02 1621

-

起浪光纤针对相干光学模块推出系列小型化EDFA产品及一站式器件服务2020-12-15 2001

-

安森美推出针对High-Q IPD工艺的设计套件2012-06-26 1385

-

基于集成无源器件和硅转接板集成方案2017-10-30 1132

-

安森美ADS软件的 High-Q IPD工艺设计套件2017-11-23 771

-

针对平板电脑的多种有源和无源器件设计方案2017-12-06 928

-

一文读懂基于IPD技术的各种无源器件2018-04-17 37215

-

凯悌推出针对多种有源和无源器件应用的平板电脑参考设计方案2018-10-13 694

-

集成无源器件的优势2019-03-12 1547

-

ADS软件的High-Q IPD工艺设计套件到底有什么作用2020-09-03 943

-

IPD滤波器与射频滤波器对比2022-11-09 5729

-

芯和半导体发布集成无源芯片IPD手册2022-11-24 2564

-

X-FAB推出新的XIPD工艺,实现全集成紧凑射频系统设计2023-11-21 1748

全部0条评论

快来发表一下你的评论吧 !