ADC的采样定理 ADC的采样过程详解

描述

今日正文

(1) ADC的硬件设计

想要保证ADC的性能能够发挥出来,在做ADC硬件设计的时候,需要注意一些事项。

从顶层看,ADC可以看作三个输入,一个输出。三个输入分别为ADC输入端的信号,ADC的时钟信号,ADC的电源输入。

所以,在设计的时候,需要控制好这三个输入口输入信号的质量。

这是硬件设计上的一些考虑项。

不过,在使用ADC之前,最好还是能够了解一下采样定理。

(2) 采样定理

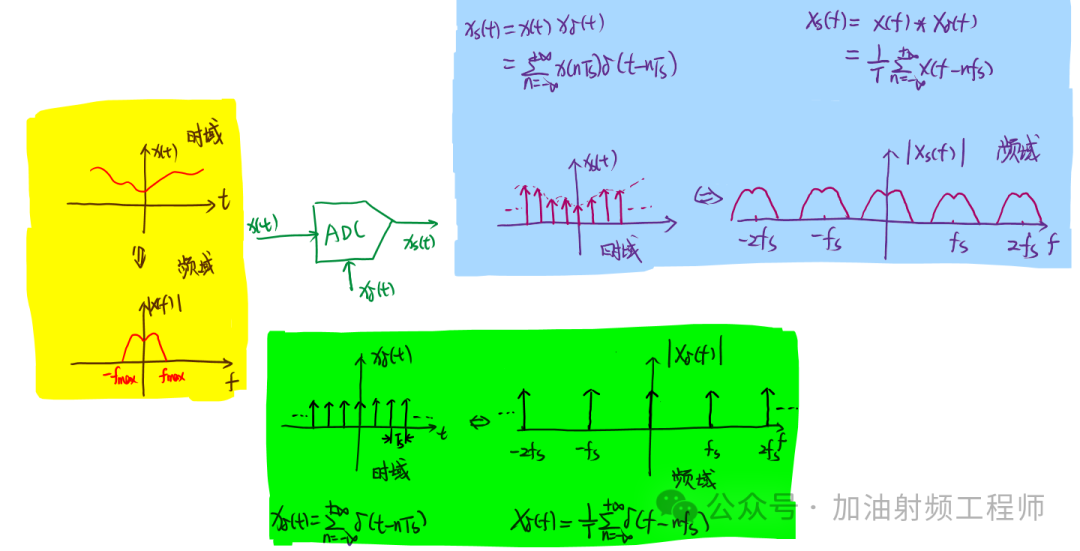

理想采样,就是用冲激函数的周期序列来对输入模拟信号x(t)进行采样,得到采样后的信号,如下图所示。

看蓝色区域的采样后的频谱,你会发现,虽然频谱每隔fs会周期性的复制,但是,采样后的频谱,在-fs/2~fs/2范围内,与原始模拟信号的频谱一样。也就是说,采样得到的数字信号保留着模拟信号的信息。

实际ADC的采样过程,可以描述为采样和保持(sampling and holding),会和理想采样有一点点差别。

(3) 过采样

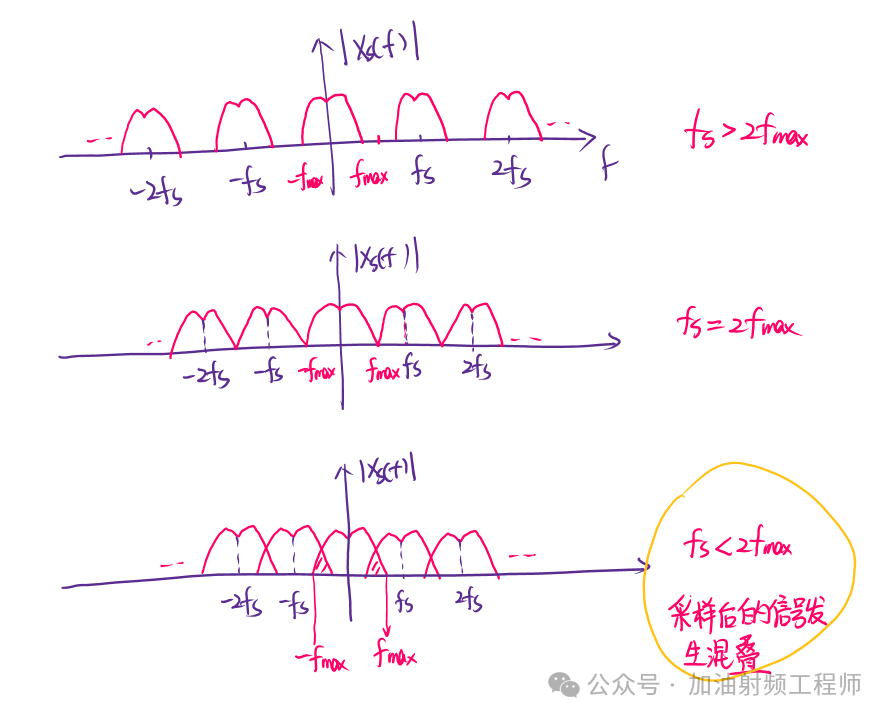

如果采样是过采样的话,采样频率需要满足fs>=2*fmax,这样的话,才能保证采样后的信号不会发生混叠,如下图所示。

所以,我们在链路设计时,需要在ADC前面加一个抗混叠滤波器,保证fs≥2*fmax。

在超外差接收机中,不管有没有镜像干扰,都需要加一个镜像抑制滤波器,ADC前面的抗混叠滤波器也有点这个意思。

不管有没有带外信号,都需要加抗混叠滤波器,因为ADC前级链路放大后的热噪声,也会混叠到带内,影响ADC的输出SNR。

(4) 欠采样

采样,除了过采样之外,还有一个欠采样。

过采样的时候,需要fs>2*fmax。欠采样,是说fs

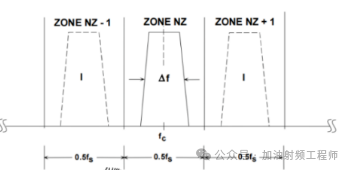

那什么是奈奎斯特域呢?

假设采样率为fs,那么DC~fs/2,称为第一奈奎斯特域;fs/2~fs,称为第二奈奎斯特域;fs~1.5fs称为第三奈奎斯特域,依次类推。

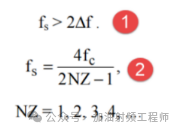

欠采样时,要求采样率能满足两个要求,即:

其实这两个条件,联合起来,就是告诉你说,你的被采样信号的频段需要在同一个奈奎斯特域上,不要超过这个域,也不要跨域,并且最好处在一个奈奎斯特域的中间。

这个靠近中间的话,抗混叠滤波器也好做一点,如果偏向一边,那对滤波器一边的抑制度,就要求太高了。

审核编辑:刘清

-

STM32 ADC的采样周期确定2012-03-22 6418

-

ADC需要采样保持器的原因及采样ADC的工作原理2021-04-28 28243

-

ADC采样过程中遇到的问题分析2022-07-22 10188

-

ADC多次采样的实现思路2022-09-09 3185

-

SAR型ADC的结构及采样过程2023-02-07 5367

-

MCU是如何提高ADC采样精度的2021-10-29 2619

-

采样定理-------------被检测信号和ADC采样率的关系?2022-05-12 11938

-

求助,关于ADC采样的相关参数问题2023-11-09 642

-

如何保护射频采样ADC的输入?2017-11-22 1582

-

主要ADC采样技术简介SAR ADC原理介绍2019-01-30 13146

-

MCU提高ADC采样精度的几种方案2021-10-25 2072

-

STM32 ADC 过采样技术2021-12-08 1561

-

adc采样率和带宽的关系2023-09-12 20927

-

ADC过采样2024-08-30 494

-

如何优化adc的采样率2024-10-31 2860

全部0条评论

快来发表一下你的评论吧 !