工程师,为什么要关注JESD204?

市场分析

描述

电子发烧友网讯:目前有一种新型的转换器接口正处于稳步上升的阶段,根据其发展形势,将来它或许会成为首选的转换器协议,那就是JESD204。这种接口在几年前就已经推出了,在经过几次改版之后,它变成了一个很有吸引力的高效转换接口。随着转换精度和速度的增强,对更高效率的接口的需求也日益增加。

JESD204不但带了来高效率,并提供了CMOS和LVDS不能满足的速度,大小和价格等优势。采用JESD204的设计不但可以体会到其可以实现高速采样率接口所带来的好处。除此之外,还可以,得益于其针脚的减少,还可以降低其封装大小,同时还可以使电路板的设计更加简便,最重要还能降低整体成本。因为这个标准是很容易扩展的,因此它还能够适应未来的设计需要。自从2006年发布以来,JESD204这个标准目前已经推出了两个版本,现行的是B版本。

随着这个标准逐渐被转换器供应商和类似FPGA制造商等用户采用,它变得更精确,同时也添加了更多的功能,这样又提高了它的效率和操作的简便性。这个标准适用于ADC和DAC,其最初的目的就是做一个基本的FPGA通用接口,或者也可以与ASIC一起用。

什么是JESD204?

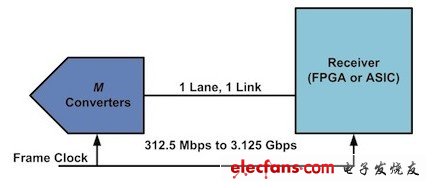

在2006年4月,JESD204的原始版本发布。这个标准被描述为一个转换器和接收器(通常是FPGA或ASIC等设备)间的千兆位级的串行数据链接。在这个原始版本,串行数据连接定义为一个转换器或者多转换器和接收器之间的单独一个串行通道。在图一用图形表示出来。展示的通道是M数量转换器和利用CML驱动的差分互连接收器与接收器之间的实体界面。连接所展现的是转换器和接收器之间已确定的串行数据连接。帧时钟指定转换器和接收器的路径,同时给JESD204设备间的链接提供时钟。

通道的数据速率定义在312.5Mbps到3.125Gbps之间,其负载阻抗定义在 。其差分电压水平定义在0.72v到1.23V之间的普通模式电压,并声称有着800mv的峰间电压。

这个链接利用包含有嵌入式时钟的8b/10b编码器,从而就不需要额外布一条时钟线,同时也免除了带有高速率传输数据的额外时钟信号复杂性调整的麻烦。随着JESD204标准的逐步采用,改进这个标准去支持带有多种转换器的不同串行通道也就变得很有必要了,这样也更能符合转换器不断增加的速度和分辨率的需要。

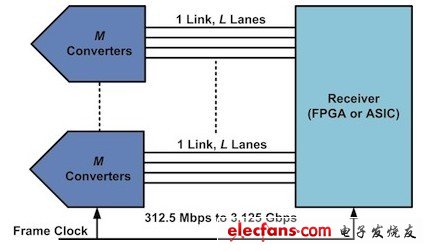

这些共识在2008年4月促进了JESD204第一个版本的推出,这也就是我们熟悉的JESD204A。这个标准的初版提供了对带有多种转换器的多样串行通道的支持。通道的数据速率仍然保持在312.5Mbps到3.125Gbps之间不变,同时也保持一样的帧时钟和电气接口规范。这个标准还增加了支持多样化的串行通道的功能,这样就能够使带有高采样率和高分辨率的转换器满足3.125Gbps的数据速率要求。图2展示了添加到JESD204A版本中以支持多种通道的的附加功能。

尽管原始版本的JESD204和改进版的JESD204A标准相对于传统的接口有着更高的性能,但仍然缺少一个关键的要素。这个缺少的元素则是链接中的连续性数据的确定延迟。

为JESD204正名

当我们使用一个转换器的时候,我们很有必要了解采样信号及其数字表示之间的时序关系。这样做就可以在接收到信号的时候在模拟区域对采样信号进行适当的重建。会出现这种情况很明显就是在进行模数转换的时候,但在数模转换的时候同样适合。这个时序关系受到定义的ADC转换器输入信号瞬时采样边缘和转换器输出数字显示之间多个时钟周期的延迟影响。同样地,在DAC,延迟定义为数字信号转换成DAC直到模拟信号输出改变的这段时间内的时钟周期的数量。在JESD204和JESD204A的标准里,没有给准确设置转换器延迟和他的串行数字输入和输出定义的功能。

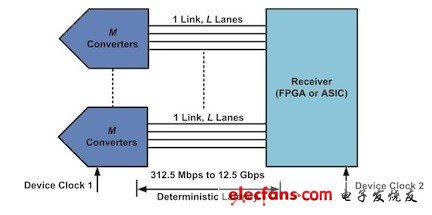

除此之外,转换器将会继续增加其速度和精度。这些要素就引出了这个标准第二个版本JESD204B的介绍。在2011年7月,第二个版本也就是现行本本的标准JESD204B推出,这个标准改进的一个管管元器件就是添加了规定去获得确定延迟,除此之外,数据速率支持逼近12.5Gbps,这就将设备分解成不同的速度等级。这个版本标准需要从用帧时钟作为时钟源到用设备作为主时钟源过渡。图3表示出了添加到JESD204B版本标准中的附加功能。

在JESD204标准的前两个版本里,没有严格规定通过接口的确定延迟。JESD204B版本通过提供一个机制、从电压升高周期到电压升高周期和通过链接再同步化,这样的话延迟就可以再重复和具有确定性。一个行之有效的方法就是通过初始化转换器初始通道的转换器排列顺序,同时及时利用一个叫做SYNC的输入信号对所有通道进行一个明确的定义。

另一个实施方法就是利用JESD204B最新定义的SYSREF信号。SYSREF信号相当于主时间基准,同时调整设备时钟的内部分配器和在每一个发射器和接收器的多帧时钟。这可以帮助通过系统确认确定延迟。JESD204B说明书介绍三个设备sub-classes:不支持确认延迟的Sub-class 0,通过SYSREF达到确认延迟的Sub-class 1和利用SYNC达到确认延迟的Sub-class 2。Sub-class 0可以简单的看做JESD204A,Sub-class 1是定位应用在运行500MSPS以上的的转换器,而Sub-class 2则只要为地狱500MSPS的转换器服务的。

除了确认延迟,JESD204B版本将其通道数据速率增加到12.5Gbps,同时将设备分为不同的速度等级。对三个速度的设备来说,源和负载阻抗都是定义在100 ? ±20%。第一速度等级从JESD204和JESD204A版本的标准校准通道数据速率,也将电气接口的通道数据速率定义在3.125Gbps。JESD204B的第二速度等级将电气接口的通道数据速率定义为6.375Gbps。这个速度等级将最小差分电压水平降到400mv的峰间值。而不是第一速度等级的500mv。 JESD204B的第三速度等级将其电气接口通道数据速率定义为12.5Gbps。这个速度把电气接口所需的最低差分电压降到360mv峰间值。随着速度等级的通道数据速率的上升,最低差分电压则相应减小,之后降低驱动器的必要转换速率会令物理实现变得更方便。

为了使JESD204B版本从帧时钟到设备时钟的过渡更具有灵活性。之前在JESD204和JESD204A版本中,JESD204系统的帧时钟是绝对帧时间基准。一般来说,转换器的帧时钟和采样时钟是一样的。当我们尝试去给多样化设备布置相同的信号,同时对不同路径这样就不能提供更多的灵活性,也有可能为尝试给多设备配置相同信号的系统设计带来不可预料的复杂性,也可以解析不同通路间的相交问题。在JESD204B,设备时钟是JESD204系统的每个因素的定时基准。每一个转换器和接收器都从时钟发生器电路获得相应的设备时钟。这就为系统设计带来更多的灵活性,但这要求指定给定设备的帧时钟和设备时钟之间关系。

为什么要关注JESD204

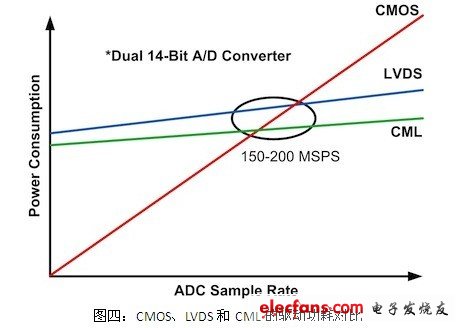

就如早几年LVDS超越CMOS成为转换器数字接口那样,JESD204在以下的几年也会走上这条道。当然,CMOS技术在这段时间内应该也是停步不前,因为它已经被LVDS全面压制了。转换器的速度和精确度及其低功耗弥补了COMS和LVDS所不能做到的。随着CMOS输出的数据速率的提升,顺便电流也会同样升高,这样就会造成高功耗。然而LVDS的电流和功率损耗都相对平稳。图四说明一个双通道14位ADC的CMOS、LVDS、CML输出的功率损耗。

总结

由于转换的速度和分辨率的增加,更高效的数字接口的需求也有所增加。行业开始实现JESD204序列化的数据接口。在转换器和FPGA(或ASIC)之间,接口规范持续发展提供了一个更好更快地传输数据。接口经历了两次修订,改善了其性能,而且能满足日益增长的需求,也带来了更高的速度和更高的分辨率转换。展望未来转换器的数字接口,很明确,JESD204有望成为数字转换器接口的行业标准。每个修订已经回答了改善其实施的要求和允许标准的发展,以满足转换技术的变化所带来的新要求。由于系统设计变得更加复杂和转换器的性能的提高,JESD204标准必定要能够适应发展的需要,以不断满足新的设计要求。

-

请问AD9683的引脚如何与zynq 7015芯片中的 JESD204 ip核端口对应相连?2018-09-05 2713

-

在Xilinx FPGA上快速实现JESD204B2018-10-16 3709

-

JESD204 v5.2约束使用生成的dcp构建逻辑计时失败2018-10-19 3144

-

JESD204不允许生成比特流2019-01-02 5233

-

JESD204接口简介2019-05-29 2672

-

JESD204标准解析2019-06-17 3392

-

JESD204评估许可证问题2020-03-11 1832

-

为什么JESD204内核不使用GTX通道绑定功能来对齐通道?2020-08-18 1439

-

为什么我们要重视JESD204?2021-04-13 1940

-

JESD204B的优势2022-11-23 768

-

AD9683的引脚如何与zynq 7015芯片中的JESD204 ip核端口对应相连?2023-12-15 907

-

采用JESD204标准的高速串行接口的应用2019-07-05 4092

-

JESD204——它是什么?2021-01-04 4421

-

什么是JESD204,我们为什么要关注它2022-12-21 5632

-

JESD204B IP核的配置与使用2025-05-24 2638

全部0条评论

快来发表一下你的评论吧 !