FSWP相位噪声分析仪测试时钟抖动测量方案

描述

随着数据传输速率的不断提升,时钟信号的抖动分析变得越来越重要。在Gb/s范围,任何一个小的抖动都会对系统性能造成显著影响。比如:高速串行链路参考时钟的稳定度会对误码率有明显影响。了解参考时钟抖动详细特性有助于在提供高数据速率的同时保证系统性能的稳定性。

此外,对于高速串行数据链路设计,准确测量以及区分由器件噪声产生的随机抖动,以及由非期望干扰产生的周期抖动,非常有助于定位抖动问题来源,提高系统性能。时钟时序抖动可以在时域以及频域进行测量。相邻周期抖动(Cycle to Cycle jitter),周期抖动(Period jitter),时间间隔误差(TIE),相位噪声(phase noise)和相位抖动(Phase jitter)等指标都可以用来衡量时钟性能,而在不同的应用背景下需要关注不同的指标。

在数字系统中,逻辑电平的切换通常伴随上升/下降沿的出现,而电平边沿的时序上的不稳定,称之为相位抖动,也叫做累积抖动(accumulated jitter),指实际的边沿与理想边沿位置的偏差。时钟抖动是相位噪声在时域的等效体现。

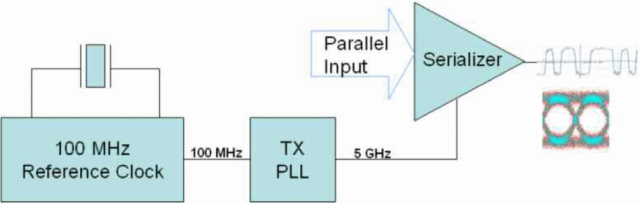

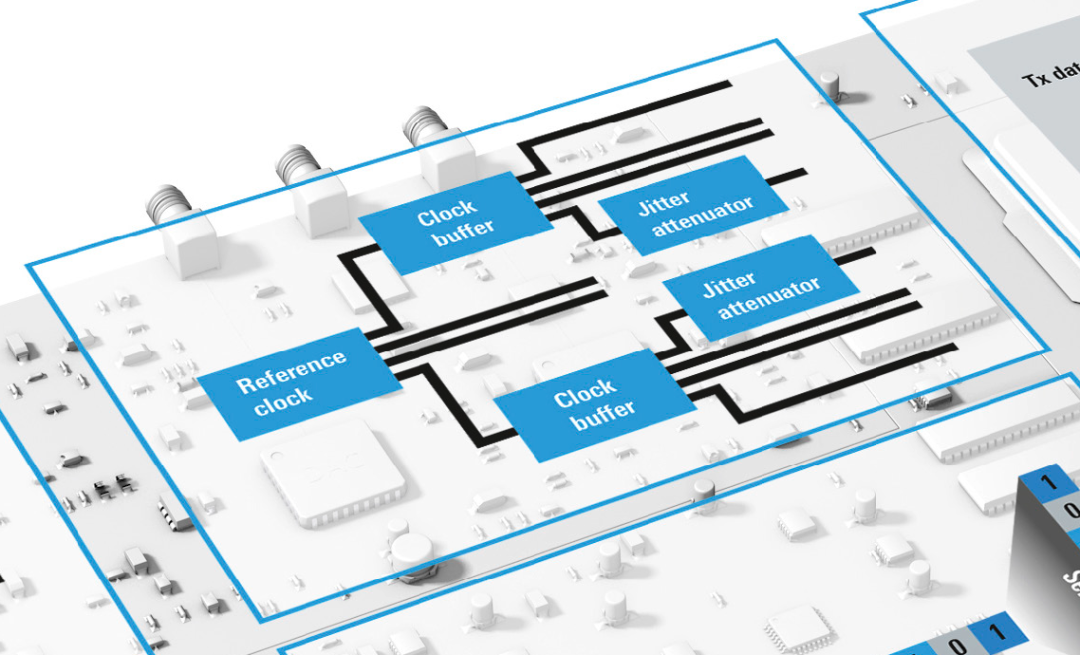

图1 典型发射机模块框图

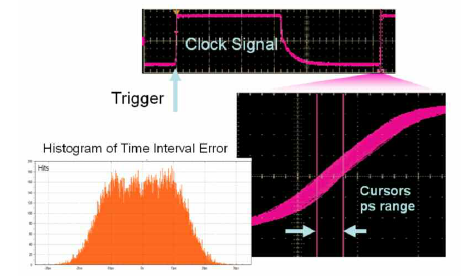

测量抖动最常用的仪表是数字示波器,测试工程师设置以时钟信号的上升或下降边沿作为触发源,而在显示屏上显示时钟的下一个上升或下降沿轨迹,打开示波器的驻留模式,可以在屏幕上观察到峰峰抖动值(Peak-Peak Jitter)。使用示波器提供的直方图功能可以观察随机抖动的统计特性。一般情况下,随机抖动直方图表现为高斯分布,而其它形式的直方图分布则有可能由确定性抖动引起。

现代高速传输直接从数据流中恢复时钟以减小抖动引入的影响。需要关注时域的分析结果,通过数字示波器的测量,获得恢复时钟,数据流或者与数据相关抖动的详细特性。但示波器自身时钟的固有抖动和模数转换器的信噪比性能限制,使得其抖动测量的最小分辨率通常在几个皮秒范围,此测量精确度越来越不能满足现代数字通信传输系统的时钟测试要求。

图2 数字示波器测量时钟抖动性能

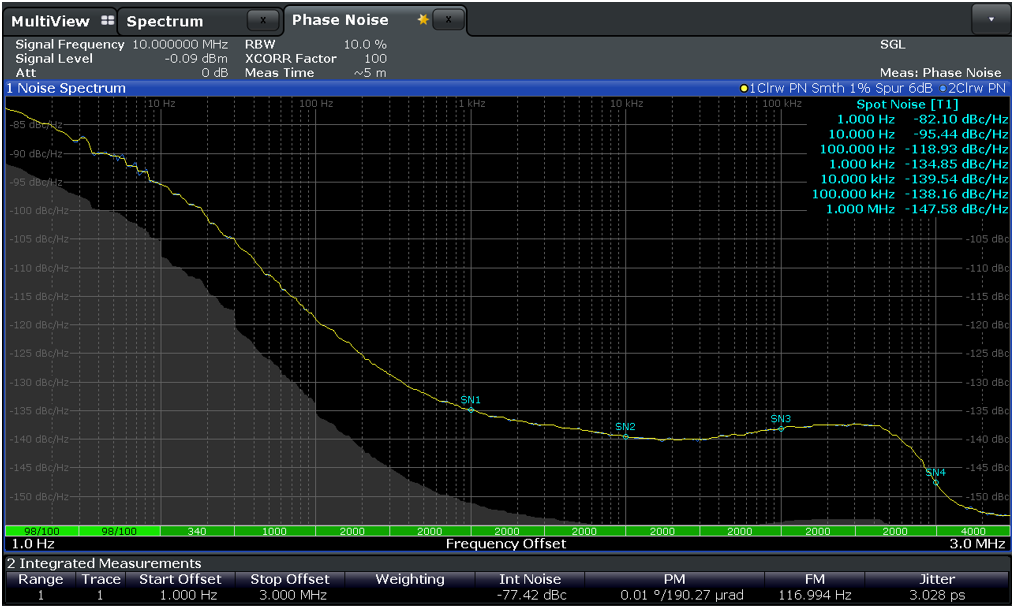

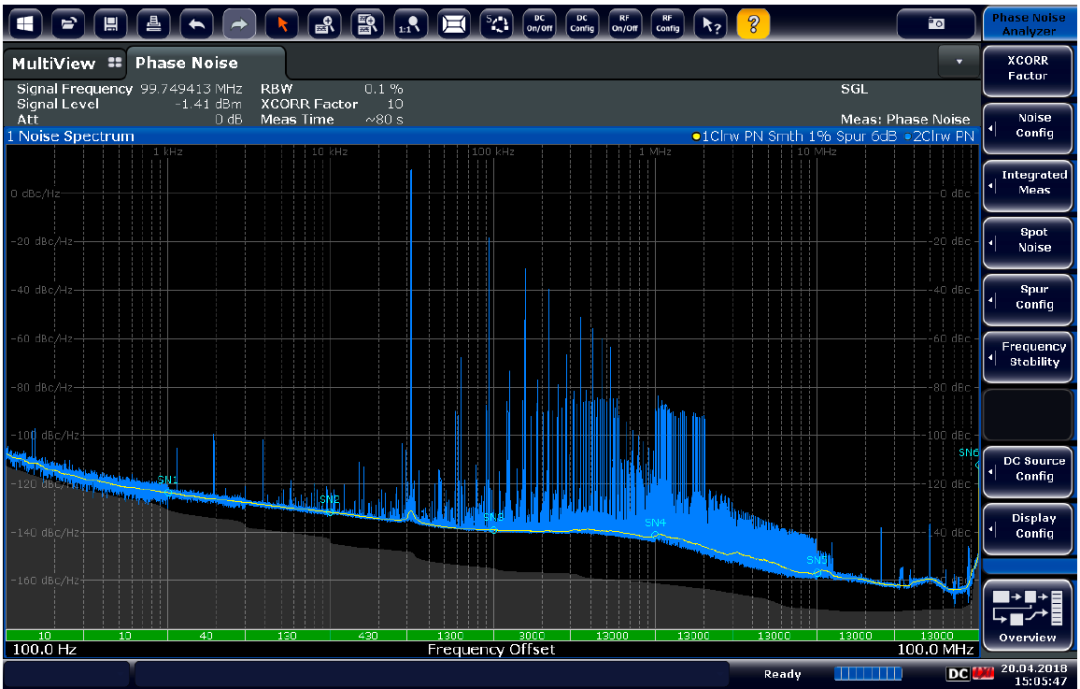

时钟信号在时域产生定时抖动,而在频域对应为相位噪声。由频域相位噪声测量结果可推导出时域的抖动性能。而且在频域测量可以很容易的区分出随机抖动和周期抖动,周期抖动在频域表现为清晰的频率毛刺,而随机抖动则表现为宽带噪声谱。使用罗德与施瓦茨公司的仪表产品,SMW200A信号源输出测量信号后,使用RTO示波器和FSWP相位噪声分析仪分别进行测量。

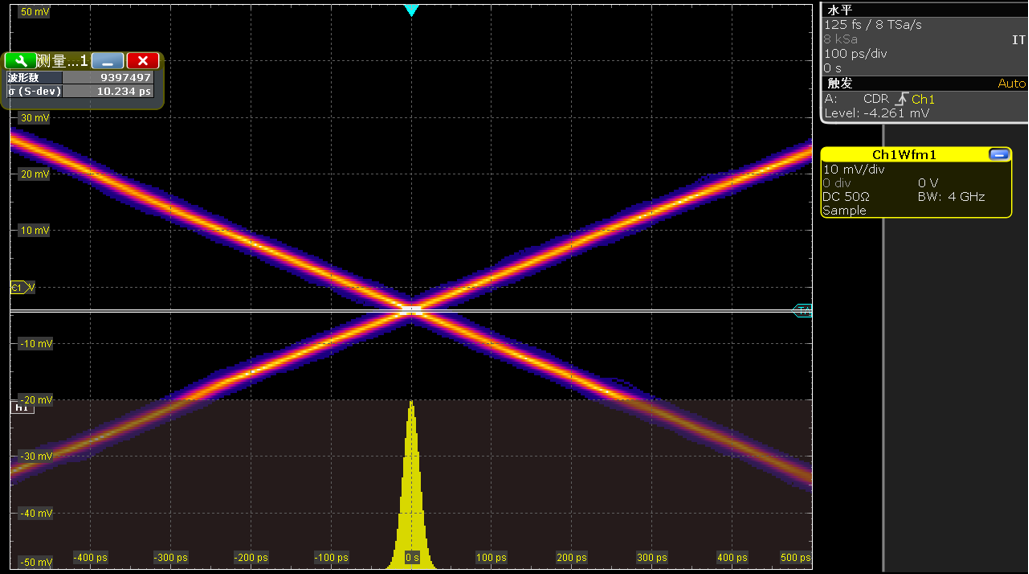

实验测试参数:SMW200A信号源产生中心载频为10MHz,信号输出功率0dBm。RTO示波器测量抖动值为10.84ps,而FSWP相位噪声分析仪测量抖动值为3.028ps,接近一致。

图4 RTO示波器测试SMW100A信号源输出信号抖动特性

图5 RTO示波器抖动测试结果10.24ps

图6 FSWP相位噪声分析仪测试SMW200A信号源输出信号抖动特性

图7 FSWP相位噪声分析仪测试抖动结果3.028ps @10MHz

实验测试参数:SMW200A信号源产生中心载频为26GHz的连续波信号,输出功率0dBm。而FSWP相位噪声分析仪测量抖动值为80.708ps。

图8 FSWP相位噪声分析仪测试抖动结果80.708fs @26GHz

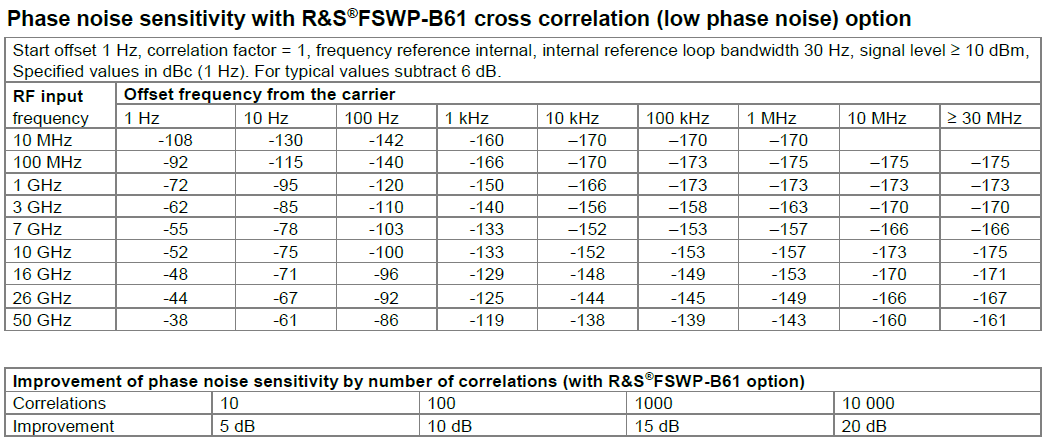

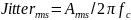

使用频谱分析仪进行测试,其使用传统方法进行相位噪声的测量,其测试动态受限于频谱分析的本底噪声和自身内部本振相位噪声性能,且近端受载波泄漏的影响较大。而FSWP相位噪声分析仪结合高性能相位噪声测试仪和频谱分析仪,测试频率范围高达50GHz,使用先进的数字锁相环方法测量相位噪声,提供互相关计算功能,可增加20dB测试动态范围。基于其自身极低的固有相位噪声和高效的杂散检测算法,FSWP相位噪声分析仪适合进行分辨率要求极高的时钟源抖动分析。

根据相位噪声分析仪FSWP提供的相位噪声动态测量指标,分析其测量抖动能力。由于指标提供的是仪表自身的相位噪声,如果被测信号具有相同的噪声能量,通常不能准确测量,在指标基础上,动态减少10dB进行抖动测量指标的估算。根据周期抖动和随机抖动的定义,计算在频偏1KHz处,由单一频率引入的周期抖动,和在频偏1Hz-1MHz频率范围内,由宽带噪声引入的随机抖动的测量指标。

图9 FSWP相位噪声分析仪相位噪声测量动态指标

由公式 可得到FSWP相位噪声分析仪测量抖动指标

可得到FSWP相位噪声分析仪测量抖动指标

(1fs = 1e-15 秒,1as = 1e-18 秒)

由推导得出的测量抖动指标可知,FSWP相位噪声分析仪FSWP在50GHz频点,可以提供1.597as的测试抖动能力。

随着高速数字设计中数据速率的提高,整个系统抖动的限制变得更加严格。这尤其适用于时钟树的各个组件,其中抖动限制可供参考时钟、时钟缓冲器和抖动衰减器甚至更加严格。由于相位噪声灵敏度高,相位噪声分析仪是这些测试的首选仪器。

图10 PCIe时钟电路抖动性能测试

测量高速数字设计中时钟的抖动变得越来越具有挑战性。例如,PCIe 5.0 使用高达32GT/s的数据速率,参考时钟的相应抖动限制为150fs(RMS)。数据引入了64GT/s的速率和100fs的抖动限制.最新PCIe 6.0 规范中的参考时钟。

相位噪声分析仪具有卓越的抖动测量基底,使其成为测量现代高速时钟抖动的理想选择。为了最大限度地减少EMI影响,PCIe、USB和HDMI等标准通常使用扩频时钟(SSC),将低频FM应用于参考时钟。由于SSC给时钟带来了额外的影响,时钟抖动也需要在SSC ON的模式下进行验证。

凭借其数字解调器架构,R&SFSWP相位噪声分析仪支持并行测量相位噪声和调幅(AM)噪声,并在相位噪声测量中提供非常高的AM抑制。该架构还支持在SSC ON 模式下测量参考时钟。该仪器还具有业界领先的相位噪声灵敏度,还可以通过R&SFSWP-B1选件添加全频谱和信号分析仪功能,以分析复杂时钟树结构中的耦合效应。

为符合PCIe 5.0 的32GT/s数据速率,总共定义了16种不同的系统传输函数。对于每一个加权抖动结果都需要低于150fs的限制。在 SSC ON模式下,在应用加权和抖动积分之前需要消除高达2MHz的SSC杂散(基波和谐波分量)。为了方便操作,可使用外部软件工具进行测试控制。该工具可自动执行数据的测量和后处理(SSC杂散去除、加权、抖动积分以及从不同系统传递函数中识别最高抖动结果)。

图11 PCIe时钟(SSC模式关闭)相位噪声和加重抖动测试

图12 PCIe 时钟(SSC模式打开)相位噪声测试

罗德与施瓦茨公司新一代的相位噪声分析仪FSWP,是专业相位噪声分析仪和频谱分析仪的完美结合,单表频率覆盖范围高达50GHz,使用此仪表测试时钟信号,不仅可以进行高精度的随机和周期性抖动性能测试,同时也可完成宽带杂散和高次谐波等频谱测试。

时钟电路设计和调试的挑战之一是缺乏可用的测试点,这使得验证电路的性能变得困难。时钟电路设计通常需要在信号路径上的多个阶段进行测量。传统上设计人员通过将射频连接器作为路径上的测试点来解决这个问题。然而随着现代设计中元件尺寸的不断缩小以及电路板上空间的限制,整合足够的射频测试连接端口以进行精确测量变得越来越具有挑战性。

为了应对这些挑战,一种潜在的解决方案是使用示波器探头。表面安装组件和印刷电路板轨道上的可用空间为连接探头尖端提供了足够的空间。通过直接探测电路,可以避免在设计的各个测试点上安装连接器的需要。然而使用示波器探头和相位噪声分析仪进行精确测量需要了解电路、探头和分析仪之间的接口。虽然分析仪的输入阻抗为50Ω,但这可能不适合许多示波器探头。现代示波器探头提供高阻抗、低电容负载和几GHz的宽带宽,使其成为使用分析仪进行RF测量的出色工具。

由于分析仪的探头接口可用,直接在电路板上进行射频测试变得可行。有源高阻抗探头可以连接到分析仪,提供实用且高精度的测量解决方案,以克服原本繁琐的射频测试问题。

图13 时钟电路

R&SRT-ZM 模块化探头系统满足高探测带宽和动态范围的需求结合低容性负载的需要。模块化探头系统可配备放大器模块提供 1.5 GHz 至 16 GHz的带宽。这些模块配有罗德与施瓦茨公司的各类探头,允许在罗德与施瓦茨分析仪上进行自动探头检测和配置的接口。模块化探头系统还提供多模式功能,使用户能够在不同模式之间切换测量模式,如单端或差分模式。

放大器配备小型化高品质高频同轴双插座SMP连接器可与各种探针模块灵活卡扣配合使用。该系统包括适用于各种测量任务和条件的探头尖端模块。包括半永久性焊料用于探测小型区域的探头尖端等。

图15 适用于R&SRT-ZM 的R&S探头前端模块

示波器有源探头具有极高输入阻抗和低电容负载的优点,通常通过宽带FET 放大器实现。探头放大器输出具有 50 Ω 阻抗,与分析仪的RF输入端口完美匹配。将有源探头与频谱分析仪结合使用的困难在于连接探头并向内置放大器供电的接口。

R&S RT-ZA9 探头适配器将 R&S有源探头的探头插头转换为标准N 型公头射频连接器。分析仪的电源和数据连接通过 Mini-USB 连接适配器。

R&S RT-ZA51 是一款探头适配器,配有R&S探头接口、USB-C连接器、3.5 mm阴头RF连接器和直流插孔。该适配器使用USB C 型连接器来供电和控制测量。该适配器附带一根短USB-C 至 USB-A电缆用于传输数据和提供电源。

总结:

使用专业的相位噪声分析仪测量相位噪声测量结果,转换得到抖动性能的方法。基于测量仪表FSWP自身出色的相位噪声高测试动态性能,提供高精度的时钟抖动测量性能。针对高速数字总线时钟测量,提供符合标准要求的测试软件,简化测试,和R&S公司的示波器探头适配,满足多种测试连接需求。

审核编辑:刘清

-

罗德与施瓦茨 FSWP8 相位噪声分析仪2026-02-28 87

-

使用FSWP相位噪声分析仪进行动态噪声系数测量2025-08-22 1009

-

罗德与施瓦茨全新FSWP相位噪声分析仪及VCO测试仪实现单表56 GHz测量能力并支持外接信号源2025-08-05 7793

-

相位噪声分析仪的技术原理和应用2024-12-13 943

-

相位噪声分析仪的基本原理和主要功能2024-05-11 3516

-

测量较低时钟频率的相位噪声和相位抖动2021-06-24 3730

-

回收罗德与施瓦茨 FSWP8相位噪声分析仪2020-05-19 1531

-

【益莱储】相位噪声测试2020-03-13 14676

-

供求二手罗德FSWP8相位噪声分析仪2019-12-14 880

-

FSW26罗德系列进口FSWP26相位噪声分析仪2019-12-13 1267

-

频谱分析仪的相位噪声2017-10-16 5450

-

R&S推出超低灵敏度相噪分析和VCO测试仪R&S FSWP2015-06-05 4686

-

时钟抖动(CLK)和相位噪声之间的转换2009-04-22 4871

全部0条评论

快来发表一下你的评论吧 !