浅析Altera公司Stratix V FPGA芯片

PLD技术

描述

电子发烧友网:本文主要为大家浅析Altera公司 28nm Stratix V FPGA。Altera公司公布了其28nm Stratix V FPGA的性能参数指标,具体参数如下表所示。该款芯片发售日期为2011年一季度。

与Altera Stratix IV及Xilinx Virtex-6对比

根据已公布的Stratix IV及刚刚公布的Stratix V,我们对于两代产品的性能参数做了一个大致比较。

| Stratix V | Stratix IV | Stratix V | |

| 逻辑单元 | 1.1M | 820K | 760K |

| 乘法器 | 可变精度 | 18*18 | 25*18 |

| 存储器 | 53Mbits | 23.1Mbits | 38Mbits |

| 串行收发 | 12.5G背板驱动、28G芯片驱动 | 11.3G*24、8.5G*48 | 6.5G*48、11G*24 |

| 工艺 | 28nm | 45nm | 40nm |

从上表我们能看到,Stratix V整体性能较之以往,得到了很大的提升。

而除了传统性能的提升之外,Stratix V还在其他方面进行了技术革新,其中包括:

嵌入式HardCopy模块:Altera公司产品及企业市场副总裁Vince Hu解释道,嵌入式HardCopy可以实现定制的IP,密度达到700K逻辑单元,可以通过用户更改硬IP实现更快的产品上市周期。Vince说:“如果重新定制硬IP往往需要12至18个月,而通过对HardCopy模块进行定制的话仅需3至6个月。”

Altera公司产品及企业市场副总裁Vince Hu

精度可变DSP模块:这次DSP乘法器较之以往的变化确实很大,毕竟FPGA的应用领域不同,对于DSP的需求也不尽相同,因此Stratix V中可为DSP设置多种精度,从9*9至54*54,并且支持浮点计算,根据Vince表示,这是业界第一个支持的厂家。

| Stratix V FPGA新功能 | 优点 |

|

——精度可变的DSP体系结构 ——集成系数寄存器和硬的预加器 ——64位DSP体系结构 ——支持浮点DSP |

效率最高、性能最好的多精度DSP数据 通路和功能,例如,FIR、FFT和浮点 |

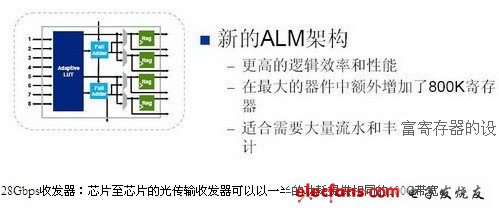

新的ALM架构:在输入端与Stratix IV并没有区别,而在后端,增加了两个寄存器,可以提升逻辑效率和逻辑性能,“由于很多ALM都被设计为寄存器,因此通过此方法会缩短编译时间,非常适合需要大量流水和丰富寄存器的设计。”Vince说。

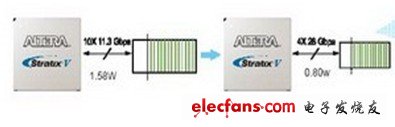

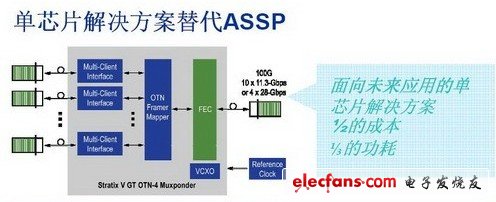

28Gbps收发器:芯片至芯片的光传输收发器可以以一半的功耗提供相同的100G带宽。

Stratix V还是延续了以往的命名规则,包括:

• Stratix V GT FPGA——业界唯一面向100G以上系统,集成28-Gbps收发器的FPGA。

• Stratix V GX FPGA——支持多种应用的600-Mbps至12.5-Gbps收发器。

• Stratix V GS FPGA——600-Mbps至12.5-Gbps收发器,适用于高性能数字信号处理(DSP)应用。

• Stratix V E FPGA——适用于ASIC原型开发和仿真以及高性能计算应用的高密度FPGA。

在硬IP上,目前Altera Stratix V FPGA已经在所有FPGA中实现了集成度最高的硬核IP,提高了器件性能,没有功耗或者成本代价。器件增强功能包括PCIe Gen3, Gen2, Gen1、40G/100G以太网、CPRI/OBSAI、Interlaken、Serial RapidIO® (SRIO) 2.0和万兆以太网(GbE) 10GBASE-R。增强了读/写通路的存储器接口包括DDR3、RLDRAM II和QDR II+。

下一代应用

| Stratix V FPGA新功能 | 优点 |

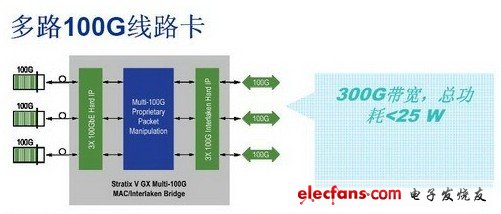

| 60个收发器工作在10.3125Gbps | 每通道135mW |

| 运行在312MHz的高性能内核构架,内核电压0.85V | 功耗比前一代低30% |

| Interlaken和100GbE的硬核IP | 与软核逻辑相比,硬核IP减少了420KL |

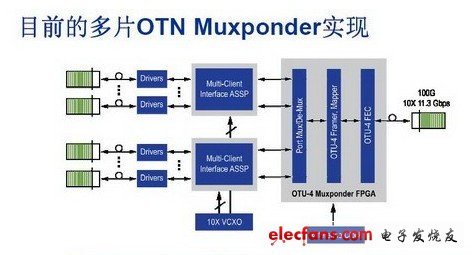

| 多客户侧ASSP | 外部VCXO | 光模块驱动器 | |

| 功能 | 多种可变数据速率和协议标准 | 客户侧通道需要10路外部时钟源 | 10路光模块驱动器 |

| 功耗 | 每个ASSP 2X 15W | 每个VCXO 10X 0.25W | 每个驱动器10X 0.3W |

| Stratix V FPGA新功能 | 优点 |

| 部分重新分配 | 替代2个多客户侧I/F ASSP,降低30W的总功耗 |

| 集成VCXO时钟电路 | 替代210个外部时钟器件,降低2.5W的总功耗 |

| 通用多协议收发器 | 节省光器件驱动器,降低3W功耗 |

-

wp02-将凌力尔特公司的DDR LVDS ADC与Altera Stratix IV FPGA接口2021-05-23 837

-

Altera Stratix V FPGA的电源解决方案2021-04-29 840

-

Altera的Stratix® V FPGA是业界唯一能提供14.1 Gbps收发器带宽的FPGA2019-05-27 1965

-

Altera Stratix V GX FPGA实现了与PCIe Gen3的兼容2013-05-23 2165

-

Pico公司提供全新Altera Stratix V PCIe FPGA模块2012-10-22 1978

-

28nm FPGA芯片-Altera 的“雄韬伟略”2012-09-19 9157

-

Altera公司 Stratix V GX FPGA开发板电路图2012-08-10 1597

-

Altera率先交付高性能28nm FPGA量产芯片2012-05-14 2745

-

Altera率先实现Stratix V GX FPGA与PCIe Gen3交换机互操作2011-12-14 998

-

28nm Stratix V FPGA突破带宽瓶颈2010-05-10 944

-

Altera推出业界带宽最大的28nm Stratix V2010-04-22 915

-

Altera Stratix IV FPGA继续广受全球媒体2010-02-24 1615

-

Altera推出面向Stratix IV FPGA的最新开发2009-12-09 1047

-

Altera Stratix IV FPGA助推XDI db2009-12-04 1018

全部0条评论

快来发表一下你的评论吧 !