工具链工具——映射与调度、模拟与验证、开发与测试工具

工具链工具——映射与调度、模拟与验证、开发与测试工具

电子说

描述

本篇文章将重点介绍工具链的工具相关知识,我们将从工具链的基本概念出发,重点介绍工具链中的映射和调度工具、模拟与验证工具、开发和测试工具,最后提出对工具链发展的展望,从而对工具链的工具进行一个较为系统的讲解。

工具链的基本概念

工具链,英文名称toolchain,通常是指在软件开发或硬件设计中使用的一系列工具和软件,用于完成特定任务或流程。这些工具一般接连地使用,从而完成一个个任务,这也是“工具链”名称的由来。

而在AI芯片领域,工具链特指连接模型算法到芯片部署的端到端系列工具。面向存算一体芯片的深度学习编译工具链包括深度学习的算法设计、前端网络的模型转换、存算一体的电路设计等模块;如今,面向传统芯片的深度学习编译工具链发展健全,而面向存算一体芯片的深度学习编译工具链在前端优化策略、后端空间映射等方面都仍有欠缺,这使得深度学习部署在存算一体芯片上移植性低、成本高,因此需要我们设计出能实现端到端的存算一体工具链及软硬件系统。面向存内计算芯片的深度学习编译工具链通常包括量化、图优化、映射与调度、模拟与验证、开发与测试等工具,前面我们已经介绍过量化和图优化相关知识,本篇文章我们将介绍映射与调度、模拟与验证、开发与测试这三种工具。

映射与调度工具

数据布局和计算任务在存储阵列中的映射至关重要,相应的工具应能智能地分配和管理数据在内存单元中的位置,优化计算效率和带宽使用;调度工具则负责在不同时刻根据资源约束安排计算操作,确保有效利用存内计算硬件的并行性和容量。在深度学习编译工具链中,映射与调度工具专门用于将高层的模型描述转换为优化的硬件指令,并调度这些指令到具体的计算资源上。这些工具通过高级优化技术来提升执行效率和硬件利用率。

下面以一些具体工具举例:

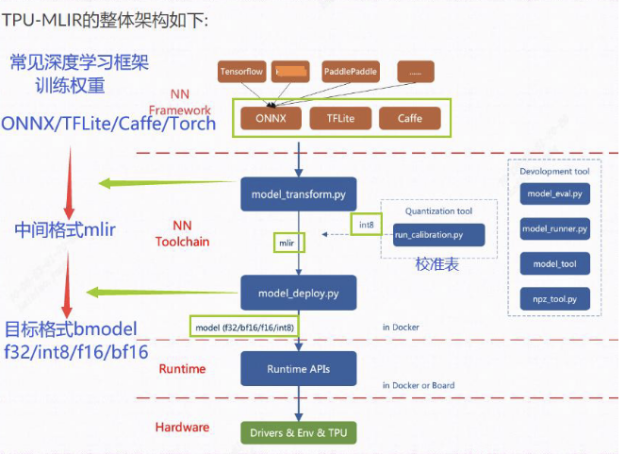

1.TPU-MLIR[1]:

TPU-MLIR是一种专用于处理器的TPU编译器。该编译器项目提供了一个完整的工具链,可以将来自不同深度学习框架(PyTorch, ONNX, TFLite和Caffe)的各种预训练神经网络模型转换为高效的模型文件(bmodel/cvimodel),以便在SOPHON TPU上运行。通过量化到不同精度的bmodel/cvimodel,优化了模型在sophon计算TPU上的加速和性能。这使得可以将与对象检测、语义分割和对象跟踪相关的各种模型部署到底层硬件上以实现加速。

图 1 TPU-MLIR整体架构[1]

2.TensorRT[2]:

TensorRT是NVIDIA提供的一个高性能深度学习推理(inference)引擎,专为生产部署优化。TensorRT提供了API和解析器,可以从所有主要的深度学习框架中导入经过训练的模型,广泛用于需要快速推理的应用场景,如视频分析和图像处理。

图 2 TensorRT logo[2]

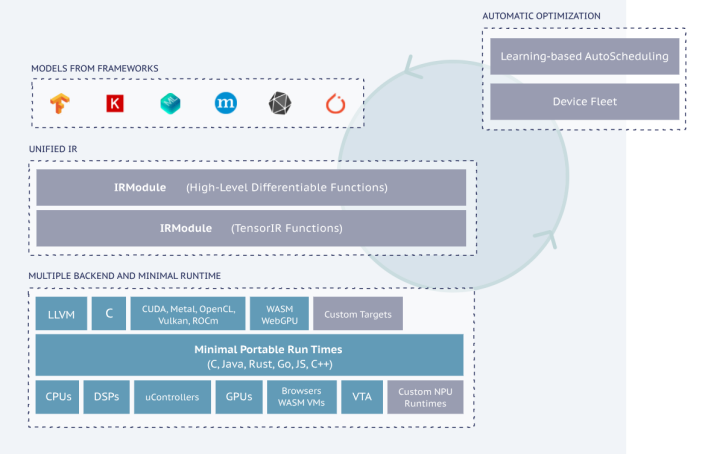

3.TVM[3]:

Apache TVM是一个端到端的深度学习编译框架,适用于 CPU、GPU 和各种机器学习加速芯片。TVM 提供以下功能:将深度学习模型编译成最小可部署的模块;在更多的后端自动生成和优化模型的基础设施,进一步提高性能。TVM支持广泛的硬件平台和前端框架,能够自动优化模型以适应不同的硬件架构。

图 3 TVM示意图[3]

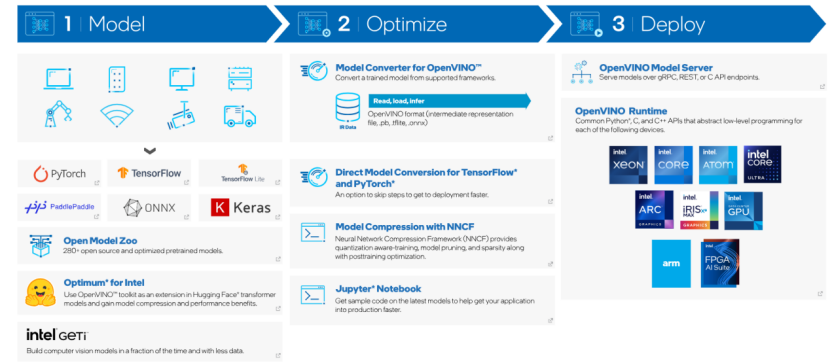

4.OpenVINO[4]:

OpenVINO是英特尔开发的一套优化深度学习性能的工具集,是一款可轻松实现“一次写入,处处部署”的开源AI工具套件,可以缩短延迟,提高吞吐量,加速AI推理过程,同时保持精度,缩小模型占用空间,优化硬件使用,支持多种类型的英特尔硬件。OpenVINO可以转换和优化使用TensorFlow和PyTorch等热门框架训练的模型,在多种英特尔硬件和环境、本地、设备、浏览器或云中部署,用于加速计算机视觉、自动驾驶等领域的深度学习推理任务。

图 4 OpenVINO原理示意图[4]

模拟与验证工具

芯片设计中,模拟与验证工具是确保设计达到期望性能和功能的关键。这些工具模拟实际操作环境,预测芯片行为,并验证设计是否符合规格,帮助发现并修正错误,提高产品可靠性和效率。

芯片设计的模拟技术可分为软件仿真和硬件仿真。软件仿真在计算机上使用仿真软件模拟芯片设计行为,不需硬件参与,常见工具有ModelSim、VCS、Virtuoso、C++或SystemC相关芯片模拟器等;硬件仿真则使用通用硬件平台FPGA或专用仿真器,提供更真实的硬件操作环境,仿真速度更快。

按流程的先后,芯片设计的模拟技术还可更细致地分为行为级仿真(功能仿真)、综合后的功能仿真、综合后带时序信息地仿真、布局布线后的功能仿真、布局布线执行后的时序仿真[5],工具链验证使用的模拟器以行为级为主。在仿真过程中,综合后门级功能仿真被称为前仿,布局布线后的时序仿真被称为后仿,前仿使用硬件描述语言描述电路逻辑;后仿在设计完成后进行,主要考虑电路物理(连线、排布、电容、电阻等)的影响。

验证技术包括形式验证和代码验证。形式验证通过数学方法证明设计正确性,不依赖测试例,常用工具有Synopsys的VC Formal;代码验证,尤其是代码覆盖分析,用来检查测试用例是否覆盖所有可能路径,帮助发现遗漏的功能区域。

对于新型的存内计算芯片,由于FPGA平台难以完全仿真其核心功能,常采用软件仿真或特定开发板如知存科技的WTMDK2101系列。而在数字芯片设计中,前端充分的逻辑仿真可避免后端问题。因此,在存算一体芯片的设计过程中,前仿和软件仿真是非常重要的内容。

下面介绍部分常用模拟与验证工具:

1. VCS:高性能Verilog仿真和调试工具,支持多种语言,适用于复杂SoC和ASIC设计验证。优势在于仿真速度快,调试方便,但仅支持Linux和Unix系统。

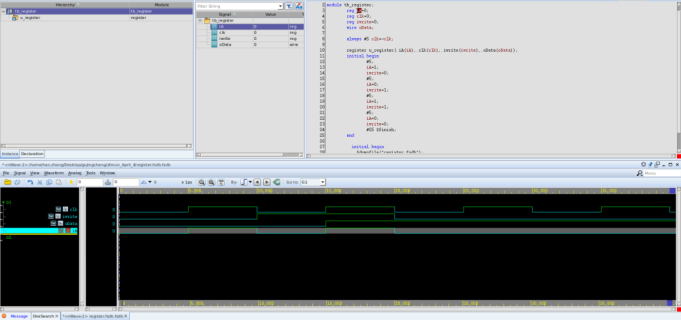

图5 使用VCS和Verdi进行仿真并查看波形的一个简单例子

2. PrimeTime:静态时序分析工具,全面进行时序性能验证,包括时序分析和功耗分析。但是该软件的操作需要相关专业知识,准确选择库文件和延时文件至关重要。

3. ModelSim:支持多种HDL语言的仿真工具,提供丰富的调试功能。优势在于友好的用户界面,但在仿真速度和性能上不如VCS。

4. Formality:形式验证工具,验证数字IC设计中功能等效性,保证设计修改不引入错误。但需要设计者熟悉设计语言版本,可能存在编程语言版本导致的兼容性问题。

5. Virtuoso:模拟、混合信号的设计和仿真工具,它为设计者提供了全面的设计和验证环境,从概念设计到芯片布局和制造的每个阶段都能得到支持。但是软件功能较为复杂,所需计算资源较大。

图6 Virtuoso用户界面

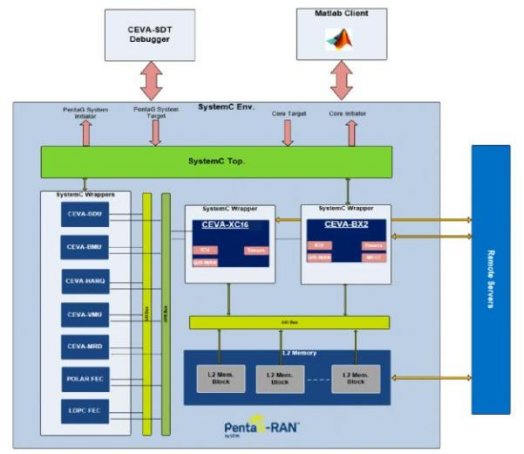

CEVA SoC:作为一种编程语言,SystemC可用于将硬件和软件描述指定为抽象行为模型。SystemC还提供事件驱动型仿真接口,开发人员可以通过该接口模拟并发进程。即使尚未设计系统的某些部分,开发人员也可以为SoC仿真生成完整系统的可执行模型。CEVA SoC模拟器提供集成SystemC仿真环境,允许系统工程师、架构师和软件开发人员在硅前阶段进行建模、分析和调试。该虚拟模拟器可用于架构定义和快速原型设计,并可用作有效的IP评估和概念验证 (PoC)工具。它能够与MATLAB无缝对接,以便用于开发算法和测试。CEVA客户可以在FPGA平台上模拟他们的系统以进行最终验证[6]。

图 7 CEVA SoC模拟器示意图[6]

开发和测试工具

芯片设计中,我们也需要一套完成的开发与测试工具,包括集成开发环境(IDE)、代码编辑器、单元测试和集成测试工具在哪的各种工具等等。前序的模拟与验证阶段主要聚焦于设计的准确性和功能性,包括功能验证、时序验证、形式验证等等;而开发和测试阶段更侧重于设计的实现与测试,包括编码、布局布线、各种测试来确保设计的正确性和性能。

下面介绍部分常用的开发和测试工具:

1. Synopsys IO Complier II:主要应用于物理综合,包括布局布线等相关功能,可实现和优化IC的物理布局,Cadence virtuoso、Mentor Graphics Calibre等软件也有能实现进行物理设计和布局的相关功能。

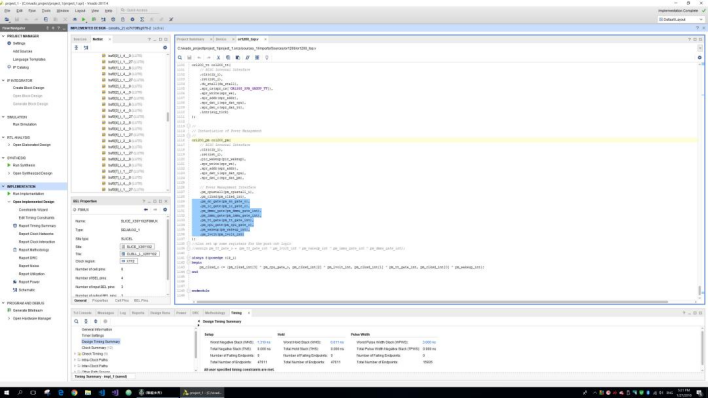

2. Xilinx Vivado:用于FPGA的设计和综合,提供全面的开发环境和工具支持,可将逻辑设计映射到FPGA架构上,并生成可下载到FPGA器件的比特流文件。

图8 Vivado开发界面

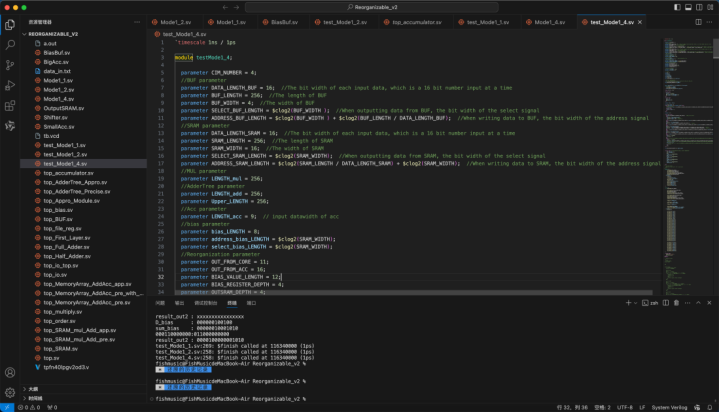

Vim、Emacs、VScode+iverilog:常用的代码编辑器,常用于编辑硬件描述语言Verilog、VHDL等等。

图9 Vscode与iverilog联动编写硬件描述语言

4. Cadence Palladium Emulator:用于大规模集成电路验证。

5. Synopsys ZeBu:用于硬件/软件共同验证或验证加速。

6.Mentor Graphics Veloce Emulation Platform:用于验证SoC设计。

7.Witmem studio:由知存科技开发的一款全功能集成开发环境,包含客户识别的SDK推送功能,SDK包自动更新下载安装功能,内核自动识别语法高亮编辑器,面向不同功能的个性化工程创建功能,以及常规IDE所具有的项目工程管理、文件编辑、编译、调试等功能,可在知存科技官网进行软件下载[7]。

图10 Witmem Studio开发界面

8.其他工具:Tcl/TK、Python等用于自动化测试和脚本编写的软件。

总而言之,为推动存内计算规模应用,工具链的发展壮大将成为存内计算芯片设计中的必然诉求,它们需要业界共同发力,共同搭建面向存内计算的映射与调度、模拟与验证、开发与测试工具链。相信在不久的将来,存内计算芯片相关工具链将迎来井喷式发展,让我们一同分享、一同创造,一起见证存内计算芯片的生态繁荣时代。

参考文献:

[1]编译器:TPU-MLIR环境构建及使用指南(一) - 江左子固 - 博客园 (cnblogs.com).

[2]使用 NVIDIA TensorRT 加速深度学习推理(更新) - NVIDIA 技术博客.

[3]Apache TVM中文站(tvm.hyper.ai).

[4]英特尔® 发行版 OpenVINO™ 工具套件 (intel.cn).

[5] FPGA中的五个级别和五种仿真(blog.csdn.net).

[6]CEVA SystemC 模拟器:出色的 SoC 模拟器 - 与非网 (eefocus.com).

[7]知存科技存内计算芯片开发者中心(witintech.com/develop.php).

审核编辑 黄宇

-

基于模型的动态测试工具TPT2023-02-20 1812

-

嵌入式软件测试与专业测试工具的必要性深度解析2025-09-28 4686

-

并口开发调试工具包2009-05-26 746

-

并口开发调试工具包 (推荐)2009-05-27 839

-

TD-SCDMA测试工具体系及应用2010-08-02 929

-

汽车CAN/LIN总线测试流程和测试工具解析2010-03-19 8987

-

TCP/UDPDbg测试工具2015-10-26 2840

-

串口调试工具2015-11-20 1936

-

渗透测试工具开发2017-09-07 1273

-

常用的软件测试工具有哪些_10款常用的软件测试工具推荐2018-04-24 77563

-

自主开发的MIL测试自动化测试工具2020-10-23 9499

-

常用串口通信测试工具sscom2022-06-07 1983

-

总线测试工具CANOE的使用指南2022-10-10 8066

-

APK渗透测试工具:AppMessenger2022-11-18 4043

-

Web端TCP/UDP测试工具!小白必学~2025-01-08 2456

全部0条评论

快来发表一下你的评论吧 !