存内计算——助力实现28nm等效7nm功效

存内计算——助力实现28nm等效7nm功效

电子说

描述

算力是数字经济时代的核心生产力,并且近年来需求剧增。而我国当前的算力供给上仍面临巨大的挑战,一方面,国外的高端算力芯片被美国禁售,另一方面,国内的芯片产业仍处于发展阶段[1]。如何获取算力提升,成为当前时代芯片研究的重要命题。

一.算力突破

研究如何获取算力提升,要从算力的来源上考虑。芯片算力可大致总结为以下计算公式:

因此,获取算力提升的主要切入点是晶体管密度、芯片面积、单位晶体管的算力,这三个方面分别主要涉及制作工艺、光刻口径、计算架构。

(1)晶体管密度:

晶体管密度的主要影响因素是制造工艺、基板材料,同样的面积内,封装的可用晶体管越多,就能提供越强的算力。

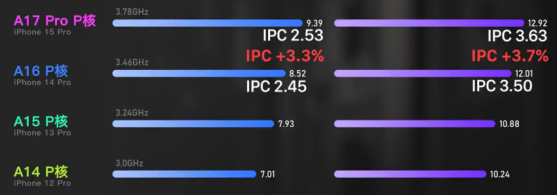

制造工艺方面,受限于美国的无理封锁,当前国内量产芯片的最先进制造工艺为14nm,国际上量产芯片最先进的制造工艺为3nm。清华大学尹首一教授认为,国内芯片制造工艺将长期处于在14nm,国内芯片产业与研究不能指望通过制造工艺获得性能提升。在国际领域,虽然芯片制造商仍能享受到制程工艺带来的升级,但从苹果A17 Pro芯片的性能表现、高通仍然采用基于4nm的升级工艺制造今年旗舰芯片的市场行为来看,产业界最先进的工艺制程已经不及预期。

基板材料方面,随着制造工艺步入埃米级别,芯片制造工艺受到硅原子性质的影响越来越大,产业界和学界也在探索新的材料用于制造芯片,通过“弯道超车”的方式提升晶体管密度,比如英特尔等厂商正在研发的玻璃基芯片[3]、北京大学彭练矛教授团队正在研发的碳基芯片[4]。

(2)芯片面积

芯片面积和晶体管密度考虑的是类似的问题,在一颗芯片内提供更多的可用晶体管,就意味着能提供更多的算力。但是在当前,GPU的单芯片面积基本已经达到上限,想通过面积获得进一步的算力提升,可以从拓展角度考虑,有两个探索的方向:平面拓展和垂直拓展。

平面拓展就是在光刻时使用光照拼接技术,实现两个曝光区域的物理连接,来把芯片做大,通过计算架构的优化设计,保证晶圆中晶体管的可用性,Cerebras公司和Tesla公司已经实现了晶圆级芯片。垂直拓展就是把芯片或其中的部分器件三维堆叠起来,如AMD的3D缓存技术。

(3)单位晶体管提供的算力:

单位晶体管提供的算力和计算架构息息相关,计算架构的优化改进或使用新的计算架构,能够对芯片算力产生更根本的影响。计算架构上面临的主要问题有:基本器件的设计架构不同导致的晶体管数量不同,需要探索更优的基本器件结构设计;冯诺依曼架构的“存储墙”导致的访存瓶颈,限制了算力的发挥,需要降低带宽对算力的限制;功耗限制导致的dark select问题,即为了保证芯片功耗,不能同时点亮芯片上的所有晶体管,需要优化设计来避免。

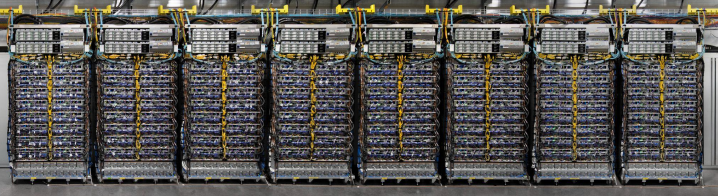

面对以上的部分问题,产业界和学界已经给出了相应的解决方案。在计算架构的优化方面,有数据流、可重构、存算一体三条路径。首先,数据流芯片尝试不使用指令而是直接通过数据驱动计算,避免外部存储访问,来解决晶体管利用率低的问题。Google的TPU芯片已经证明了,这种方式虽然在单芯片性能上逊于GPU,但能在系统级算力上实现超越[1]。具体来讲,单核TPU v4的性能是低于A100 GPU的,只有它的88%,但1024颗TPU v4的集群性能,超过了A100 GPU的集群性能,最高达到了1.96倍。4096颗TPU v4芯片示意图如下图3所示。

图 3 4096颗TPU v4芯片集成[6]

可重构芯片尝试在芯片内布设可编程的计算资源,根据计算任务的数据流特点,动态构造出最适合的计算架构,国内团队设计并在12nm工艺下制造的CGRA芯片,已经在标准测试集上实现了和7nm的GPU基本相当的性能。存算一体尝试通过集成存储和计算在一个芯片甚至一个容器内,来突破访存限制,发挥芯片的最大算力。下面我们将重点介绍存算一体技术。

二.存算一体

存算一体是一种新型计算架构,直接利用存储器本身进行数据处理,从根本上消除数据搬运,实现存储与计算融合一体化,成为后摩尔时代集成电路领域的重点研究方向之一。

(1)存算一体技术优势:

存算一体技术具有很大的优势,存算融合的特点使其天然具备较大算力、低延迟、高带宽等优势。相比传统架构,存算一体大算力芯片不仅仅是能效比有数量级的提升,更重要的是将大大缓解存储墙问题,简化AI服务器集群的互联网络及其管理和各类成本,包括高速互联、DPU和能耗等。因此,存算一体技术是实现芯片算力突破的重要途径,可助力实现28nm等效7nm功效。

(2)传统工艺芯片算力提升实例:

目前已有一些企业和高校,通过存算一体技术,实现28nm制程芯片的能效算力提升。

忆铸科技于2021年10月于上海成立,是一家基于ReRAM设计和落地数字存算一体芯片的企业。在公司的技术畅想中,他们尝试将新型忆阻器、存算一体架构、Chiplet技术、3D封装等技术结合,实现大算力、高能效比的芯片。据其官网信息,亿铸第一代算力芯片采用的工艺为28nm,其能效比可以实现目前主流算力板卡的10倍以上[7]。

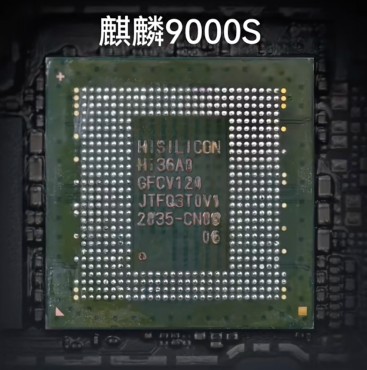

2023年8月29日,华为的麒麟9000s芯片随着Mate 60 Pro成功发布,该款芯片一经发出,就引发业界讨论:“麒麟9000s的工艺制程究竟是多少?”在2023年中国集成电路设计业(ICCAD)年会上,清华大学魏少军教授在演讲中提出:“能够用14nm,甚至28nm做成7nm的产品性能才是真正的高手”。据悉,华为并未公布麒麟9000s真正的工艺制程,知名科技解析机构TechInsights对麒麟9000s深入解析结果显示,该芯片确实拥有7nm工艺制程的特性。

图 4 华为麒麟9000s芯片

知存科技的WTM2101量产芯片采用40nm制程,将神经网络部署在芯片中,已经实现了满足端侧算力需求的语音识别等功能。即将量产的WTM8芯片,采用28nm制程,作为新一代存内AI计算视觉芯片,能够实现图像的AI超分、插帧、HDR识别和检测这样复杂的功能[8],现有的一些研究也已经证明存算一体可以实现16bit、32bit的浮点计算,具备进入高算力芯片的能力。

图 5 知存科技WTM-8系列芯片示意图

三.未来展望

随着工艺的进步,先进工艺制程已从28nm发展至3nm,苹果新发布的A17Pro已采用了tsmc 3nm工艺。据悉,tsmc也将投资近万亿新台币建造1nm晶圆厂。在未来,有没有一种全新的方案解决算力不足、工艺制程发展空间受限的局面?存算一体便是答案之一。

综上所述,存算一体技术因为其特殊优势,可以大大提升芯片算力,从而使得成熟28nm制程芯片能够实现等效于7nm制程芯片的性能。当然这其中还有很多难点需要突破,需要科研工作着的不断努力,期待未来基于存算一体技术的芯片可以更好地突破芯片制程的限制。

参考资料

[1] 尹首一教授报告:以“架构”创新,突破算力卡脖子问题.

[2] 极客湾 space.bilibili.com/25876945.

[3] 第八届未来芯片论坛中英特尔中国研究院的报告.

[4] 北京大学新闻网:专访北大碳基芯片团队:我们换道走了20年,觉得能走下去 (news.pku.edu.cn).

[5] AMD官网 amd.com.

[6] Jouppi N, Kurian G, Li S, et al. Tpu v4: An optically reconfigurable supercomputer for machine learning with hardware support for embeddings[C]//Proceedings of the 50th Annual International Symposium on Computer Architecture. 2023: 1-14.

[7] 忆铸科技官网 (yizhu-tech.com).

[8] 知存科技官网(witintech.com).

[9] 从7nm到5nm,半导体制程 - 吴建明wujianming - 知乎(zhuanlan.zhihu.com/).

审核编辑 黄宇

-

Altera 28nm FPGA助力NEC提升LTE基站性能2013-11-19 1018

-

什么是Altera最新28nm FPGA技术?2019-08-21 3127

-

如何利用28nm高端FPGA实现功耗和性能的平衡?2019-09-17 2915

-

10nm、7nm等制程到底是指什么?宏旺半导体和你聊聊2019-12-10 10351

-

请问C2000系列产品的制程是45nm还是28nm?2020-06-17 2157

-

Fusion Design Platform™已实现重大7nm工艺里程碑2020-10-22 2380

-

请大神解释一下28nm下是没有MIM电容了吗?2021-06-24 3024

-

求一份tsmc 7nm standard cell library2021-06-25 3223

-

从7nm到5nm,半导体制程 精选资料分享2021-07-29 8365

-

28nm Stratix V FPGA突破带宽瓶颈2010-05-10 1064

-

降低赛灵思28nm 7系列FPGA的功耗2012-03-07 742

-

半导体制程发展:28nm向3nm的“大跃进”2020-10-15 6970

-

22nm和28nm芯片性能差异2022-06-29 12451

-

7nm芯片和5nm芯片哪个好2022-07-05 25530

-

所谓的7nm芯片上没有一个图形是7nm的2024-10-08 1739

全部0条评论

快来发表一下你的评论吧 !