深入阐述全球首款异构3D FPGA芯片

PLD技术

描述

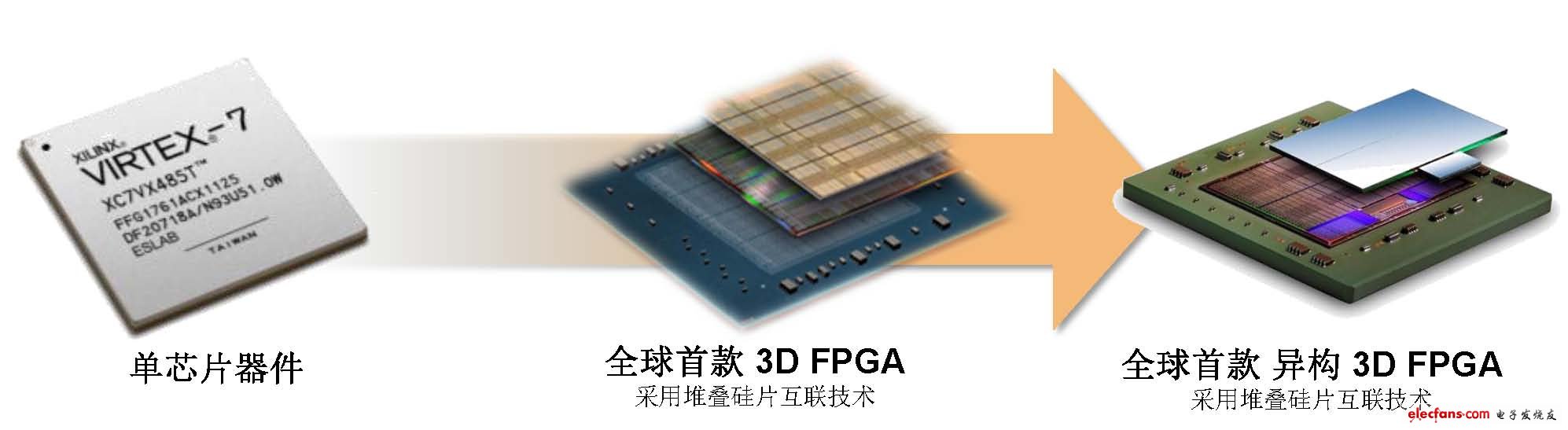

核心提示:不久前,赛灵思公司(Xilinx:All Programmable技术和器件的企业) Virtex-7 H580T FPGA—全球首款3D异构All Programmable芯片正式发货。本文将为大家深入阐述此款3D异构All Programmable芯片。

Virtex-7 HT采用赛灵思的堆叠硅片互联 (SSI)技术,是提供业界带宽最高的FPGA,可提供多达16个28Gbps收发器和72个13.1 Gbps收发器,也是能满足关键Nx100G和400G线路卡应用功能要求的单芯片解决方案。

为此,本文就赛灵思一些问题进行了深入讨论,具体问题和相应答案如下:

问:为何28 Gbps收发器是40nm工艺,而不是28nm或65nm?

答:异构架构的优势使我们能够把不同的技术结合在一起,从而能够提供针对客户需求儿和优化的器件。就 Virtex-7 H580T 器件而言,我们选择了在 40nm 技术节点上已得到检验的成熟的收发器技术。

问:Virtex-7 HT FPGA为何称为all programmable器件?还是Xilinx今后所有7系列及以上的产品都称为all programmable?

答:我们还没有正式做出用词的改变,但“All Programmable”这个用词反映出了一个事实,那就是FPGA 这个词已经不能全面充分地描述当前可编程器件产品了。我们的产品已经超越了传统的可编程逻辑,已经不再是简单的门阵列了。尤其对28nm工艺节点而言,赛灵思开发了许多不同类型的可编程技术;超越了可编程逻辑和I/O,包括了软件可编程ARM 处理系统、3D-IC、模拟混合信号 (AMS)、IC 设计工具以及IP 等。

赛灵思将可编程技术的这些不同子集整合为All Programmable器件,如Virtex-7 2000T和Virtex-7 H580T SSI器件以及最新发货的Zynq-7000可扩展处理平台 (EPP),此外还包含带有大量模拟混合信号(AMS)、高性能SERDES、PLL到可编程数据转换器资源的FPGA。

问:新闻稿[1]中,“赛灵思公司有线通信系统架构师Mark Gustlin指出:‘Virtex-7 H580T具有8个28 Gbps 收发器和更大的逻辑容量,……’”,而开头又提到:“可提供多达16个28 Gbps收发器 ”。到底是8个、还是16个28Gbps收发器?

答:新闻稿的第一段提到了整个产品系列,共包括三款器件:Virtex-7 H290T、Virtex-7 H580T 和 Virtex-7 H870T。Virtex-7 H870T 采用 16 个 28Gbps 收发器和 72 个13.1 Gbps 收发器,是产品系列中带宽最高的器件。两个带宽较低的器件均采用 8个 28Gbps 收发器,但分别采用 24 个和 48 个 13.1Gbps 收发器。

问:Nx100G和400G线路卡市场如何?何时会开始研发和大量部署?

答:赛灵思在本领域的研发工作已经开展了一段时间。

通信设备OEM厂商面临着加倍设备密度,同时确保功耗不变,降低成本的压力。相对CFP光学模块而言,CFP2光学模块可支持下一代100-400Gbps系统的设计,最大化面板带宽密度,同时又不增加尺寸和功耗。

为支持更高带宽,需要将SEREDES数据速率从10Gbps提升到28Gbps。在赛灵思的Virtex-7 HT FPGA(包括Virtex-7 H290T和Virtex-7 H870T器件)的开发过程中,芯片到光学模块、芯片到背板以及芯片间接口的抖动预算异常严格,与功耗一起成为了关注的焦点。

使用400Gbps线路卡的客户希望在输入侧加入包括16个28Gbps的单芯片解决方案,以连接4个 400Gbps CFP2光学模块。系统还要求用48~72个10.3125 Gbps收发器连接多个速率为 200Gbps或400Gbps的NPU或ASIC。除了采用16个28Gbps收发器的Virtex-7 HT之外,赛灵思还将针对100Gbps、2 x 100Gbps应用提供采用4或8个28Gbps 收发器的器件。

-

详解赛灵思异构 3D 技术2012-07-06 1498

-

全球首款异构融合类脑芯片备受世界关注2019-08-10 2360

-

中国传动网:全球首张3D打印唱片发布 歌声也可3D打印2013-12-17 2939

-

华硕推出全球首款NVIDIA 3D笔记本2009-12-03 1552

-

全球首款3D视效笔记本Aspire 5740DG热辣劲销2010-03-31 614

-

友达发表全球首款全视角裸眼3D面板2010-11-04 1120

-

全球首款2D/3D视频转换实时处理芯片:DA82232010-12-14 5726

-

赛灵思正式发货全球首款异构3D FPGA2012-05-31 1099

-

赛灵思正式发货全球首款异构3D FPGA 再次刷新FPGA行业的历史2012-06-18 748

-

全球首款工业级硅胶3D打印机 灵活性极高2016-11-22 3982

-

索尼推出全球首款头戴式3D OLED 显示器2019-01-07 888

-

当芯片变身 3D系统,3D异构集成面临哪些挑战2023-11-24 2314

-

3D异构集成与 COTS (商用现成品)小芯片的发展问题2023-11-27 1880

-

中兴通讯发布全球首款5G+AI裸眼3D平板2024-02-28 1595

-

紫光展锐助力全球首款AI裸眼3D手机发布2024-07-15 1977

全部0条评论

快来发表一下你的评论吧 !