如何使用GaN HEMT抽取Self-heating效应和Trapping效应模型参数?

描述

氮化镓(GaN)技术在5G基站、卫星通信和其他应用中的迅速普及提高了晶体管建模的门槛。尤其是,在最新版本的ADS中支持ASM-HEMT 101.4和MVSG_CMC 3.2.0 GaN HEMT模型。对于器件建模工程师,如何准确地抽取这两个效应的模型参数往往是一个挑战,今天来介绍一下使用IC-CAP中GaN HEMT模型参数抽取包如何抽取Self-heating效应和Trapping效应模型参数。

GaN器件的标准模型

通过对业界GaN模型的验证筛选,Compact Model Coalition (CMC)选出ASM-HEMT和MVSG_CMC作为GaN器件的标准模型。

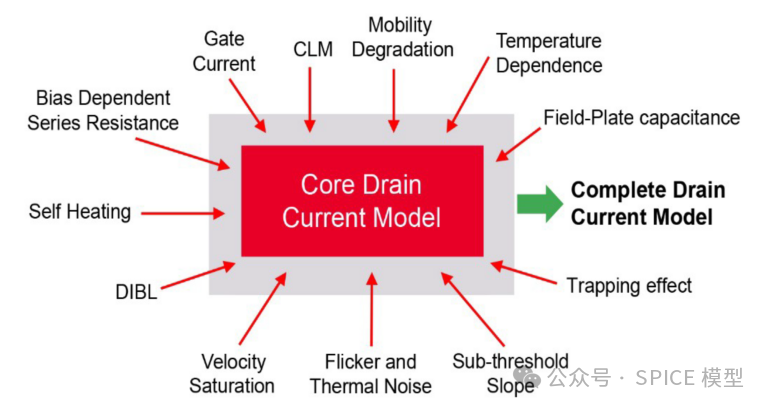

ASM-HEMT是一个计算效率高,基于表面势的电流和电荷模型,考虑了各种二次器件效应,包括Self-heating和Trapping等效应。

MVSG_CMC (MIT Virtual Source GaNFET Compact Model Coalition) 是一种基于电荷的模型,具有多种场板电流和电荷模型可供选择。它还包括Leakage、Noise、Self-heating和Trapping等效应。

这两种模型都提供了GaN器件行为的模拟,适用于频域和时域的精确模拟。它们都使用带有热阻和热容的R-C网络来模拟Self-heating效应。两者还提供了各种Trapping场景的参数选择,包括最新版本的R-C网络模型,其中包含可变drain-lag和门gate-lag。

Self-heating模型参数抽取

GaN器件的功率密度增加,使自热集中在更小的区域,降低了迁移率,增加了信号延迟,并可能缩短器件的使用寿命。使用IC-CAP提取自热参数对于ASM-HEMT或MVSG_CMC GaN HEMT模型都是相似的。

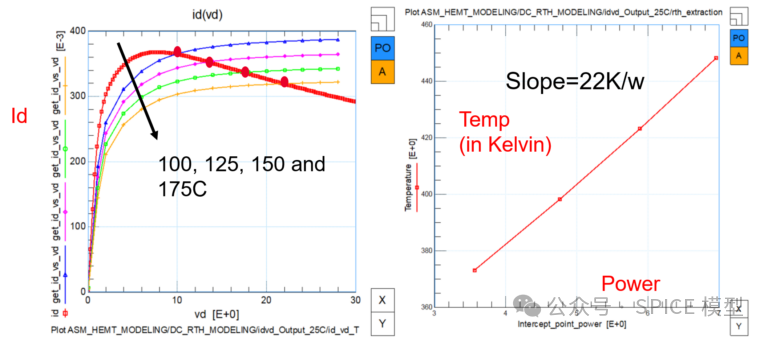

在静态和脉冲激励下,利用漏极电流Id随漏极电压Vd和栅极电压Vg的变化进行热阻RTH0建模是有效的。首先,在室温下的静态Id-Vd曲线提供了一个基线。然后,在Vd0和Vg0保持在0V的情况下施加短Id脉冲,以最大限度地减少Trapping和Self-heating,从而提供不同温度下的响应曲线。将静态曲线与脉冲曲线叠加会得到Id相同的交点。计算并绘制功率与温度的关系,曲线斜率为RTH0。使用脉冲Id方法提供了一种比单独从直流静态特性中提取RTH0更直接的提取方法。

Trapping模型参数抽取

GaN器件中的Trapping效应也严重影响了器件的性能和可靠性。缓冲层和界面层中的电荷捕获降低了2DEG通道电荷密度和动态离子,增加了动态Ron和Cutt-off电压,并调节了Id。

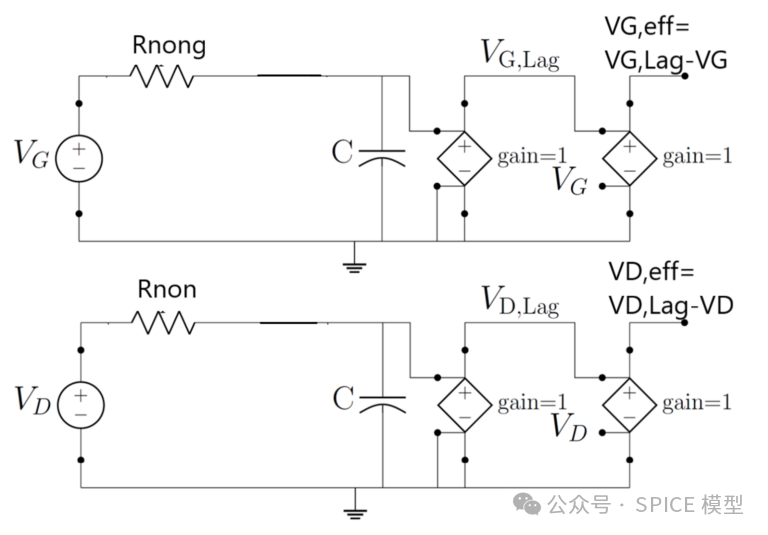

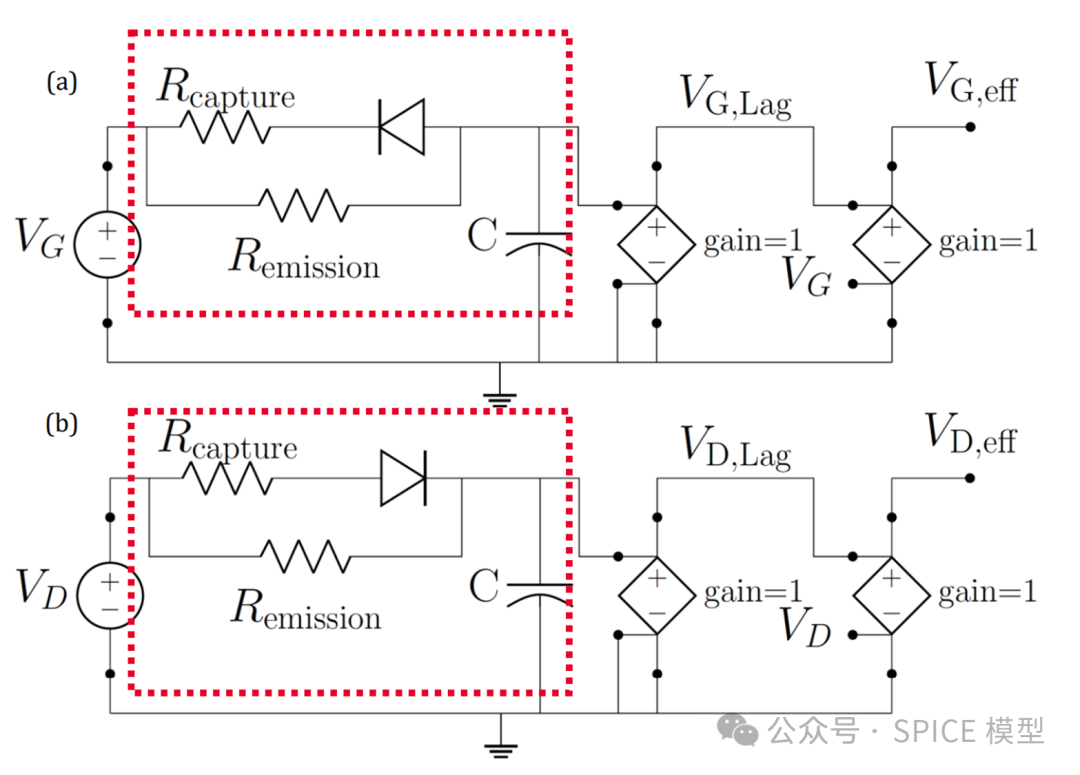

同样,ASM-HEMT和MVSG_CMC之间的参数提取方法相似,即使模型之间在R-C网络的实现上存在差异。Trapping参数提取是在DC、IV、Thermal、S参数提取之后进行的。Gate-lag Trapping参数首先被抽取,因为它影响晶体管的初始响应和整体行为,只影响表面陷阱捕获。通过分析gate-lag行为,drain-lagTrapping提取更加准确,同时影响表面和缓冲陷阱。

ASM-HEMT Trapping Model 4 使用两个R-C电路来模拟drain-lag 和 gate-lag。

MVSG_CMC Trapping Model 2 使用一个类似的网络,但物理模型略有不同,考虑到捕获和释放时间的变化。

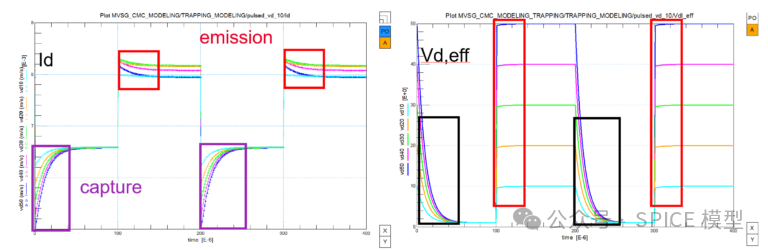

在Pulsed Vg下,同时保持Vd为常数来抽取gate-lag的参数;在Pulsed Vd,同时保持Vg为常数来抽取drain-lag的参数。

MVSG-CMC的典型drain-lag图说明了陷阱捕获和释放效应的差异

-

介绍一种扁线电机趋肤效应和邻近效应的新型解决方案2023-07-18 3507

-

非线性模型如何帮助进行GaN PA设计?2018-08-04 4113

-

GaN HEMT可靠性测试:为什么业界无法就一种测试标准达成共识2020-09-23 4542

-

霍尔效应和霍尔效应法测量螺线管线圈内的磁场2009-11-03 1924

-

使用大数据进行社交网络中的从众效应和权威效应影响分析2019-10-30 1453

-

内光电效应和外光电效应的区别2020-08-04 31736

-

《涨知识啦19》之HEMT 的电流崩塌效应的讲解2020-09-21 2937

-

热电偶、热电效应和热电效应原理2021-10-29 10354

-

分析毫米波GaN器件热电效应2022-09-08 3208

-

GaN HEMT大信号模型2023-05-24 3793

-

GaN单晶衬底显著改善HEMT器件电流崩塌效应2023-06-14 4476

-

FinFET工艺之self-heating概念介绍2023-12-07 5514

-

电光效应之普克尔效应和克尔效应2024-12-02 2997

-

霍尔效应和量子霍尔效应的原理与机制2025-01-07 3146

-

GaN HEMT的SPICE模型使用指南及示例2025-03-11 3087

全部0条评论

快来发表一下你的评论吧 !