选ADC做外围电路的时候,需要考虑些什么?

描述

今日正文

(1) 怎么看ADC

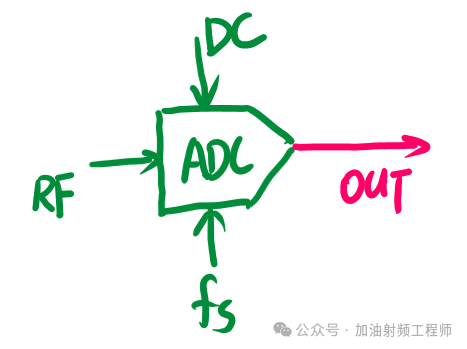

一个ADC,可以把它简单的看成这样一个器件,三个输入,一个输出。

三个输入分别是模拟射频信号输入,时钟输入和电源输入。

一个输出为数字采样信号输出。

(2)ADC的电源选型

市面上有很多型号的LDO和DC-DC,到底应该选择哪种呢。按理说,指标最高的一般都没问题,但是关键指标高的那不是贵么?所以要是能选个指标没那么好,但是和所用ADC搭配刚刚好的器件,那不是又便宜又性能OK么?

与ADC的电源选型相关的,就是ADC的PSSR和PSMR。

当噪声从ADC的电源端引入的时候,噪声可能会直接出现在ADC的输出端,也有可能是噪声与模拟输入信号产生的调制信号出现在ADC的输出端。

举个例子,假设叠加在DC上的噪声信号的频率为1MHz,模拟输入信号为100MHz,而PSSR关注的是ADC输出端的1MHz频率处的幅度,而PSMR则关注的是ADC输出端在101MHz和99MHz频率处的幅度。

ADC厂家的手册上,很多都没有PSSR和PSMR的详细指标。

如果我们对LDO和DCDC的成本敏感的话,比如说出货量很大,单个器件省点就能省下一大笔钱的话,可能就需要自己做些预研工作,测试一下ADC的PSSR和PSMR随频率变化的曲线,以此来选择合适的电源器件。

如果不敏感的话,可能就不费那个事了,直接高指标的电源器件+高抑制的电源滤波,完事。

(3) ADC的时钟电路

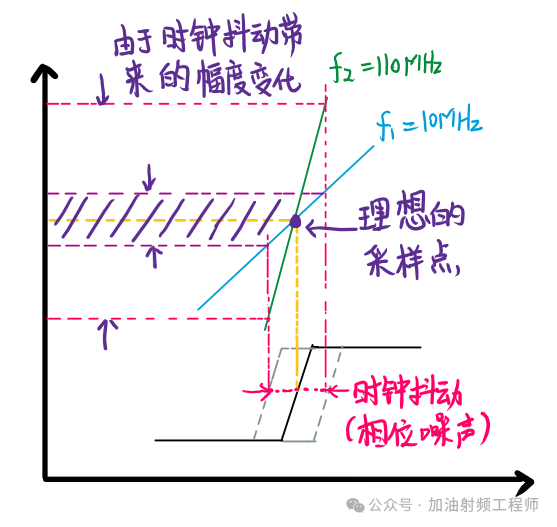

如上图所示,当时钟边沿有抖动的时候,采样的时刻也会有抖动,这样对应的采样数据也会有抖动,而且输入频率越高,由于时钟抖动带来的幅度变化越大。

所以,在评估ADC的时钟是否符合要求的时候,需要综合考虑时钟的抖动带来的影响。

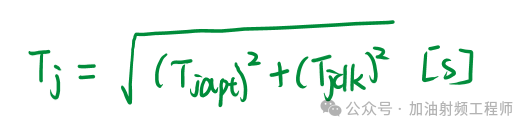

采样时钟抖动Tj是由时钟源(Tjclk)和内部ADC孔径抖动(Tjapt)产生的抖动的组合,即:

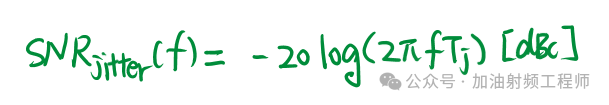

由总抖动导致的ADC的SNR下降,可按以下公式进行计算:

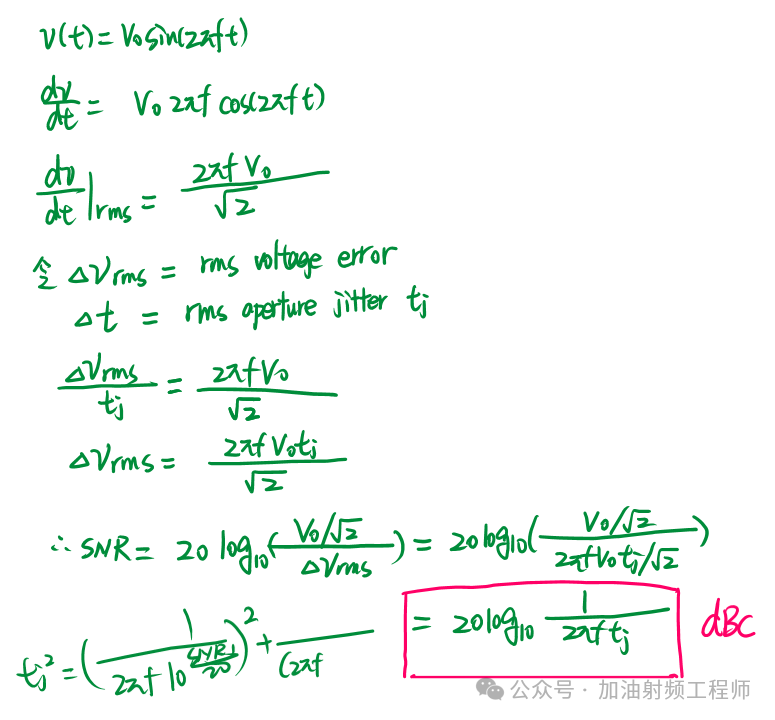

具体推导如下:

这个公式,是假定影响ADC的SNR的只有抖动本身,而ADC的SNR为无穷大。

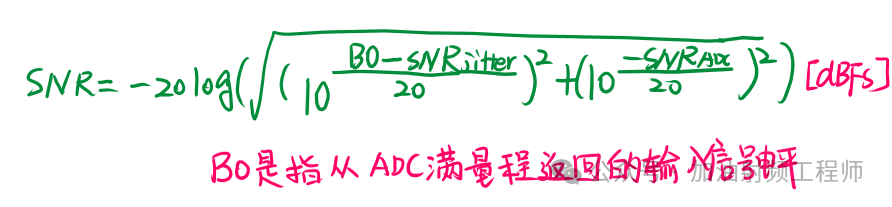

但是,ADC本身受量化噪声和热噪声的影响,所以自身有一个SNR,假设为SNRADC,则:

这边的单位会有点绕,本质上就是由抖动计算出来的SNR的单位是dBc,也就是说以信号的大小为基准的;但是加上ADC本身的SNR之后,由于手册上计算SNR时,都是基于-1dBFS来得到的,所以两者结合起来的时候,划归到统一的单位,即dBFS,所以会有BO这一项。

(4) ADC的输入电路

对ADC的输入电路进行设计的时候,需要根据具体要求,来设计电路。

同时还要考虑抗混叠滤波器。

设计完的电路,拿不准的时候,可以用仿真来验证。

-

ADC和FPGA之间LVDS接口设计需要考虑的因素2025-07-29 5692

-

DESAT外围电路设计的应用笔记2023-10-09 18030

-

电路板设计需要考虑的一些因素2023-06-13 2445

-

一文教你如何进行ADC的外围电路设计!2021-03-26 4185

-

MT-012: ADC需要考虑的交调失真因素2021-03-20 1005

-

如何进行ADC的外围电路设计2021-02-10 5716

-

ADC外围电路应该如何设计2020-12-20 6853

-

使用ADC时VREF引脚需要考虑的因素有哪些?2020-12-11 3494

-

请问设计稳压电路的时候要考虑哪些因素?2019-06-25 2432

-

【开发经验】嵌入式硬件设计需要考虑的一些问题总结2018-08-28 2697

-

电源外围保外围应用电路2015-10-15 2675

-

ADC外围电路设计方法2012-03-15 10085

-

ADC外围电路的设计2011-02-11 5352

-

adc0809外围电路2007-12-25 4361

全部0条评论

快来发表一下你的评论吧 !