HPI接口在TI SOC的应用详解

接口定义

描述

摘要

本文从总体上介绍HPI(Host Peripheral Interface)接口的工作模式,与上位主机的连接方式,主机访问的操作流程;归纳了应用当中常见问题,并提供了分析解决办法。

简介

HPI 接口是TI 为处理器之间直接互连通讯定义的一种异步接口,大多数TI DSP 芯片上都有HPI 接口。HPI 接口是从(Slave)端口,接在主机的扩展内存总线上,DSP 不能通过HPI 向主机(Host)的访问,只能被主机读写。两个DSP 的HPI 接口之间不能通讯。两个DSP 之间互连,可以将一个DSP(从)的HPI 接到另一个DSP(主)的扩展内存接口(EMIF)上[1]。

1. HPI工作模式

不同系列DSP 上的HPI 接口版本有所不同,区别体现在DSP 对HPI 的控制上,如C6727 上的UHPI 可通过寄存器使能与关闭HPI 接口,对主机访问DSP 内存空间的控制,以及对HPI 接口信号的功能复用上。但从主机访问的角度,HPI 的工作模式分为:复用模式(Multiplexed-Mode)和非复用模式(Non-multiplexed-Mode)。

复用模式下没有地址线,主机访问DSP 的地址信息是以数据方式送到HPIA(HPI 地址寄存)。从硬件信号的角度,地址,数据信号是由同一组数据线传递,所以称为复用模式。

非复用模式的数据线与地址线是分开的,与内存接口连接相似。非复用模式不需要操作HPIA 寄存器,主机访问的地址信息通过地址总线直接送给HPI。

所有的HPI 接口都支持复用模式,但不是所有芯片的HPI 接口都支持非复用模式(参考相应的芯片手册确定是否支持)。除了有无HPIA 的操作区别外,两种模式的操作没有区别。因为非复用模式的操作是复用模式操作的子集,为方便起见,本文以复用模式展开讨论。

2. HPI硬件信号连接

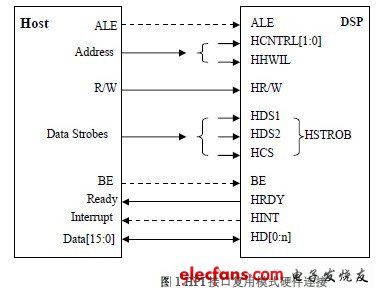

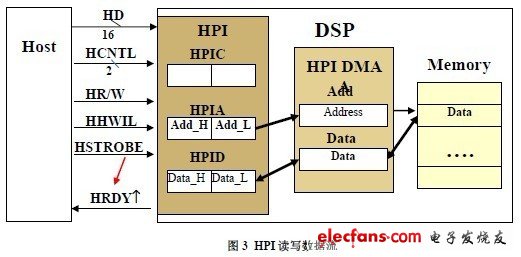

HPI 接口复用模式连线如图1 所示,根据在应用当中的必要性分为:必要的,和可选的两组信号。可选的信号

以虚线表示。

l 数据线HD[0:n]:在复用模式下,数据线的宽度一般为CPU 位宽的一半,一个HPI 访问分为高低半字的两次访问,如C5000 是16-bit CPU,HPI 数据线为8 位,C6000 是32-bit CPU,其HPI 数据线为16 位。C64x 系列的HPI 支持32 位,在32 位模式下一个HPI 访问不需要分为高低半字两次访问组成一个完整的访问。

l HCNTL0/1,HWIL:HCNTL0/1 选择要访问的HPI 寄存器,HWIL 控制访问寄存器的高低半字,必须先高后低。一个寄存器的高低半字的两次访问一定要连续完成,中间不能插入其它的HPI 操作。只有HPIC 可以只访问半个字。

l HR/W:指示对HPI 寄存器进行读,还是写操作。如果主机的读,写信号是分开的,可以利用其中一个信号,但要注意做上拉或下拉处理以控制其在三态时的电平。

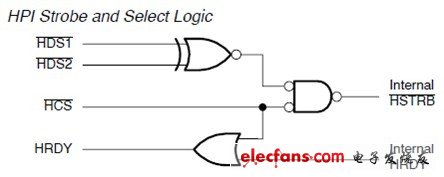

l HCS,HDS1/2:这三个信号根据图2 的逻辑产生内部HSTROBE 信号,其逻辑关系是要求HDS1 和HDS2信号相反,HCS 低有效。HSTROB 下降沿的时间点反应的是三个信号中最后跳变的信号。HPI 在HSTROB的下降沿采样控制信号HR/W,HCNTL0/1,HWIL 以判断主机要对哪个寄存器进行读,或者写操作命令。

注意控制信号在HSTROBE 的下降沿之前需要最少5ns 的setup 稳定时间,而HDS1/2 和HCS 到HSTROBE信号内部门电路的延时是皮秒级的,所以控制信号的setup 时间需要外部时序保证。

图2 HSTROBE信号产生逻辑

l HRDY:HPI 的输出信号,指示当前操作状态,用做硬件流量控制握手信号。

l HINT:通过HPI,主机与DSP 之间可以互发中断。HINT 是HPI 送给主机的中断信号,DSP 对HPIC[HINT]位写1,HINT 信号线上送出高电平信号,主机可利用此信号做为中断信号输入。DSP 不能清除HPIC[HINT]状态,主机在响应中断后,需要对HPIC[HINT]位写1 清除状态,DSP 才能再次对HPIC[HINT]置位发中断。主机通过写HPIC[DSPINT]置1 给DSP 产生中断,DSP 在响应中断后,需要对HPIC[DSPINT]写1 清除状态,主机才能继续操作HPIC[DSPINT]给DSP 发中断。通过HPI 传输数据,结合互发中断做为软件层的握手信号,可有效提高通讯的效率与灵活性。

l ALE:存在于地址,数据线复用的主机上用来指示地址信号周期,这种总线复用的主机很少见,所以通常将ALE 固定上拉处理,只用HSTROBE 采样控制信号。

l BE:Byte Enable 信号,这个信号只出现在32 位的C6000 DSP 上。因为应用当中通常都是对整个32-bit 字进行访问,所以直接做上拉使能处理。

3. HPI寄存器地址映射

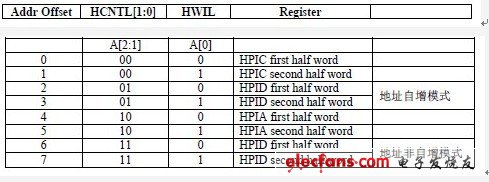

HPI 口提供给主机端访问的寄存器只有4个,通过HCNTL[1:0]选择.

表1 HPI寄存器访问选择

由于在复用模式下数据线通常只有寄存器宽度的一半,所以一个完整的数据访问由高低半字两次访问组成,由HWIL 信号控制,HWIL 信号必须是先低后高。通常将HWIL 和HCNTL[1:0]接在主机的地址线上,将4 个寄存器映射为主机端的8 个内存单元,下表中的地址线连接方法将8 半字寄存器映射到主机的8 个连续的内存单元。这里的地址线是用来选择HPI 的寄存器,与非复用模式下的地址线直接访问DSP 的内存空间是完全不同的作用。

表2 HPI寄存器地址映射

4. HPI寄存器功能说明

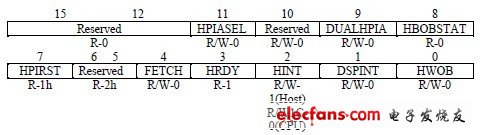

HPIC (HPI Control Register)

HPI 控制寄存器HPIC 的位图如表3 所示,C6000 系列DSP 的HPI 寄存器是32 位的,也只有低16 位有效,与C5000 系列DSP 的HPIC 寄存器定义的功能保持一致。不同版本的HPI 接口的HPIC 位定义的主要不同之处在于软件握手HRDY 位的有无,其它位名称可能存在细小差异,但功能定义都是一样的。

表3 HPI Control Register

主机在对HPI 进行访问前可以通过HPIC 配置字节序(HWOB)和地址寄存器模式(DUALHPIA)。默认的配置为HWOB=0,即先访问高半;DUALHPIA=0,即单地址寄存器模式,读和写操作使用同一个HPIA;通常都采用默认的HPIC 寄存器配置。

HWOB 与硬件信号HWIL 是没有联系的,HWIL 信号必须保证先低后高分别访问两个半字单元。至于先访问一个字当中的高或低半字,是由HWOB 控制的。

HPIA (HPI Address Register)

物理上存在HPIAR,HPIAW 两个地址寄存器。HPIAR 是读操作地址寄存器;HPIAW 是写操作地址寄存器。由HPIC 的DUALHPIA 位来决定是采用双地址寄存器模式还是单地址寄存器模式。如果采用双地址寄存器模式,在对HPIA 操作之前,通过设置HPIC 的HPISEL 位选择下一个要访问的HPIA。通常为了简化在读写操作转换时对HPIC 的操作,选用单地址寄存器模式。

HPIA 的地址信息在不同系列DSP 上有所不同:

在C5000 上,数据空间,I/O 空间只能按16 位字寻址,程序空间按字节寻址。HPI 的DMA 访问属于I/O 空间,HPIA 的值代表16 位字地址。如主机端要访问DSP 内存字节地址0x100, 则要往HPIA 写的地址值是0x80。在用HPI 启动时,要注意DSP 代码是按字节地址链接的,即代码段的地址是字节地址,主机端要将代码段的地址信息除以2 再送到HPIA。

在C64 上,HPIA 的值代表字节地址,但是HPI 访问的数据是32 位的,所以HPI 会忽略HPIA 地址值的低两位。

在C64+的DSP 上,HPIA 代表32 位字地址,HPI 会将字地址左移两位转换成字节地址,主机若要访问DSP 字节地址0x100,则要赋值HPIA 为0x40。

HPID (HPI Data Register)

主机通过HPI 对DSP 的内存访问是间接访问,主机只能访问HPID,HPID 与DSP 内存之间是通过HPI 专属的DMA 进行数据搬运的。如图3 所示。

HPID 的访问分为自增模式和非自增模式。在自增模式下,访问HPID 后,HPIA 会自动增加指向下一个字地址,在连续访问时,自增模式因为减少了主机对HPIA 的操作,可以增加HPI 数据访问的吞吐率。非自增模式下访问HPID 后,HPIA 的值保持不变,主机需要更新HPIA 来访问下一个地址。

在写操作时,主机把数据写到HPID,HPI 将第二个半字的数据通过HSTROBE 的上升沿锁存到HPID 后,将HRDY 置为忙状态,并启动HPI DMA 将HPID 的内容搬到HPIA 所指向的内存单元,然后清除HRDY 指示可以进行下一次操作。

在读操作时,在第一个HSTROBE 的下降沿,HPI 采样到HR/W为读命令,则将HRDY 置为忙状态,启动HPIDMA 将HPIA 指向的内存单元的数据搬到HPID,清除HRDY 忙状态,主机端方可结束总线访问周期,锁存数据线上的有效数据。

5. HPI操作流程

主机对HPI 的一次总线访问周期为分三个阶段:主机发起访问,HPI 响应,主机结束访问周期。

A. 主机发起访问:即对HPI 寄存器的读,或者写命令。主机送出的硬件信号为HSTROBE(由HCS, HDS1/2产生),HR/W,HCNTL0/1,HWIL,以及HD[0:n]。HPI 在HSTROBE 的下降沿采样控制信号HR/W,HCNTL0/1,HWIL 判断主机的操作命令。

B. HPI 响应:HPI 在HSTROBE 的下降沿采样控制信号,根据控制信号做出相应的响应。如果是写(HR/W为低)命令,则在HSTROBE 的上升沿将数据线上的信号锁存到HCNTL0/1 和HWIL 指向的寄存器。如果是读命令(HR/W 为高),如果是读HPIC,或者HPIA 寄存器,HPI 将寄存器的值直接送到数据总线上;如果读HPID,HPI 先将HRDY 置为忙状态,HPI DMA 将数据从HPIA 指向的内存单元读到HPID,再送到数据线上,并清除HRDY 忙状态,在读HPID 后半字时,数据从寄存器直接送到数据总线上,不会出现HRDY 信号忙状态。

C. 主机结束访问周期:对于写操作,主机将数据送出后,只要满足芯片手册中HPI 对HCS 的最小宽度要求,即可结束访问周期。对于读HPID 操作,要等HRDY 信号由忙变为不忙,主机才能结束访问周期。两次连续的HPI 操作的间隔,在芯片手册的HPI 时序参数表里有要求,最小间隔为两个HPI 功能模块时钟周期。

6. HPI常见故障案例分析

在HPI 应用调试过程中,常遇到的问题分为:写数据不成功,读数据不正确,HRDY 常高。这些问题通常都是由于时序不正确造成的,下面结合实际应用当中的案例进行分析。

1.1写数据不成功

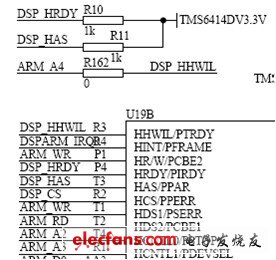

案例的硬件连接如下:

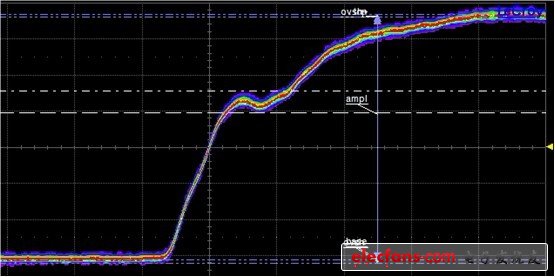

首先关注核心信号HSTROBE 由DSP_CS,ARM_WR(HDS1),ARM_RD(HDS2)产生,从下面时序图可以看出ARM_WR 的下降沿是最后产生的,所以写操作时HSTROBE 的下降沿反应的是ARM_WR 的下降沿。

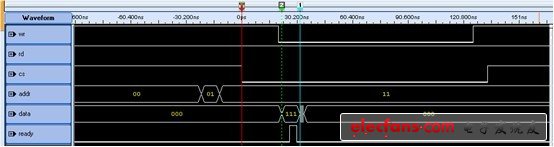

写HPIC 的时序截图如下:

写HPID 的时序截图如下:

两个时序图显示主机送出的数据111b 在HSTROBE(ARM_WR)的下降沿后,很快被改变成其它值000b。在写HPID 的时序截图中,第一个HSTROBE 的下降后,HPI 送出HRDY 信号,然后数据线被改变,首先判断HPI 对主机的命令做出了响应,通过HRDY 信号的出现时机,说明HPI 判断这是一个读操作,可以判断为HSTROBE 的下降沿采样HR/W信号不正确。

从硬件连接来看,HSTROBE(HR/W)要采样HR/W,HCNTL0/1 来判断主机命令, HR/W的与HSTROBE 为同一信号源,且同为下降沿,HR/W与HSTROBE 的下降沿之间的setup 时间不够,采样HR/W的电平状态出现误判,认为是高电平读命令,HPI 对读命令的响应则是在第一个HSTROBE 的下降沿之后送出HRDY 信号,并在HRDY 之后,HPI 送出数据到总线上。

对于该问题,需要对参与HSTROBE 逻辑译码的HR/W信号的下降沿做延时处理,可在逻辑电路如CPLD 或 FPGA 里实现,以确保HSTROBE 的下降沿采样到稳定的HR/W电平。

1.2读数据不正确

通常表现为读读HPIC,HPIA 正常,但读HPID 不正常,前半字为0,后半字正确,对同一个地址读两次,第二次的数据完全正确。

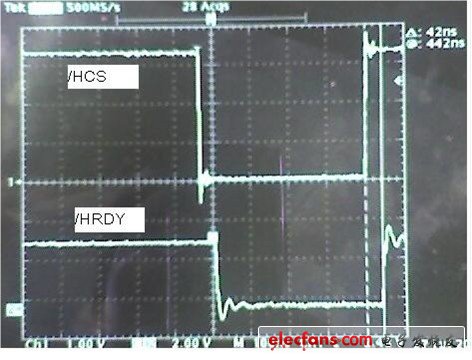

在案例中,用示波器观察HCS 与HRDY 之间的时序关系,发现HCS 的上升沿在HRDY 的上升沿之前,即主机在HPI 数据有效之前结束了访问周期。HRDY 的上升沿其实是因为HCS 的结束而拉高的,并非数据真正有效。

用户由于没有在硬件上将HRDY 与主机PowerPC 的TA 信号互连,没有硬件握手机制,于是从软件配置上加大主机的总线访问周期,即增加HCS 的宽度,故障现象没有变化。

原因分析:读HPID 与HPIC,HPIA 时序不同,读HPID 操作需要HPI DMA 从HPIA 所指向的地址读数据到 HPID,会有时间上的延时。而读HPIC 和HPIA 直接从寄存器读数据,没有延时,所以读HPIC,HPIA 是正确的。在读HPID 时,HPI 会在第一个HSTROBE 的下降沿后将HRDY 置位,指示数据未准备好的忙状态,主机应当在总线上插入等待周期,数据准备好后HPI 清除HRDY,主机才可以结束总线周期,通过HCS 的上升沿将有效数据锁存。

HSTROBE 的下降沿到数据有效之间的延时与芯片及HPI 接口的工作频率相关,以C5502,C5501 为例,在芯片手册中,这个延时参数H1 在SYSCLK1 与CPU 时钟的分频为4 时,最大延时为12*2H+20(ns),H=SYSCLK1/2,在HPI 启动期间,PLL 没有倍频,处于旁通状态,系统输入时钟就是CPU 的工作时钟,SYSCLK1默认分频为CPU 时钟的4 分频,以输入时钟为25MHz 为例,最大延时为:

这个时间长度通常超出了主机端总线周期的软件配置范围,所以通过软件配置增加HCS 的宽度不一定能满足 HRDY 的最大延时要求。在有的DSP 芯片手册上只提供了HRDY 的最小延时,最大延时与芯片的优先级设置,及系统配置相关而不确定,比如与系统中其它主模块如EDMA 同时访问DDR,那么延时与HPI 的优先级,EDMA 的优先级,EDMA 的burst 长度,以及DDR 的命令排序等配置相关,这样通过延长主机的总线访问周期,更加不可靠。

解决办法:在硬件设计之初,一定要利用HRDY 硬件握手信号[2][3]。虽然有的芯片HPIC 寄存器提供了HRDY 软件握手方式,只能做为弥补硬件设计之初遗漏HRDY 硬件握手信号的权宜之计,软件轮循HRDY 的办法会带来额外的开销,降低HPI 总线的吞吐率,增加主机软件实现的复杂度。而且有的芯片HPI 不支持HRDY 软件查询方法,只能通过硬件HRDY 保证数据的有效性。

1.3 HRDY常高

有的系统在长时间运行中偶尔出现HRDY 常高,导致主机端总线访问异常,需要重新上电才能恢复HPI 的正常操作。这种故障是由于HPI 状态机出现异常。

从实际故障定位中总结出以下几点原因:

A. HPI 的高低半字访问的顺序访问被其它HPI 访问打断:在复用模式下,一个完整的HPI 访问是由高低半字两次访问组成,需要严格保证,否则会破坏HPI 的状态机,从而导致不可预期的后果。

B. 主机通过HPI 访问了DSP 内部的保留空间,或者破坏了DSP 的程序,数据空间,导致DSP 运行异常,进而导致HPI 状态机异常。

C. 主机的HSTROBE 信号有毛刺,或者信号完整性不好,如下图中HCS(些案例HSTROBE 是由HCS 控制)的上升沿的回勾,都会导致HPI 误判断为主机的新的访问的开始,从而打乱了高低半字的访问顺序要求,导致HPI 状态机的错乱。

7.总结

HPI 是一种简单的异步接口,只要设计中满足了时序要求,即可稳定工作。在开发当中遇到数据读写不正确,从HSTROBE 信号入手检查与之相关的信号的时序关系,便可以找出问题原因。另外,信号完整性是任何系统稳定工作的前提。

关于特定芯片上HPI 接口的特有功能本文没有针对讨论,如C6727 的字地址模式和字节地址模式可通过HPIC配置;C6727 在HPI 启动后ROM bootloader 将HPI 关闭,需要软件重新使能才能使用等;以及不同芯片的HPI 启动模式下的跳转方式不同,请参考相应芯片的HPI 手册及bootloader 应用手册。

-

PCI总线接口与DSP的HPI接口2011-11-29 7138

-

DSP6000系列的HPI接口怎么调2015-07-22 3778

-

HPI接口的工作模式与上位主机的连接方式2019-05-28 2979

-

基于HPI主机接口的多处理器系统2019-06-06 1944

-

基于HPI的MCU和DSP接口应用2019-06-14 1514

-

如何去设计VC5402的HPI口与PC***的接口?2021-05-26 928

-

HPI接口在脑电数据采集系统中的实现2010-01-07 771

-

HPI在主从式系统数据通信中应用2011-01-19 576

-

主机口(HPI)在基于DSP与ARM的系统中的应用2011-02-27 828

-

HPI接口技术应用2011-09-02 923

-

HPI主机接口在多处理器系统中的应用2011-10-09 2759

-

基于PC机与HPI接口的DSP程序直接下载法2017-10-19 1004

-

DSP的HPI与PC机并口通信接口设计2017-10-20 1044

-

HPI接口的工作模式以及与上位主机的连接方式解析2019-07-01 8966

-

HPI在MCU和DSP接口中的应用2023-08-29 1519

全部0条评论

快来发表一下你的评论吧 !