通俗理解:下载口的上下拉电阻

描述

串行调试(Serial Wire Debug)接口,SWD是ARM目前支持的两种调试端口之一,其用于实现微控制器与调试器之间的通信。SWD仅需4pin的2.54排针加上4根线就能完成程序的烧写与调试,而且ST-LINK的价格也很便宜。

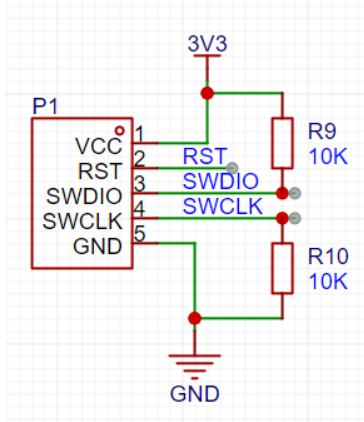

如上图所示,一般我们都会这样设计SWD接口,但是为什么SWDIO需要10K电阻上拉?SWCLK为什么需要10K电阻下拉?

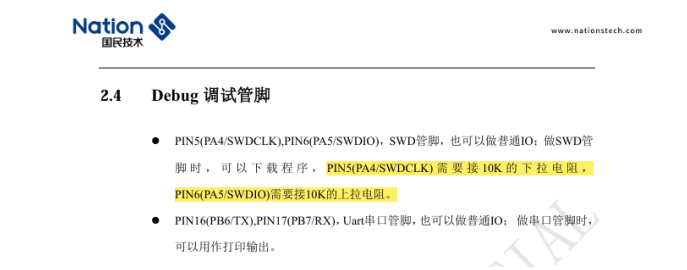

我们先来参照一下国民技术的《N32WB03x 系列芯片硬件设计指南》:

这里明确指出SWDIO和SWCLK需要上拉和下拉。

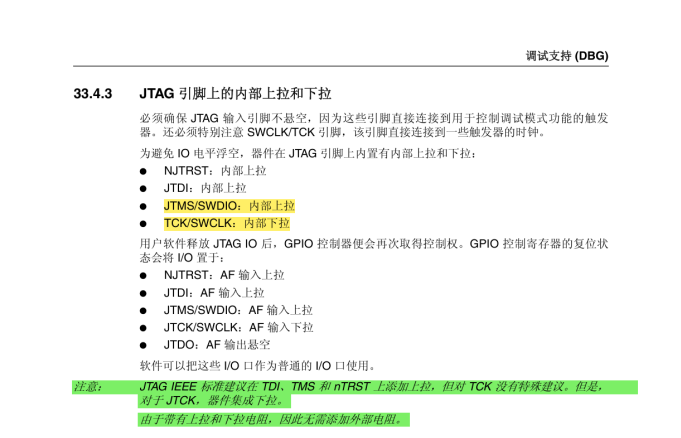

再来看看《STM32F4xx中文参考手册》

在这里,SWDIO和SWCLK内部已经有上拉和下拉了。对于SWDIO,在芯片内部已经有上拉,在电路板上也必须再一次上拉;而对于SWCLK,在芯片内部已经有下拉,没有特殊说明则不需要再下拉。

对于STM32的SWCLK和SWDIO引脚在设计上内部通常带有弱上拉和下拉电阻,这意味着在某些情况下,不额外添加外部上下拉电阻也可以正常工作。而其他一些MCU则需要进一步参照其数据手册以确定,如国民技术的N32WB031KEQ6-2。

而我们也要明确一下上拉或下拉电阻的作用是什么?

首先,上下拉电阻可以在引脚未被驱动时(浮空),使其保证明确的状态(上拉电阻使其保持高电平,下拉电阻使其保持低电平)。同时,上下拉电阻也能抑制噪声,避免因噪声而导致误判。因此为了确保更好的信号完整性、降低噪声干扰和提高通信可靠性,尤其是在长距离传输、嘈杂环境下,建议在设计时添加合适的上下拉电阻(10K或100K)。在实际应用中,应该多参照数据手册以及使用环境决定是否添在SWDIO和SWCLK加上下拉电阻,但是为了以防万一,研发和设计过程中板子上往往会预留下上下拉电阻的位置。

-

电阻是如何实现上下拉功能的呢?2024-02-04 2399

-

电阻上下拉功能实现原理详解2023-11-13 3560

-

单片机上下拉电阻的作用2023-11-06 2734

-

上下拉电阻应用很简单吗?哪些地方要加上下拉电阻?2023-10-08 3911

-

电路设计:上下拉电阻应用很简单吗?2023-03-17 2365

-

上下拉电阻在电路设计中的应用2022-11-23 3505

-

上下拉电阻有什么用呢2022-01-14 1388

-

上下拉电阻有什么用2021-11-30 1671

-

深入浅出上拉电阻下拉电阻2021-11-20 1333

-

上下拉电阻的接线方法及作用介绍2019-09-30 20664

-

上下拉电阻分析2017-07-24 2321

-

上下拉电阻的作用2015-04-18 26939

全部0条评论

快来发表一下你的评论吧 !