基于VLPE技术的碲镉汞p-on-n双层异质结材料与器件研究进展

描述

碲镉汞(HgCdTe,MCT)红外焦平面器件结构包括本征汞空位掺杂n-on-p、非本征掺杂n-on-p、n-on-p台面结器件、n⁺/p高密度垂直集成光电器件(HDVIP)、As离子注入p-on-n平面结、原位As掺杂p-on-n台面结、非平衡全耗尽p-π(ν)-n以及nBn 器件等。典型的MCT红外焦平面器件结构可以概括为n-on-p和p-on-n两种类型,如图1所示。n-on-p器件结构的低暗电流性能优势需要低浓度P型吸收层作为支撑,低浓度P型材料的稳定可控制备一直是MCT材料研究中不变的主题。随着红外探测器向长波/甚长波、高工作温度等方向发展,对器件暗电流提出了更高的要求,p-on-n型器件由于其在工程实现上的性能优势已成为重要的技术路线。

据麦姆斯咨询报道,昆明物理研究所科研团队分析了p-on-n器件几种制备方式的优劣,报道了基于VLPE技术的p-on-n双层异质结器件(DLHJ)在材料生长、器件工艺和器件性能方面的研究进展。重点分析了p-on-n DLHJ器件的国内外差距以及制约该技术发展的关键问题和技术难点,并提出了解决思路,最后对基于VLPE技术的p-on-n DLHJ器件的发展进行了展望。相关研究内容以“基于VLPE技术的碲镉汞p-on-n双层异质结材料与器件研究进展”为题发表在《红外技术》期刊上。

p-on-n器件制备方式对比分析

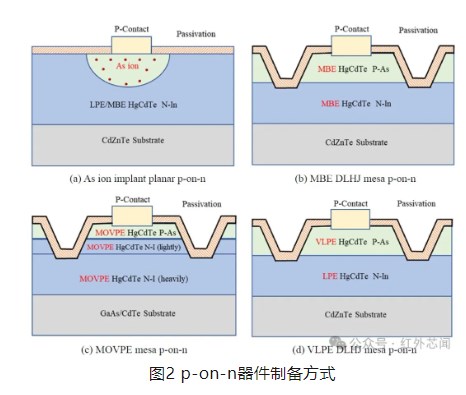

影响p-on-n型器件性能的因素主要有:①N型吸收层的材料质量;②P型cap层的组分,以及同N型吸收层之间的界面状态。N型吸收层材料质量直接决定了辐射吸收和器件性能;宽带隙cap层形成的组分梯度有利于抑制热激发,降低耗尽区漏电流,同时近表面低阻区形成理想的金属接触。p-on-n器件的几种制备方式如图2所示。

图2(a)所示为基于As离子注入的p-on-n平面结器件,图2(b)所示为基于MBE技术的p-on-n台面结器件,图2(c)所示为基于MOVPE技术的p-on-n台面结器件,图2(d)所示为基于VLPE技术的p-on-n双层异质台面结器件。

基于VLPE技术,N型MCT吸收层可采用LPE或VLPE原位掺In生长,P型cap层采用VLPE原位掺As生长,经台面刻蚀、表面/侧壁钝化、电极开孔、金属电极沉积和倒装互连等工艺完成红外焦平面器件制备。相比基于As离子注入的p-on-n平面结器件,一方面避免了离子注入引入的损伤,理论上可减少界面缺陷密度,从而抑制产生复合电流以及缺陷辅助隧穿电流;表面高组分层有利于进一步抑制表面漏电流、耗尽区产生的复合电流和隧穿电流;同时,极大地简化了器件制备的工艺流程,规避了离子注入、激活退火、损伤修复等过程。与基于MBE和MOVPE技术制备的p-on-n异质结器件相比,在获得更高的As激活率的同时减少了高温激活退火过程,有利于获得晶体质量更优越的材料。综合以上分析,基于原位As掺杂与激活的VLPE技术制备p-on-n台面结器件有望在更简单的器件制备工艺下实现更低暗电流,为高性能HOT、长波以及甚长波MCT红外焦平面器件的研制提供技术方向。

基于VLPE技术的p-on-n DLHJ技术研究进展

材料生长

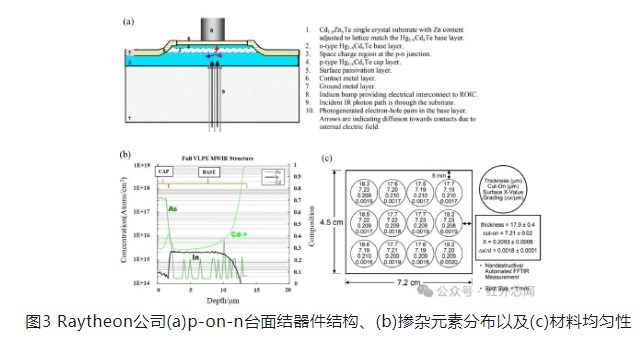

材料的厚度和组分均匀性、晶体质量、组分梯度的构建以及掺杂浓度的有效控制是实现高性能p-on-n DLHJ器件的基础,从前文分析可知,VLPE技术具有高晶体质量以及原位As掺杂与激活等优势,是制备p-on-n DLHJ器件重要技术。图3为Raytheon公司DLHJ器件结构和掺杂元素分布以及材料均匀性。

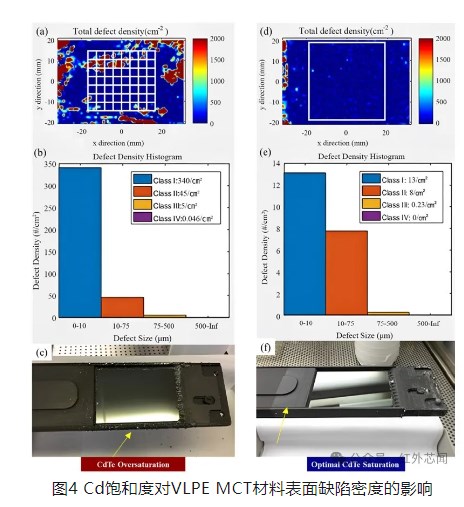

表面缺陷也是影响MCT红外焦平面器件性能的重要因素。Raytheon通过优化Cd饱和度实现了较好的表面缺陷抑制。图4为Cd饱和度对VLPE MCT材料表面缺陷的影响。

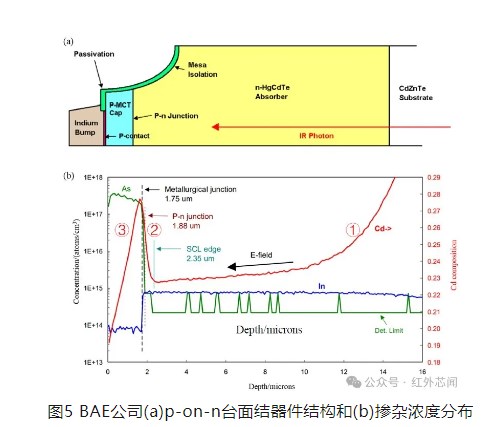

组分梯度的构建是p-on-n DLHJ器件实现漏电流抑制的关键。BAE在文献中多次报道了组分梯度与价带势垒和器件量子效率的关系。研究表明,组分梯度调控是消除价带势垒进而提高量子效率的关键。图5为BAE公司p-on-n DLHJ器件结构示意图和掺杂浓度分布。

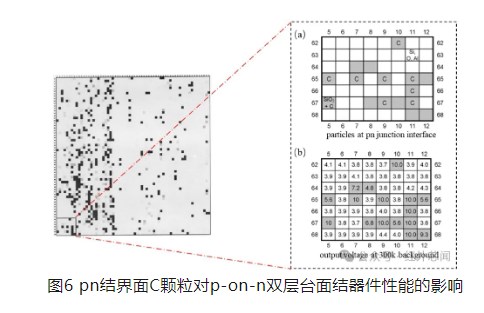

p-on-n双层异质结材料的界面缺陷对器件缺陷辅助隧穿电流、产生复合电流、响应均匀性等关键性能有重要影响。BAE建立了器件漏电流与生长过程中引入的C颗粒之间的关系。图6为对p-on-n双层异质结材料pn结界面处C颗粒对器件性能影响,C颗粒位置与输出电压异常点具有较好的对应关系。

器件工艺

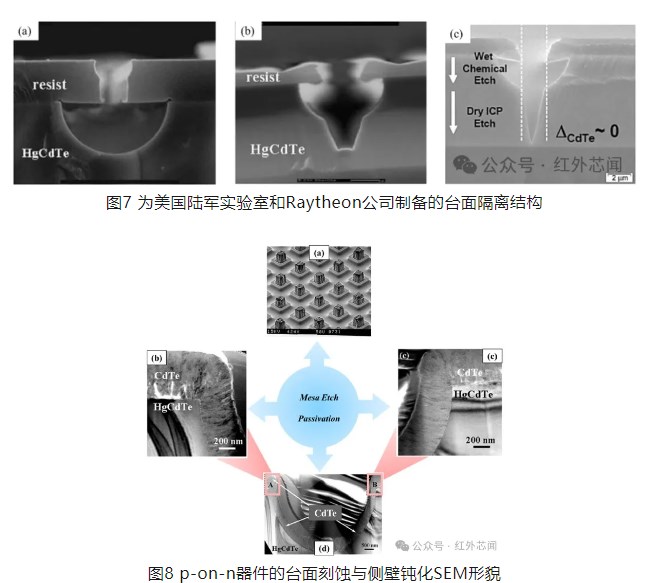

台面刻蚀和表面/侧壁钝化是p-on-n台面结器件的关键制备工艺。台面刻蚀实现像元隔离形成焦平面阵列,制备工艺包括干法刻蚀、湿法腐蚀、干法刻蚀与湿法腐蚀相结合等方法,各研究机构在长期的工艺探索中形成了独具特色的工艺路线,但都在围绕高深宽比、低损伤等目标展开。表面/侧壁钝化则实现表面漏电的抑制,制备工艺包括热壁外延(HWE)、MBE、磁控溅射(MS)、热蒸发(TE)等。

Raytheon采用湿法腐蚀和等离子体耦合(ICP)干法刻蚀相结合制备台面,图7为美国陆军实验室和Raytheon公司制备的台面隔离结构。BAE则采用无损伤湿法腐蚀制备台面结构,MBE技术沉积CdTe钝化层,图8为BAE公司采用无损伤湿法腐蚀制备的台面结构和MBE技术制备的CdTe钝化层侧壁SEM形貌图。

器件性能

材料生长和器件制备工艺是实现p-on-n DLHJ器件的基础,器件性能则是检验材料生长和器件工艺的最终标准。品质因子R₀A和量子效率(QE)是衡量器件性能的两个关键性指标。R₀A为器件零偏电阻R₀和结面积A的乘积,消除了结面积A的影响,能够很好地表征红外探测器的品质。QE为某一特定波长下单位时间内产生的平均光电子数与入射光子数之比,是描述光电转换能力的一个重要参数。

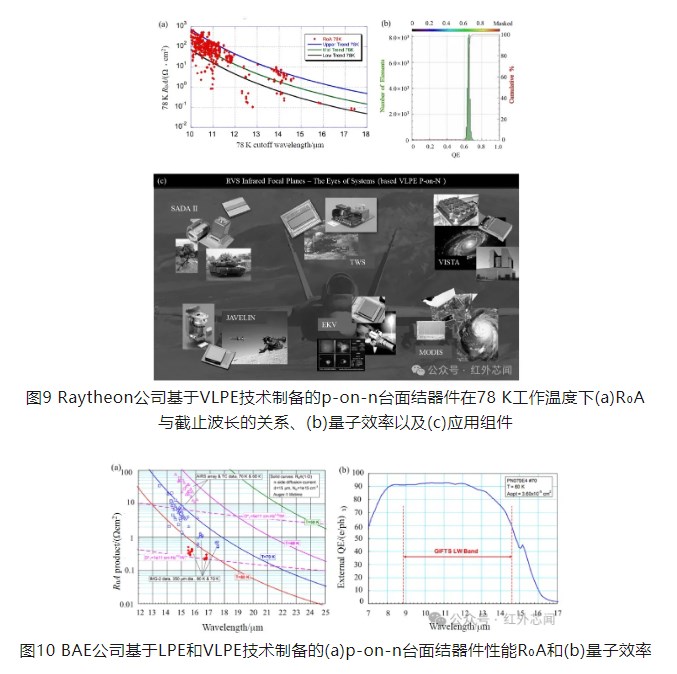

Raytheon基于VLPE技术制备的p-on-n DLHJ器件,图9为Raytheon公司基于VLPE技术制备的p-on-n DLHJ器件性能及应用组件。BAE基于LPE和VLPE制备的p-on-n DLHJ器件,图10为BAE基于LPE和VLPE技术发展的DLHJ器件性能及其所应用的组件。

相比国外,国内VLPE技术起步较晚,发展缓慢。华北光电技术研究所(NCRIEO)在2018年报道了基于VLPE技术的p-on-n长波双层异质结材料生长与器件制备,实现了器件研制,但尚未产品化,主要存在台面器件工艺不成熟、台面刻蚀与表面钝化引起的漏电较大等问题。昆明物理研究所开展了VLPE单层MCT材料表面缺陷抑制、均匀性提升及原位As掺杂等研究,实现了p-on-n双层异质材料的制备,但尚未实现产品的工程化研制。

通过研究国内外现状及发展趋势可以发现,国外已实现p-on-n DLHJ器件的产品化,国内尚处于研制阶段,初步实现了p-on-n DLHJ材料的生长与器件研制,对于Cd组分梯度的调控、掺杂元素扩散还鲜有研究,台面刻蚀、表面钝化等关键工艺尚未成熟。

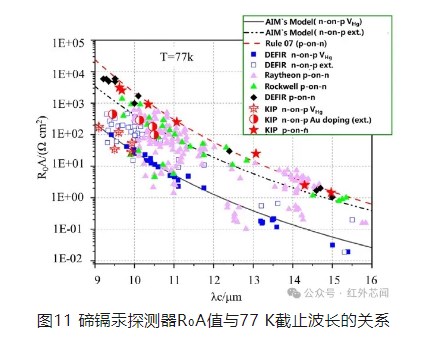

基于VLPE技术的p-on-n DLHJ器件性能优势与技术难点

图11为MCT红外焦平面器件几种器件结构的性能对比。从图中可以看出,国外技术路线包括主要为以美国Raytheon为代表的基于VLPE技术p-on-n DLHJ器件和以法国DEFIR为代表的本征汞空位掺杂和非本征掺杂n-on-p器件,国内则主要发展了基于LPE技术的本征汞空位掺杂和非本征Au掺杂n-on-p器件以及As离子注入p-on-n器件。

综合以上分析,基于VLPE技术的p-on-n DLHJ器件在对暗电流要求较高的长波、甚长波红外探测器方面具有一定的性能优势,是高性能红外探测器的重要发展方向。但目前国内尚未实现产品化,限制器件性能的关键问题和技术难点主要有以下几方面:

1)cap层组分梯度构建。cap层组分梯度的构建是p-on-n DLHJ器件实现表面漏电抑制的关键,如前文所述(图4),需要实现两个区域的组分梯度构建:近界面组分突变陡增区和近表面组分递减区。

2)界面控制。p-on-n双层异质结材料涉及Cd、In、As三种元素的扩散迁移控制,Cd元素的扩散是构建cap层两个组分梯度区的关键,As元素和In元素的扩散则影响pn结的位置。

3)器件台面刻蚀与表面钝化。p-on-n DLHJ器件的台面刻蚀与侧壁钝化是发挥其性能优势的关键制备工艺,台面刻蚀引入的损伤、钝化膜质量的好坏都会影响器件的最终性能。

综上,在传统n-on-p标准工艺基础上,针对材料生长与器件制备的关键工艺进行研究,探究成熟稳定的p-on-n制备工艺,提高其可靠性、重复性及技术成熟度,是实现高性能p-on-n DLHJ器件产品化的重要一环。

结论与展望

MCT是新一代高性能红外探测器的首选材料,暗电流降低是红外焦平面器件性能提升的重要方向。p-on-n型器件是降低器件暗电流的重要发展方向,在p-on-n器件的几种制备方式中,基于VLPE技术的p-on-n DLHJ器件采用原位生长成结,避免了离子注入损伤,实现了原位As掺杂与高激活率的同时,可获得较高晶体质量,表面高组分层可有效降低近漏电流,是高性能红外探测器的重要发展方向,有望成为长波/甚长波以及HOT器件的支撑技术。

然而,目前p-on-n DLHJ器件国内外发展仍存在一定差距,为实现器件的产品化研制与工程化应用,亟需解决的问题包括:1)突破VLPE生长技术,实现低缺陷密度、高均匀性原位As掺杂cap层材料的生长和组分梯度构建;2)研究p-on-n DLHJ器件界面控制技术,兼顾暗电流与量子效率两个关键性能指标;3)研究低损伤、高深宽比台面刻蚀技术,降低刻蚀损伤,减小表面漏电;4)提升钝化层质量,减小侧壁钝化表面漏电;5)在传统的成熟n-on-p器件制备工艺上探索一套适用于p-on-n双层异质结台面器件的工艺,充分发挥p-on-n双层异质结台面器件的工艺简化和低暗电流优势。

论文信息:

http://hwjs.nvir.cn/article/id/c1af70e9-c67d-42df-907f-303188fd7512

审核编辑:刘清

-

基于分子束外延的短/中波双色碲镉汞材料及器件的最新研究进展2021-05-24 4294

-

简析金掺杂碲镉汞红外探测材料及器件技术2021-06-24 5774

-

碲镉汞P-on-N红外探测器的器件结构设计2022-06-20 5700

-

昆明物理研究所在长波p-on-n碲镉汞红外焦平面器件方面的研究进展2022-12-05 2906

-

高工作温度p-on-n中波碲镉汞红外焦平面器件研究2023-01-05 2619

-

碲镉汞APD焦平面技术研究2023-01-16 2786

-

基于昆明物理研究所的Au掺杂碲镉汞长波探测器探究2023-02-13 1449

-

昆明物理研究所碲镉汞红外探测器研究进展2023-08-07 1955

-

碲镉汞贯穿型缺陷的形貌特征及成分构成研究2023-09-10 2534

-

分子束外延In掺杂硅基碲镉汞技术研究2023-09-20 2678

-

详细介绍碲锌镉衬底的表面处理研究2024-01-02 3141

-

碲镉汞PIN结构雪崩器件的Ⅰ区材料晶体质量研究2024-03-15 2127

全部0条评论

快来发表一下你的评论吧 !