如何更好的设计便携式电源

便携电源

描述

一: LDO 的选型和设计

1: LDO 的重要技术指标:

导通压降:

定义为维持输出电压在标称值的100mV 范围内时,输入电压与输出电压的最小差值。这个指标直接反映出效率和电池寿命。

静态电流/地电流(Iq or Ignd ): LDO在无负载工作时自身所需要的电流,直接反映出效率。

工作电流: 调压器在满负载工作时,自身所需要的电流,直接反映出效率

PSRR – Power Supply Rejection Ratio电源干扰抑制率比:反映了电源的变化对该器件的性能指标的影响.也反映了电源输出产生的纹波反射到该器件的输入端的大小.有衰减输出纹波反馈到输入的作用.

小写δ指电压的AC值: 从100Hz,1KHz, 10kHz,100kHz.

2: LDO的选用和使用:

I: 选用LDO的不同封装

根据最高环境温度和最大功耗选择LDO的封装含义如下:

LDO 的最大功耗:

Pmax=(Vin-Vout)x Iout+IqxVin(可以忽略)

不同封装最大能耗散的功率:

二者必须满足以下关系式:

Pmax《Pd

例如:Vin=4.2V,Vout=3.0V@200mA TPS79930DDC 封装为: TSOT-23 Iq=40uA

工作于:Tj=1250C, Ta=700C, Rtherta=2000C/W

Pmax=(4.2-3.0)x200mA+40uAx4.2V=240mW.

PD = (TJ - TA)/ JA。=(125-70)/200=275mW.

Pmax《Pd, 故可以选用此封装LDO

下表所附是TI TPS79930 系列LDO的不同封装的热阻及该封装在不同环境下的最大功耗:

II: 选用LDO的输出电容:

此表反映了某系列LDO容许的输出电容ESR的大小在4Ω 到10mΩ:

过大过小ESR 输出电容可能导致LDO系统内相位余量不够而不稳定, 如下图所示:

低的 ESR (50mOhm) 将零点移到高频。

这样一来零点发生在0dB穿越频率之后,意味着PL,P1两个极点产生-180度总相移。

系统不稳定。

当然TI也有一系列LDO输出无须输出电容:TPS732XX,由于内部误差运算放大器的相位余量足够大,所以无须外加电容,除非输出电容的ESR和所有寄生电阻的乘积小于50nWF;另由于此类LDO内部集成了一电荷泵提供内部调整管的工作电源,其输入电压最低可以达1.7V.所以从1.8V直接降压到1.5V,1.2V ,在输出电流达250MA最低压差为40mV

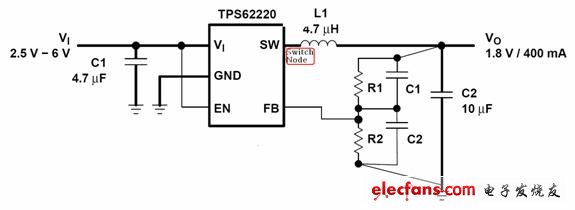

二: DC/DC 电源中电阻和电容的选择和设计:

1: 功率回路中的电容的特性和设计:

电解电容器一般都有很大的电容量和很大的等效串联电感。由于它的谐振频率很低,所以只能使用在低频滤波上。钽电容器一般都有较大电容量和较小等效串联电感,因而它的谐振频率会高于电解电容器,并能使用在中高频滤波上。瓷片电容器电容量和等效串联电感一般都很小,因而它的谐振频率远高于电解电容器和钽电容器,所以能使用在高频滤波和旁路电路上。由于小电容量瓷片电容器的谐振频率会比大电容量瓷片电容器的谐振频率要高,因此,在选择旁路电容时不能光选用电容值过高的瓷片电容器。为了改善电容的高频特性,多个不同特性的电容器可以并联起来使用。图3是多个不同特性的电容器并联后阻抗改善的效果。

ΔV= ΔI X ESRCout

当然并联越多, ESR越低,输出纹波越小。

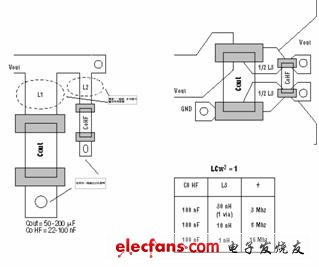

2:功率回路中的电感特性和设计:

I:Buck电路中输出电感的选择:

电感量的计算方法, DC/DC 输出电感电流波形根据工作的模式不同如下图所示:

参数r的说明:

一般r值我们选0.25-0.5(最大输出电流时)

从公式可以看到, r随输出电流变化而变化,当r=2时,电感工作模式从连续过度到非连续。

基本方法的计算公式是从V=L*di/dt演化出来:

正激类输出滤波电感和 变换器输出电感相同一般工作在电流连续模式。电感量为:

Ui----电感输入端电压

D---Ton/T占空比

Uo---输出电压

F=1/T---开关频率

k=ΔI/2Io

允许的纹波电流越小,即 越小,电感越大,纹波电流, 反之,电感较小,要求的电容较大, 一般k=0.05~0.1

II: 电感饱和电流必须满足以下公式:

一般选择电感的饱和电流大于或等于控制器的最大开关电流。

Boost和Buck-boost电感的设计:

当设计为连续工作模式时,所需的电感量必须满足以下公式:

式中Ii=Io/η(1-D)---输入电流平均值。

η---变换器效率。

当设计为断续工作模式时,所需的电感量必须满足以下公式:

式中: Ui---电感输入端电压

3:系统的稳定性补偿:

这是一电压式(VM) DC/DC控制器的频响曲线: (没有回路补偿)

从以上曲线可以看出:

主极点由输出电感电容谐振决定的双重极点。增益以-40Db/斜率下降

输出的等效内阻ESR和容值构成一级零点,此时增益以-20Db/斜率下降直到过零点。,这样一来使得相位余量的范围在450到900

但当输出电容的ESR太低,相移可能达到1800, 而且f0 太接近开关频率(f0》fsw/3),也会使系统不稳定。

综上所看:

高ESR 的输出电容 Cout , 可以得到更大的相位余量,但同时输出纹波较大,因为 ΔV= ΔI X ESRCout. 。 低感量的输出电感可以得到更大的相位余量,在在负载瞬态响应中过冲很小,但开关电流的峰值高会很高,即输出输出纹波较大。

因此我们可以说, 电源设计是一系列的折衷考虑。

为了使我们的电源系统更加稳定, 如果有调整电压输出反馈端,不过去我们可以通过以下方法调整, 使的我们可以在采用在采低的ESR电容, 输出纹波更低的条件下系统更稳定。

I: 一般的电压分压反馈网络:

传输函数 G(S):

II: 加入一前馈电容:

其传递函数和增加的一级零, 极点如下:

III:

这种补偿方式增加一零点和一高频极点但减少了高频增益。被用于增加系统的相位余量。

IV:

这种补偿方式用于减少DC/DC变换器的高频增益, 提高相位裕量。并且减少反馈端的噪声。 但电容容值不能太大, 否则可能使系统的动态响应减慢。

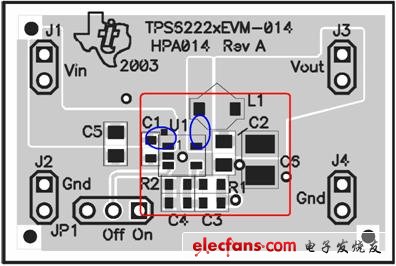

四:PCB板设计布局

1: PCB板设计布局的一般原则

I: 器件的放置的优先级:

先功率器件(MOSFET, 整流二极管,输出电感, 输出电容), 后 控制IC,最后IC周边

II: 功率回路尽量短, 如上图所示加粗线路: 电流从输入到输出的路径。

III: 地线: 一般电源里有功率地和控制地, 要求分别采用星形接地法连接到控制IC的功率地和控制地, 后在IC 下通过一个过孔联结在一起。

IV: 注意几个敏感点:

FB pin 或 I sense 电流取样端: 尽量远离功率回路, 即上图中加粗的部分, 特别提醒,反馈线不能从电感下通过。 这部分线可以走的稍远些。 反馈取样电阻及电容尽量靠近IC.

Switch Node: 在开关电源里, 在这一点的电压波形以开关频率(如1.2MHZ)从输入电压到地高速切换,所以有很高的 dV/dt ,电磁辐射非常严重。 因此我们在画PCB时,避免把此点设计为一天线,要求输出电感尽量靠近MOSFET 或SW脚, 使这点尽量短, 使用多层PCB, 避免通过寄生电容偶合到地和信号通到。

2: 注意过电流量:

电流1A, 1 盎司的铜, 线径最小 = 12 mils Min.

电流5A, 1/2 盎司的铜, 线径最小 = 240 mils Min.

电流20A, 1/2 盎司的铜, 线径最小 = 1275 mils Min.

3oz = 0.105mm

2oz = 0.070mm

1oz = 0.035mm

3: 实例:

-

便携式示波器的技术原理和应用场景2024-10-24 3838

-

便携式充电电源开源分享2022-11-14 1078

-

便携式UPS电源的相关资料推荐2021-11-16 1350

-

便携式产品的电源管理2021-05-13 929

-

便携式UPS电源电池不可拆卸的原因2018-10-17 3224

-

便携式UPS储能电源的简介和应用2018-09-06 6421

-

电源IC在便携式移动设备领域的应用2015-09-29 3347

-

便携式仪器的电源设计2014-04-24 3144

-

用于便携式及无线应用的便携式电源管理2012-08-16 3002

-

便携式医疗应用的电源管理技术2011-02-12 859

-

什么是便携式DVD及DVD电源2009-12-23 2169

-

便携式B超电源的设计2009-10-10 1309

-

便携式仪表电源的设计2009-07-16 1033

-

便携式电源解决方案2008-07-27 4208

全部0条评论

快来发表一下你的评论吧 !