40nm FPGA的功耗管理和优势

FPGA/ASIC技术

描述

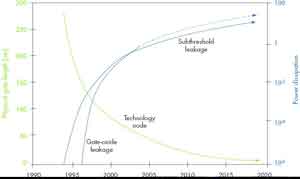

电子发烧友网核心提示:随着工艺尺寸的减小,数字逻辑电路的漏电流成为当前FPGA面临的主要挑战。静态功耗增大的主要原因是各种漏电流源的增加。图1所示为随着更小逻辑门长度的技术实现,这些漏电流源是怎样随之增加的。此外,如果不采取专门的功耗措施,较大的逻辑电容和较高的开关频率也会导致动态功耗增大。

功耗由静态和动态功耗组成。静态功耗是采用可编程目标文件(.pof)对FPGA进行设置,但时钟还没有工作时消耗的功率。数字和模拟逻辑都存在静态功耗。在模拟系统中,静态功耗主要来自模拟电路不同接口配置带来的静态电流。

图1 在更小的工艺尺寸上,静态功耗显著增大

动态功耗是器件工作时由于信号触发和容性负载充放电所带来的功耗,影响动态功耗的主要因素是电容充电、供电电压和时钟频率等。按照摩尔定律,小工艺尺寸降低了电容和电压,从而降低了动态功耗。而难点在于小工艺尺寸上实现了更多的电路,提高了最大时钟频率。随着工艺节点的减小,相同电路的功耗在降低,但是FPGA容量在不断加倍,最大时钟频率不断提高。

体系结构和工艺技术的功耗创新

FPGA可以采用创新的内核、I/O和收发器体系结构以及最新的工艺技术和电路技术来解决这些功耗难题。

1 可编程功耗技术

FPGA内核主要包括逻辑、存储器和数字信号处理(DSP)模块。在Virtex-5 FPGA等标准FPGA中,所有逻辑模块都设计运行在一个速率上——最大速率,导致非常大的功耗。

Altera公司的工程师分析了71个设计的基准测试结果,估算一个设计一般需要多少高速逻辑。他们对设计进行编译,在FPGA架构上实现所能达到的最佳性能。在这些设计中,所需要的高速逻辑大概平均占20%。

图2所示为一个典型的余度直方图,大部分通路(左侧)都有一定的余度,只有少量关键通路(右侧)需要性能最好的逻辑以达到时序要求。

图2 余度直方图显示少量电路没有或者很少有余度

利用这一事实——设计中的大部分电路都有一定的余度,不需要将所有逻辑置于高性能状态。以Stratix IV FPGA为例,它由逻辑阵列模块(LAB)、TriMatrix存储器和DSP模块构成,利用可编程功耗技术将少量的关键时序逻辑模块设置为高速模式。时序不重要的逻辑模块设置为低功耗模式,能够大大降低低功耗逻辑的泄漏功耗。而且,可编程功耗技术将没有使用的逻辑、TriMatrix存储器以及DSP模块设置为低功耗模式,进一步降低了功耗。

在任何设计中,Quartus II软件能够自动确定设计中每一通路的余量,通过调整晶体管反向偏置电压,把晶体管,同时把逻辑模块设置为合适的模式——高性能或者低功耗。例如,将Stratix IV FPGA内核的n-MOS晶体管设置为这两种模式。

● 低功耗模式,Quartus II软件减小反向偏置电压,使得晶体管很难接通。这降低了时序不重要电路的亚阈值漏电流和不需要的静态功耗。

● 高性能模式,Quartus II软件增大反向偏置电压,在几个关键时序通路上的晶体管更容易接通,以满足设计中规定的时序约束要求,提高性能。

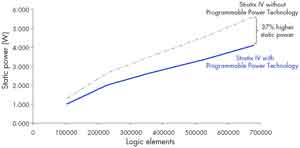

采用同样的方法也能将p-MOS晶体管设置为合适的模式,从而设置LAB、TriMatrix存储器和DSP模块为高性能或者低功耗模式。这样,通过改变晶体管的电气特性,Stratix IV FPGA可编程功耗技术以高速逻辑和低功耗逻辑的最佳组合,实现了最好的性能和最低的功耗。例如,图3所示的Stratix IV EP4SE680 FPGA在85℃时的典型设计,和没有采用可编程功耗技术时相比,静态功耗降低了37%。

图3 可编程功耗技术降低了静态功耗

我们可以精确地控制一个设计达到其性能要求而需要的高速逻辑数量。在每一个逻辑块基础上控制高速和低功耗逻辑的设置(每个逻辑块包括两个LAB,或者一个LAB和DSP模块,或者一个TriMatrix存储器,都含有相关的走线)。例如,在Stratix IV FPGA中,可以分别对5000多个逻辑块进行控制,设置为高速或者低功耗模式,把设计功耗降到最低。Quartus II开发软件能够将逻辑块设置为高速或者低功耗模式,自动对设计进行优化,无须用户的干预。

Quartus II软件每次针对Stratix III FPGA进行设计编译时,自动对设计进行优化,达到规定的时序约束,同时实现最低功耗。得到的编程文件被装入FPGA,包括将每个逻辑块设置为高速或者低功耗配置的信息。在Quartus II软件中完全可以看到逻辑块高速或者低功耗模式的最终设置。

2 MultiTrack互连

Stratix系列器件还采用了MultiTrack互联来提高性能,降低拥塞和功耗。MultiTrack互联提供不同LAB之间的连接,可以采用一个LAB到另一个LAB之间的“跳转”数量来对其性能进行衡量。由于增加互连跳转数量会增大电容,因此,跳转数量越少,就可以采用越少的高速逻辑来达到性能要求。

ALM和MultiTrack体系结构相结合后,能够以更少的布线连接更多的逻辑,从而提高了性能,降低了功耗。

3 分级时钟

分级时钟可以在LAB层面上来控制每一时钟网络的传播。作为Quartus II软件中逻辑优化的一部分,通用时钟逻辑被划入LAB中。只有在逻辑使用时钟时,才启用该时钟。关断所有其他时钟信号,以降低功耗。

4 DDR3和动态片内匹配

以Stratix IV FPGA为例,其I/O创新技术包括I/O中直接内置读/写调平功能,更迅速方便地与1067Mb/s533MHz) DDR3 DIMM进行接口。从1.8V工作的DDR2过渡到1.5V工作的DDR3,使I/O静态功耗降低了30%。

为进一步降低I/O静态功耗,可在数据传送期间动态接通和关断串联匹配(RS)及并联匹配(RT),这一功能被称为动态片内匹配(DOCT)。在写周期,RS接通,RT关断,以匹配线路阻抗,而在读周期,RS关断,RT接通,实现与总线的远端匹配。在一个典型72位DIMM上,和使用DDR2但不具有DOCT的标准FPGA相比,Stratix IV FPGA在1067Mb/s时I/O静态功耗降低了65% (1.9W)。

5 内置硬核IP和收发器技术

以Stratix IV FPGA为例,它为各种×1、×4、×8 PCI Express Gen1和Gen2应用提供一系列完整的PCI-SIG兼容FPGA解决方案。Stratix IV FPGA新增特性提供4个PCI Express硬核知识产权(IP)模块,嵌有完整的PCI Express协议堆栈(端点和根端口)。这包括收发器模块、PHY MAC、数据链路层和协议层。

和软核IP相比,Stratix IV FGPA中的硬核IP不但节省了逻辑和嵌入式存储器资源,缩短了设计和编译时间,而且大大降低了功耗。表1为Stratix IV FPGA中PCI Express硬核IP内核Gen2的功耗。

40nm工艺的电路技术

40nm工艺要比以前包括65nm节点和最近的45nm节点在内的工艺技术有明显优势。最引人注目的优势之一是其更高的集成度,半导体生产商可以在更小的物理空间中实现更强的功能。和65nm工艺相比,45nm工艺密度提高了1倍,而40nm工艺密度达到了2.35倍。

半导体行业一直在不断迈向更小的工艺节点,在设备、工艺技术、设计工具和电路技术上进行大量投入,以解决出现的各种问题。整个行业普遍面临的挑战是小工艺尺寸上越来越大的泄漏功率问题,40nm工艺节点(以及以前的节点)采用了很多技术手段来管理泄漏功率,进一步提高性能,或者保持性能不变。

1 全铜布线

铜替代铝之后,减小了电气损耗和功率损耗,从而提升了性能。以Altera为例,该公司在150nm工艺节点开始采用全铜金属进行片内布线,在所有130nm、90nm、65nm和40nm产品中都采用了全铜布线。

2 低k绝缘

绝缘材料实现了金属层之间的隔离,支持多布线层。采用低k绝缘后,降低了布线层之间的电容,显著提高了性能,降低了功耗。

3 多阈值晶体管

晶体管电压阈值影响晶体管的性能和泄漏功率。Altera对性能要求高的高速晶体管采用低阈值电压,对性能要求不高的慢速低泄漏晶体管采用高阈值电压。

4 可变门长度晶体管

晶体管的逻辑门长度影响其速率和亚阈值泄漏。当晶体管的长度接近45nm工艺的最小门长度时,亚阈值漏电流会显著增加。在性能要求不高的电路中,可使用长度较长的逻辑门以降低漏电流。对于性能非常关键的电路,Altera使用长度较短的逻辑门来提高性能。Altera在90nm、65nm和40nm Stratix系列器件中采用了可变门长度晶体管来降低功耗。

5 三重氧化

逻辑门氧化层的厚度会影响晶体管的性能和漏电流。Stratix IV FPGA在I/O电路和核心逻辑中使用了三个分立的氧化层(三重氧化)。这些核心氧化层中的两个被用于在低性能晶体管中实现最小泄漏,在高性能晶体管中被用于实现最佳性能。

6 超薄门氧化

三重氧化技术还包括针对高性能晶体管的超薄门氧化技术。这些晶体管即使使用长度较长的逻辑门也可以达到最佳性能,适当的提高栅极导致的漏极泄漏以及栅极直接沟道泄漏,能够大大降低亚阈值泄漏。

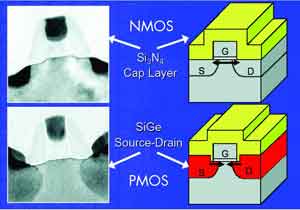

图4 40nm应变硅技术实现了性能更好的晶体管

7 应变硅

应变硅技术增大了晶体管沟道跨导,从而提高了晶体管的性能,如图4所示。Stratix III和Stratix IV FPGA的所有晶体管中使用了应变硅技术,以提高FPGA的性能。

Quartus II功耗优化

详细的设计实施可以提高性能,减小面积,降低功耗。以前,通过布局布线设计流程,寄存器传送级(RTL)自动在性能和面积上达到均衡。Quartus II PowerPlay优化工具自动在Stratix IV FPGA上继承了这些节省功耗的特性,进一步降低功耗。

Quartus II软件的许多自动功耗优化功能对设计人员而言都是透明的,而且还提供Stratix体系结构详细的优化措施以降低功耗,这些措施如下。

1 分析和综合优化

● 主要功能模块变换映射用户RAM,降低功耗。

● 重新规划逻辑以降低动态功耗,正确的选择逻辑输入,降低高频触发网络的电容。

2 适配器优化

● 降低核心逻辑的面积和连线要求,以降低布线的动态功耗。

● 修改布局以降低时钟功耗。

● 在对时序不重要的数据信号进行布线时,降低速率以减小功耗。

● 将关键通路上的逻辑块设置为高速模式,所有其他逻辑块设置为低功耗模式(Stratix III和Stratix IV FPGA)。

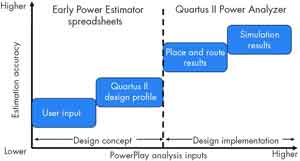

功耗估算

在设计概念构思直到实施的整个过程中,PowerPlay都支持功耗估算,如图5所示。在设计构思阶段,设计人员使用PowerPlay EPE,而在设计实施阶段使用PowerPlay功耗分析器。这些工具是精确的FPGA功耗分析工具。

图5 PowerPlay分析工具——精度和实现

PowerPlay EPE是一种基于表格的分析工具,可以根据器件和封装选择、工作条件以及器件使用情况来进行早期功耗估算。EPE具有FPGA内部精确的功能元件模型,但是,由于在RTL设计之前采用EPE,因此,它缺乏很多关键信息,如逻辑配置、布局布线等,限制了其精度范围。然而,用户还是依靠EPE作为主要的功耗估算工具,在设计早期阶段进行功耗估算。

PowerPlay功耗分析器是更精细的功耗分析工具,它使用实际的设计布局布线和逻辑配置,以及仿真波形精确地估算动态功耗。总体上,功耗分析器结合精确的设计信息,其准确度在±15%以内。

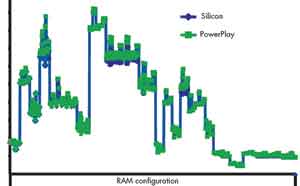

图6 全RAM配置的PowerPlay功耗估算和芯片测量

Quartus II PowerPlay功耗模型与实际的芯片测量结果密切相关。Altera公司使用了8500多个不同的测试配置来测量Stratix系列器件每一组成的功耗。每一配置专门针对FPGA特定配置下的某一电路组成,例如9×9模式下的DSP、×16模式下的M9k存储器模块,以及特定逻辑配置下的ALM等。

所采用的测试方法简单、精确。对特定配置下FPGA中单个模块进行精确的功耗测量,最好的方法是采用待分析配置状态测量的模块实例来配置FPGA。所有其他逻辑和功能模块配置为低功耗工作模式不被激励。然后,在所有被测模块中运行设计好的、能够重复激励的模式,产生清晰的功耗参数。得到的芯片功耗主要来自于大量被测模块,可以从总功耗中提取出多余功耗。得到的功耗除以配置模块数后,得出该模块在该模式下的精确功耗,如图6所示。

结论

虽然迈向尺寸更小的工艺节点实现了摩尔定律预言的密度和性能优势,但是要在提高性能的同时降低功耗,不但要进行工艺创新,而且也需要在FPGA体系结构上进行创新。可编程功耗技术和支持DOCT的DDR3等独特的技术使Stratix IV FPGA等高端FPGA尽可能将功耗降到最低,同时不会牺牲新一代设计的性能。

-

ST宣布:40nm MCU交由华虹代工!2024-11-21 1737

-

IP_数据表(Z-2):GPIO for TSMC 40nm N40EF22023-03-16 618

-

IP 数据表: 3.0V Standard Cell for TSMC 40nm LP2023-03-14 644

-

40nm读取信道芯片RC9500怎么样?2019-08-21 1707

-

Altera公司 Cyclone V 28nm FPGA功耗优势2012-09-05 1346

-

瑞萨电子开发出首款用于汽车实时应用的40nm工艺嵌入式闪存技术2012-01-05 1226

-

赛灵思高性能40nm Virtex-6 FPGA系列通过全生产验证2010-04-24 2394

-

40nm工艺的电路技术2010-03-03 1669

-

三星首家量产40nm级工艺4Gb DDR3绿色内存芯片2010-02-26 1205

-

赛灵思高性能40nm Virtex-6 FPGA系列即将转入2010-01-26 1256

-

赛灵思40nm Virtex-6 FPGA系列通过全生产验证2010-01-22 1101

-

台积电称其已解决造成40nm制程良率不佳的工艺问题2010-01-21 1372

-

传40nm制程代工厂良率普遍低于70%2010-01-15 1431

全部0条评论

快来发表一下你的评论吧 !