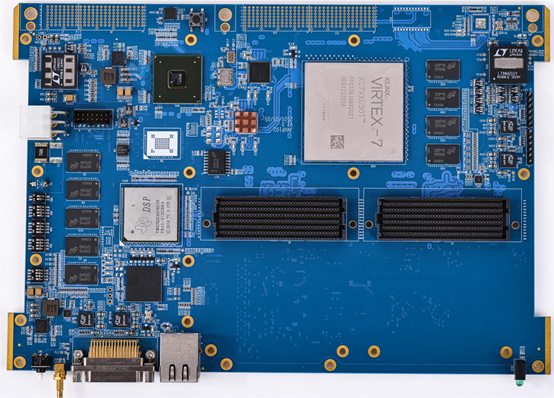

V7-690T和DSP6678双FMC+ 6U VPX 高性能载板

电子说

描述

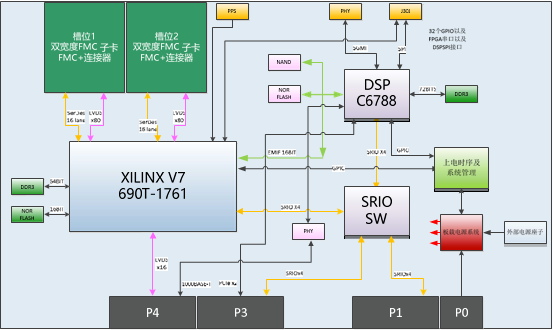

V7-690T和DSP6678双FMC+ 6U VPX 载板一款高性能数据处理载板,可以搭载 2 块标准 FMC单宽度子卡,实现射频信号采集与处理板。该板卡基于Xilinx 公司V7-690T 系列FPGA 芯片,以及 TI 公司TMS320C6678 系列 DSP 芯片。每个子卡槽位最大提供 16 组GTH Serdes以及 80组 LVDS 连接。板卡支持外部触发信号输入,外部 Refclk 参考时钟输入和 RapidIO 或 PCIe信号输入,可以完成多板卡同步输出、同步输出和同步采样功能。板卡 FPGA 侧和 DSP 侧都支持板载 16Gbit DDR3 SDRAM 存储,同时提供一个 10/100/1000MBASE-T 以太网接口和一个RS232 Console调试接口以及多路 GPIO 输入输出。板卡支持 VPX 插头供电和 ATX 插头供电两种供电方式。上电后根据用户的选择方式不同,单板可以从 Flash 启动或者由 JTAG 仿真器动态加载 Bit 文件启动。

DSP 处理器

板载 1 片 TI TMS320C6678 多核处理器;

DSP 外挂 2GB 64bits DDR3,支持 ECC 功能;

DSP 外挂 256MbNOR Flash,位宽 16 位;

DSP 外挂 1GB NAND Flash,位宽 8 位;

DSP 外挂 128KBI2C EEPROM,支持存储配置信息;

DSP 出两路SGMII,一路到背板,一路通过前面板出 1000BASE-T 接口;

DSP 出一路PCI-Ex2 到 VPX P3 连接器,速率支持 2.5Gbps 和 5Gbps;

DSP 出一路SRIOx4 到 SRIO 交换芯片,速率支持 2.5Gbps,3.125Gbps,5Gbps 和 6.25Gbps;

其他:UART、JTAG、MDIO 和 GPIOs。

FPGA

板载 1 片 VIRTEX 7 系列XC7VX690T-2FFG1761I 可编程逻辑;

FPGA 外挂 2GB 64bits DDR3(最高 4GB),数据速率高达1333M;

FPGA 外挂 1Gb NOR Flash,位宽 16 位;

FPGA 出两路 FMC+槽位,支持单宽度和双宽度 FMC+标准子卡进行功能扩展,每个 FMC+连接器提供 16 对 SerDes 接口(GTX)和 80 对 LVDS 接口,GTX 链路速率最高可达 10.3125Gbps,LVDS 接口可支持高达 400MHz 信号速率;

FPGA 出一路 SRIO x4 到 SRIO 交换芯片,速率支持 2.5Gbps,3.125Gbps,5Gbps 和 6.25Gbps;

FPGA 出 16 路 LVDS 接口到VPX P4 连接器,可同时支持 M-LVDS 总线;

FPGA 和DSP 之间通过EMIF 接口进行互连,可支持 DSP 对FPGA 进行动态配置;

SRIO 交换芯片(IDT-CPS1616)

板载集成单片 IDT 公司 CPS1616 交换芯片;

CPS1616 实现 4 路 SRIO x4 接口用于板内DSP 和 FPGA 以及板间互连;

CPS1616 一路接DSP,一路接 FPGA,另外两路通过 VPX P1 和 P3 连接器提供板间互连;

CPS1616 链路速率支持 2.5Gbps,3.125Gbps,5Gbps 和 6.25Gbps;

CPS1616 可支持静态路由和动态路由,支持 I2C 和SRIO 模式进行初始化;

BMC 板载管理控制器

1) 板载集成一片 XC7A15T 系统管理控制芯片,功能可编程; 2) 电源管理:上下电 Sequencer;

主要芯片的工作模式设定;

复位管理;

温度监控;

可支持板载 DSP 和 FPGA 之间低速接口的灵活通信(UART 和SPI 等);

测试接口

千兆以太网:从前面板直接引出至 RJ45;

测试接口:包含 DSP、FPGA 的 JTAG 信号。

复位

具有上电自复位功能,保证各芯片同步上电;

板内自带复位按键,升顶位置放置;

软件可控复位。

电源和环境

供电方式:直流+12V 供电;

常温模块功耗不大于 60W。

元器件等级:所有元器件都采用工业等级(至少-40℃~85℃)

散热方式:无风扇整板散热

单板外形尺寸

a) 6U(233.35mm×161.5mm)尺寸,VPX 结构;

b) 模块厚度 25.1mm,公差±0.1 mm;

供电

DC +12V 电源供电,功耗≤60W,重量(含散热板)≤1Kg。

VPX连接器接口定义

模块 VPX 连接器接口符合VITA65-2010 OpenVPX规范要求

审核编辑 黄宇

-

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX双FMC接口通用信号处理平台2025-09-01 1119

-

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信号处理卡2024-11-08 1691

-

基于6U VPX XCVU9P+XCZU7EV的双FMC信号处理板卡2024-11-07 2508

-

KU115+ZU19EG+DSP6678的双FMC 6U VPX处理板2024-04-08 2524

-

C6678学习资料:基于6U VPX的 XC7VX690T+C6678的双FMC接口雷达通信处理板2019-09-06 10818

-

和大家分享一个基于6U VPX TMS320C6678+XC7K325T的信号处理板2018-12-19 3606

-

VPX_2FMC_V7_2C6678信号预处理版2018-06-21 2308

-

高性能6U VPX高速信号处理平台2016-03-02 2585

全部0条评论

快来发表一下你的评论吧 !