玩转赛灵思Zedboard开发板(2):最简单的测试工程

PLD开发板

描述

电子发烧友网核心提示:ZedBoard开发板上的Zynq是一个ARM PS(processing system, 双核A9 + 存储管理 + 外设)+ PL(programable Logic) 结构,如果不使用PL,zynq的开发和普通的ARM 开发一样。不同的是ARM PS是可配置,因而硬件信息是不固定的。这也是zynq灵活性的一个表现。电子发烧友网编辑现为读者整合《玩转赛灵思Zedboard开发板》系列文章,其中包括在ZedBoard开发板上的一些应用实例。关于Zedboard开发板详解,参见:【玩转赛灵思Zedboard开发板(1):ZedBoard详解 】。这是本系列的第二篇:玩转赛灵思Zedboard开发板(2):ZedBoard最简单的测试工程,因而会给出详细步骤的截图。其余篇章将陆续推出,敬请期待。

硬件平台:Digilent ZedBoard;开发环境:Windows XP 32 bit;软件:PlanAhead 14.1 + XPS 14.1 + SDK 14.1。

一、配置硬件信息

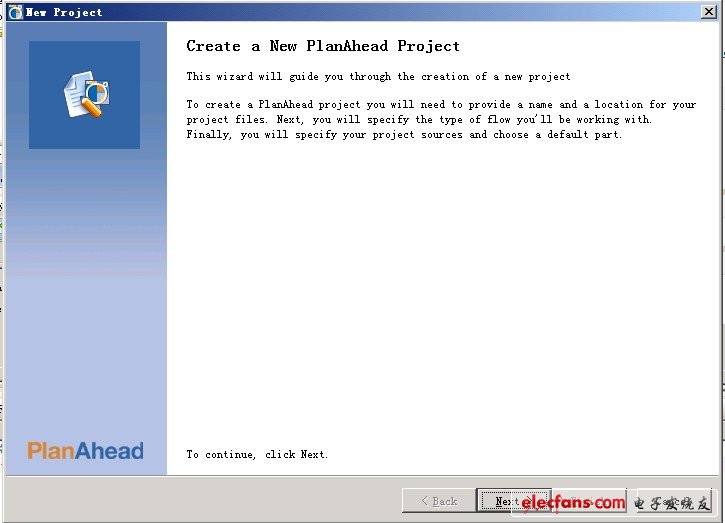

启动PlanAhead,进入新建工程向导

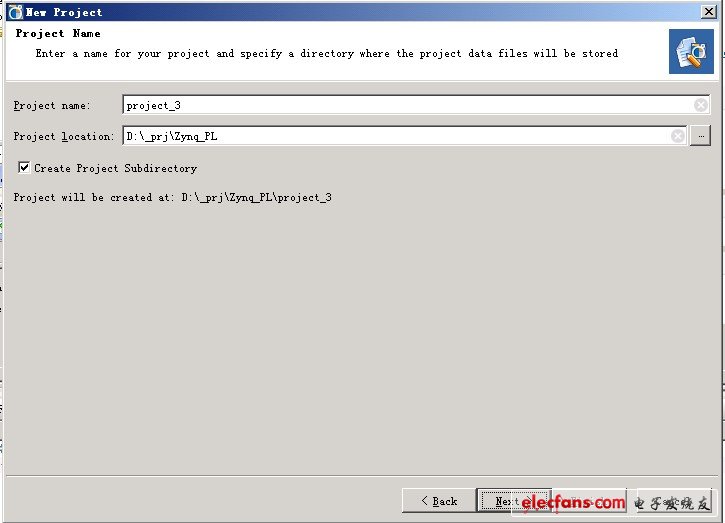

选择工程名和路径

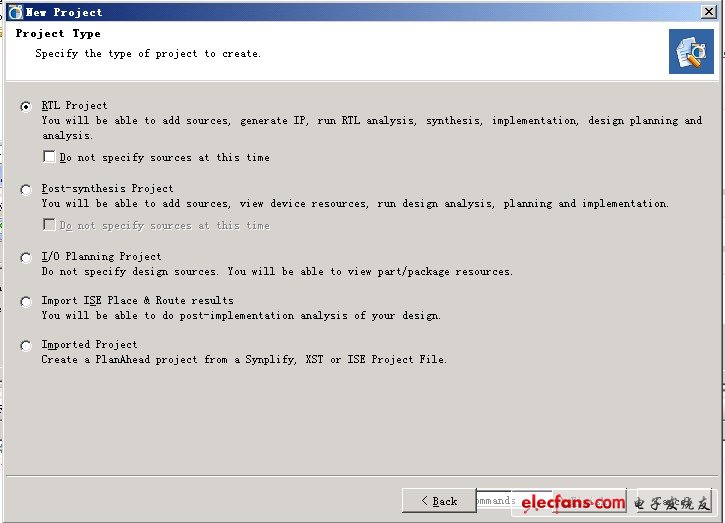

工程类型,这里选择 RTL 工程

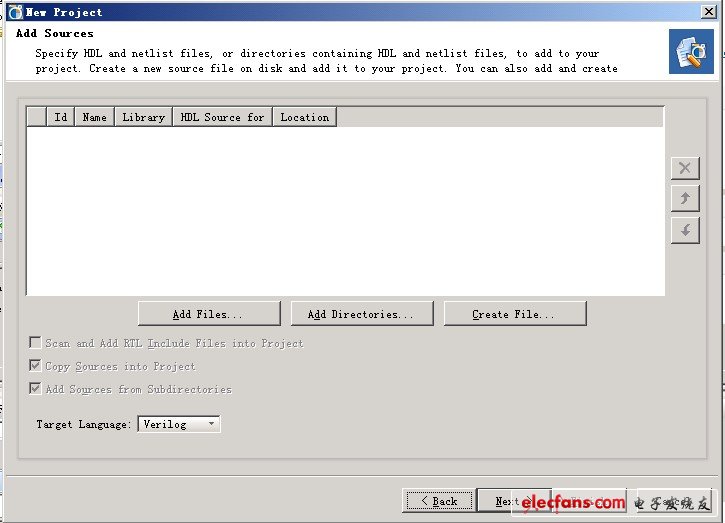

由于只需要PS部分信息,而这部分在后面由XPS完成,因而不需要添加任何文件

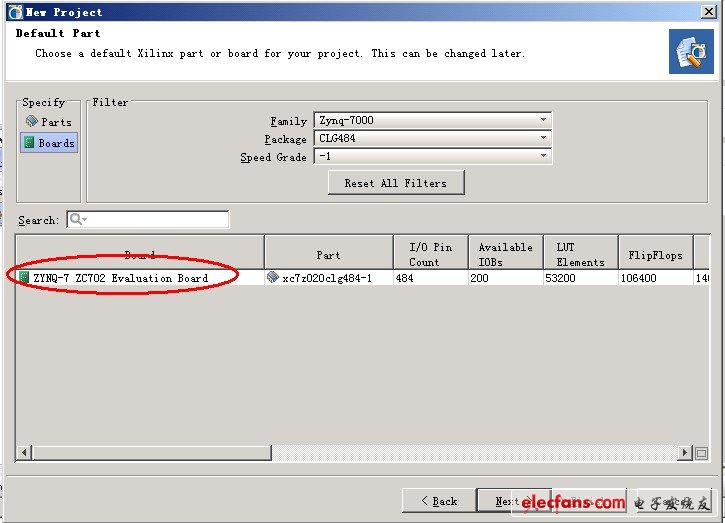

一直点下一步,直道出现芯片和板载信息。直接选择Boards,选择系列是Zynq-7000。14.1目前只支持XC7Z020器件。

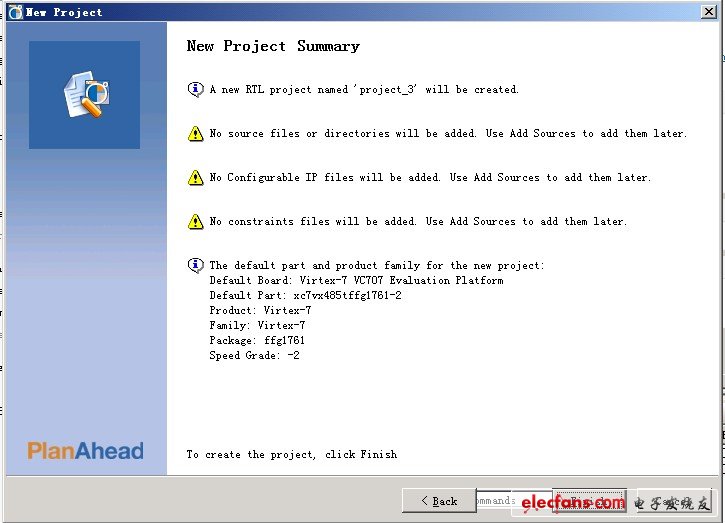

完成新建工程向导

PlanAhead进入工作视图,在Project Manger中选择建立的工程,右键,Add Sources

选择 Add or Create Embeded Sources

单击 Create Subdesign

输入需要建立嵌入系统名称,这里填duocore

确定后,提示所建立的工程是一个Zynq工程,提示是否添加PS到系统。点确认。

XPS会被启动,可以看到Zynq的配置界面。Diligent公司做好了一套配置方案,从其网站上能下载到配置文件:

import这个配置文件,点“+”找到文件位置后,点OK

可以看到配置后的结果,同时MHS和UCF文件也被修改。其中有颜色标记为使用,没有颜色标记表示没有使用。可以对其修改,这是对应ZedBoard的硬件接口,保持默认就可。

至此,硬件配置结束。关闭XPS,切换到PlanAHead。可以看到duocore.xmp已经加入到工程中。

在硬件配置文件duocore.xmp上右键,选择Create Top HDL,生成顶层HDL文件

可以看到生成的duocor_stub.v文件

最后一步,将硬件信息导入到SDK。File-》Export Hardware

为了方便管理,软件workspace放在software目录下。

二、建立软件工程

Export结束后,会自动启动SDK。界面如下。可以看到工程浏览器Project Explorer中已经有一个硬件平台duocore_hw_platform,里面有一系列配置和初始化文件。不要修改这些文件。

新建Xilinx C 工程。

新工程建立向导。这里我们建立最简单的测试工程helloworld。

修改源代码。将工程源文件内容修改,如下

#include

#include “platform.h”

void print(char *str);

int main()

{

init_platform();

print(“Hello World from Zynq ”);

print(“这是Zynq ARM 测试 ”);

print(“2012年9月8日14:30:48 ”);

print(“荣超群 ”);

cleanup_platform();

return 0;

}

至此,工程建立完成

三、编译和下载

给ZedBoard上电,将启动模式设置为Jtag启动,将mini USB下载线接上,并将mini USB to Uart接上。

启动电脑上的超级终端,配置串口和波特率,115200

右键工程hello_world_0,build,编译工程。

右键工程hello_world_0,run-》run configuration,打开下载配置界面。双击Xilinx C/C++ ELF,建立新的下载配置。默认即可。

点run,开始下载。等待下载完成,可以看到ZedBoard向超级终端发来的信息

-

工程师必入!288 元解锁赛灵思开发板2025-12-17 1004

-

赛灵思Spartan开发板使用困境记录 精选资料分享2021-07-13 1692

-

玩转赛灵思Zedboard开发板(6):如何在Zedboard上运行linux下的应用程序?2013-01-24 27464

-

玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯2012-12-05 22666

-

玩转赛灵思Zedboard开发板(1):ZedBoard详解2012-11-26 62744

-

赛灵思(Xilinx) Zedboard开发板简介2012-11-23 18457

-

玩转FPGA 赛灵思(xilinx)FPGA设计大赛圆满结束2012-09-06 6739

-

提交FPGA设计方案,赢取赛灵思FPGA开发板2012-07-06 10414

-

玩转FPGA,赛灵思FPGA设计大赛活动细则,参赛必看2012-04-24 46375

-

玩转FPGA,赛灵思FPGA设计大赛开赛啦2012-04-23 23986

全部0条评论

快来发表一下你的评论吧 !