玩转赛灵思Zedboard开发板(4):如何使用自带外设IP让ARM PS访问FPGA?

PLD开发板

描述

电子发烧友网核心提示:ZedBoard开发板上的Zynq是一个ARM PS(processing system, 双核A9 + 存储管理 + 外设)+ PL(programable Logic) 结构,如果不使用PL,zynq的开发和普通的ARM 开发一样。不同的是ARM PS是可配置,因而硬件信息是不固定的。这也是zynq灵活性的一个表现。电子发烧友网编辑现为读者整合《玩转赛灵思Zedboard开发板》系列文章, 其中包括在ZedBoard开发板上的一些应用实例。其内容包括:

玩转赛灵思Zedboard开发板(1):ZedBoard详解

玩转赛灵思Zedboard开发板(2):ZedBoard最简单的测试工程

玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯

本文为玩转赛灵思Zedboard开发板(4):如何使用自带外设IP让ARM PS访问FPGA?,内容精彩,敬请对电子发烧友网保持密切关注。本文的目的是使用XPS为ARM PS 处理系统添加额外的IP。从IP Catalog 标签添加GPIO,并与ZedBoard板子上的8个LED灯相连。当系统建立完后,产生bitstream,并对外设进行测试。本文给出流水灯实现过程 的详细步骤截图。更多赛灵思(Xilinx)Zedboard基础知识、相关手册以及应用实例将陆续推出,以飨读者,敬请期待。【本文的完整工程文件下载:见本文最后。】

硬件平台:Digilent ZedBoard;开发环境:Windows XP 32 bit;软件: XPS 14.2 +SDK 14.2。

一、硬件配置

1、创建硬件工程

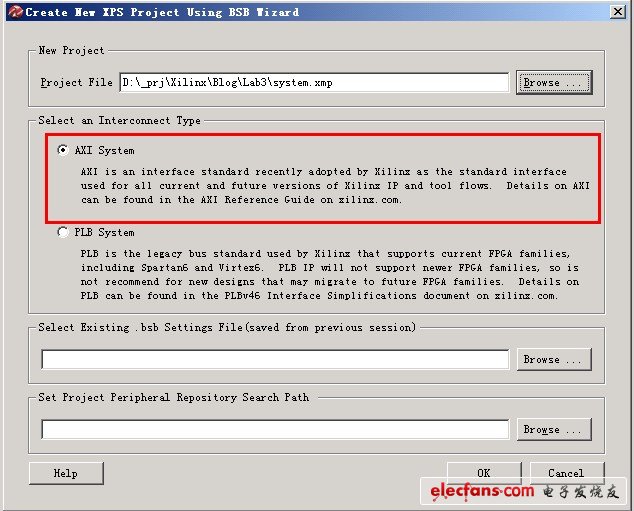

启动XPS,创建Lab3工程。因为PS系统和FPGA连接是采用AXI接口,因而选择内部互联类型(Interconnect Type) 为AXI。

选择设计平台为Zynq ZC702

到外设配置界面,系统会默认有GPIO_SW 和 LEDs_4bits 这两个外设,我们不需要,remove之

2、添加AXI GPIO外设

工程建立后,在IP Catalog中,找到General Purpose IO,找到 AXI GPIO,双击添加到系统中。

修改元件实例化名称为axi_LDs,这个名称就是将要实例化连接到PS的元件。将长度改为8,其他默认。

点开Bus Interfaces标签,可以看到系统汇总现在有PS(这里是processing_systems7_0) 、添加的外设axi_LDs 和AXI内部互联总线axi_interconnet_1。可以看到对于 axi_interconnet_1来说,PS是AXI主设备,外设是AXI从设备。

在Port标签,将IO_IF中的GPIO_IO_O(output)设置为External Ports,将Port名称改为LD。LD就是顶层对外的引脚名称

3、设定引脚约束

在project标签中,找到system.ucf约束文件,

将其内容改为

4、点击Generate BitStream,生成bitstream

如果没有错题,控制台会提示信息如下,表明成功生成了FPGA的配置bitstream文件

5、将硬件配置导入到SDK,启动SDK。这里需要将bitstream和BMM文件同时包括到SDK中。

二、创建软件程序

为了方便项目管理,在SDK目录下建立sw文件夹,作为workspace

使用新建工程向导。注意,这里使用工程模板为Memory Tests。个人经验是使用Hello World会出现XMD错误,原因不明白,可能是工程的配置不同。

新建工程后,会有几个存储空间测试的文件,我们不需要,删掉。

修改main文件,内容如下

在下载软件程序前,需要将bitstream文件烧如FPGA,对FPGA进行配置。在工具栏中Xilinx tools->Program FPGA,也可以使用XPS中的Device Configuration->Download Bitstream等其他配置FPGA的方式。

配置完FPGA后,下载软件程序,可以看到超级终端显示调试信息:

同时,Zedboard上的8个LED亮起

注意:

如果run或者debug软件程序提示

ERROR : Unexpected error while launching program. java.lang.RuntimeException: ERROR: Elf Verify failed at Address: 0x0060d77b

at com.xilinx.sdk.targetmanager.internal.TM.verifyELF(Unknown Source)

at com.xilinx.sdk.debug.core.internal.AppRunner.run(Unknown Source)

则很有可能是因为工程建立的问题,建议使用Memory Tests模板,然后再加以修改

完整工程下载:【自学ZedBoard:使用IP通过ARM PS访问FPGA(源代码) 】

-

一步一步学ZedBoard Zynq(三):使用自带外设IP让ARM PS访问FPGA2017-02-10 4064

-

zynq使用自带外设IP让ARM PS访问FPGA(八)2017-02-09 2632

-

FPGA是用altera多还是赛灵思的多呢2016-01-09 16232

-

玩转赛灵思Zedboard开发板(6):如何在Zedboard上运行linux下的应用程序?2013-01-24 27580

-

自学ZedBoard:使用IP通过ARM PS访问FPGA(源代码)2012-12-16 1469

-

玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯2012-12-05 22819

-

玩转赛灵思Zedboard开发板(1):ZedBoard详解2012-11-26 62830

-

玩转FPGA 赛灵思(xilinx)FPGA设计大赛圆满结束2012-09-06 6754

-

提交FPGA设计方案,赢取赛灵思FPGA开发板2012-07-06 10421

-

玩转FPGA,赛灵思FPGA设计大赛开赛啦2012-04-23 24006

-

赛灵思和DMP演示配备图形IP的FPGA开发板2011-10-20 3270

全部0条评论

快来发表一下你的评论吧 !