Altera或为其FPGA产品采用全耗尽型SOI技术?

PLD技术

描述

电子发烧友网讯【翻译/Triquinne】:伦敦消息,Altera一位高级工程师对全耗尽型SOI(FDSOI)芯片制造过程进行评估,并得出以下结论:对FPGA而言,该技术(全耗尽型SOI技术)有着特殊的用处。这无形中增加了未来Altera考虑换掉台积电(TSMC)代工厂或采取增加代工厂策略的可能性。

在旧金山举行的国际电子设备大会举行的全耗尽型SOI研讨会上,Altera资深技术研究员Jeff Watt提出在FPGA中采用14nm全耗尽技术。

据报道,Altera由于2013年的滑坡,所以一直忙于跟TSMC合作开发20nm平面式CMOS节点,但是却也很担心该节点是否会出现功耗很高(power hungry)的问题。

格勒诺布尔研究所实验室、SOI晶片生产商Soitec和 IBM已经和意法半导体(ST)合理开发FDSOI进程【详见:意法半导体(ST)与Soitec携手CMP提供28纳米FD-SOI CMOS制程】。此外,ST也成为了Globalfoundries公司的新客户,进而提升其生产能力。一直以来,台积电在FDSOI方面并不出色,但是也指出将计划在2014年的下一代技术中迅速向16nm FinFET制造工艺转变。

Jeff Watt在演讲中对 28nm Bulk平面CMOS工艺和14nm FDSOI平面CMOS进行了对比。这预示着Jeff Watt已经接受了这个惯例:28nm之后的下一代FDSOI节点有可能是14nm FDSOI工艺。

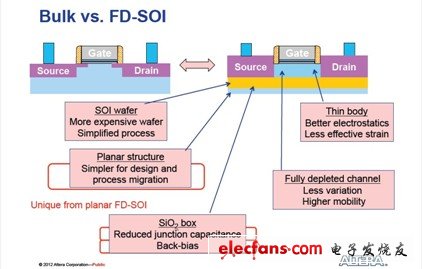

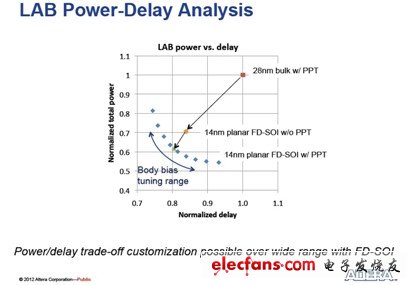

图 Bulk CMOS工艺和FDSOI CMOS工艺对比图

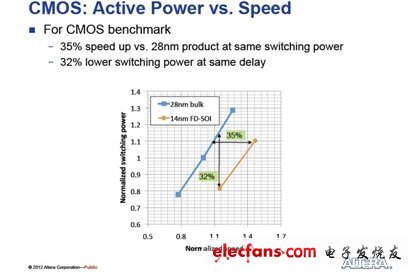

Jeff Watt说,相比28nm Bulk平面CMOS工艺而言,14nm FDSOI在同样的切换功率下性能可以提高35%,在相同的延迟时间下切换功率要低32%。

图 Bulk CMOS工艺和FDSOI CMOS动态功率及速度对比

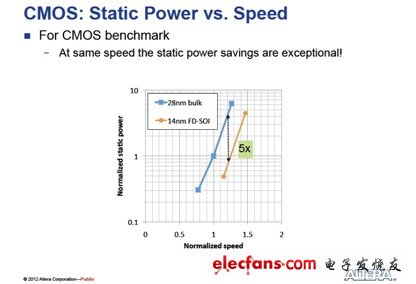

图 Bulk CMOS工艺和FDSOI CMOS静态功率及速度对比

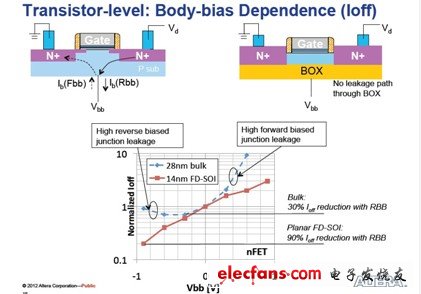

此外,Jeff Watt还演示了该工艺吸引FPGA制造商的几点,如Body-bias Dependence、广泛的定制化服务等。

图 晶体管结构层次:Body-bias Dependence对比展示

图 两种工艺的LAB功率-延迟分析

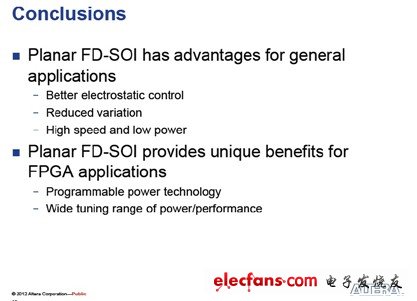

最后,Jeff Watt总结道,平面FDSOI对于一般的IC来说可能作用平平,但是对FPGA而言却具有很特殊的优势。在一般IC中,平面FDSOI应用的优势在于更好的静电控制、减少变异、高速、低功率。而在FPGA中,其优势却更为特殊:具有可编程动力技术、广泛的调谐范围功率和性能。

图 Jeff Watt得出的结论

由于2012年TSMC客户遇到的28nm Bulk CMOS工艺供应问题,Altera对此兴趣或许会大减。有人就会推测,Altera有可能会找Intel做其代工厂,因为Intel能提供尖端FinFET制造工艺技术。如果Altera选择在其FPGA上采用FDSOI技术,那这种技术很有可能由Globalfoundries提供,毕竟ST在克罗尔市的晶圆制造厂仅有试产能力。

据报道,TSMC方面保证能在Altera和其竞争对手Xilinx使用下一代FPGA中(使用20nm Bulk平面CMOS工艺)获得一大笔订单。据称Altera是第一家委托TSMC生产 20nm 平面块状硅工艺的公司,但预计在2013年将有所下降。另外,Altera和Xilinx应该都对使用TSMC CoWoS工艺的多芯片封装感兴趣,但是TSMC还未开始批量生产20nm。

然而,对Altera而言双代工厂或多代工厂制造策略是有一定困难的。早期,对代工厂忠诚在于工艺技术,有时候,对FPGA供应商亦然。或许这时候有人就会担心TSMC是否会给其100%忠实客户提供更好的支持和客户服务了。

——电子发烧友网翻译,转载请注明出处!

-

物联网应用带动FD-SOI制程快速增长2016-11-17 1344

-

Altera进一步扩展 Agilex™ FPGA 产品组合,全面提升开发体验2025-10-13 1495

-

国内外进展及SOI产业化进程2011-07-06 3247

-

FD-SOI(全耗尽型绝缘层上硅)2016-04-15 7048

-

采用SOI-CMOS技术的UV传感器IC2018-10-25 2114

-

基于FD-SOI的FPGA芯片有哪些技术优势及应用?2021-06-26 2808

-

Altera新Cyclone IV FPGA拓展了Cyclo2009-11-04 1670

-

Altera Stratix IV FPGA助推XDI db2009-12-04 1099

-

Altera发布28nm FPGA技术创新2010-02-04 962

-

Altera和Eutecus发布基于FPGA的视频分析解决方案2011-10-19 1447

-

三星预计今年将采用其28nm FD-SOI制程出样20余款芯片2018-05-02 5464

-

莱迪思即将发布首款SOI的FPGA产品2020-02-12 1336

-

部分耗尽SOI器件新体接触技术可有效克服MOSFET中的浮体效应2020-08-05 6473

-

Altera FPGA CPLD学习笔记2021-09-18 1670

-

Altera Agilex 3 FPGA和SoC产品介绍2025-06-03 1750

全部0条评论

快来发表一下你的评论吧 !