基于MC8051 IP核和FPGA的频率计设计

FPGA/ASIC技术

描述

频率是电信号中重要的物理量,在电子、通信系统中,信号的频率稳定度决定了整个系统的性能,准确测量信号的频率是系统设计的重要内容。

单片机广泛地应用于电子系统设计,其性价比高,大量的外围接口电路,使基于单片机的电子系统设计方便,周期缩短。然而,单片机的串行工作特点决定了它的低速性和程序跑飞,另外还存在抗干扰能力不强等缺点。EDA(Electronic Design Automation)技术以计算机为工具,在Quartus II软件平台上,对以硬件描述语言Verilog HDL/VHDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、综合及优化、逻辑仿真,直至对特定目标芯片的适配、编译、逻辑映射和编程下载等工作,FPGA是纯硬件结构,具有较强的抗干扰能力。

文中在FPGA芯片中嵌入MC8051 IP Core,作为控制核心,利用Verilog HDL语言进行编程,设计了以MC8051 IPCore为核心的控制模块、计数模块、锁存模块和LCD显示模块等模块电路,采用等精度测量法,实现了频率的自动测量,测量范围为0.1 Hz~50 MHz,测量误差小于0.01%。

1 8051 IP(Intelligent Property)软核

8051单片机是以由VQM原码(Verilog Quartus Mapping File)表达的,在QuartusII环境下能与VHDL、Verilog HDL等其他硬件描述语言混合编译综合,并在单片FPGA中实现全部硬件系统。

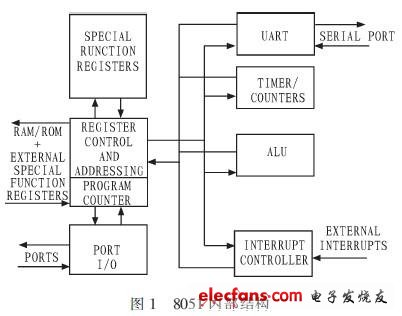

MC8051单片机核含有8位复杂指令CPU,存储器采用哈佛结构,其结构框图如图1所示。

MC8051的指令系统与8051/2、8031/2等完全兼容,硬件部分也基本相同,例如可接64KB外部存储器,可接256字节内部数据RAM,含两个16位定时/计数器,全双工串口,含节省功耗工作模式,中断响应结构等。不同之处主要有:

1)MC8051是以网表文件的方式存在的,只有通过编译综合,并载入FPGA中才以硬件的方式工作,而普通8051总是以硬件方式存在的;

2)MC8051无内部ROM和RAM,所有程序ROM和内部RAM都必须外接。

3)以软核方式存在能进行硬件修改和编辑;能对其进行仿真和嵌入式逻辑分析仪实现实时时序测试;能根据设计者的意愿将CPU、RAM、ROM、硬件功能模块和接口模块等实现于同一片FPGA中(即SOC)。

4)与普通8051不同,MC8051的4个I/O口是分开的。

更多内容请浏览:【基于FPGA的多功能频率计的设计与实现 】

- 相关推荐

- 热点推荐

- FPGA

- eda

- vhdl

- QUARTUS II

- Verilog HDL

-

MC8051 IP指令使用资源表2021-03-28 700

-

如何将外部SPI Flash加载到FPGA内部ram然后复位MC80512019-06-11 1308

-

MC8051 IP核在Altera FPGA上的移植与使用2019-05-24 3134

-

【小梅哥FPGA进阶教程】第十章 MC8051软核在FPGA上的使用 上2017-02-17 10841

-

基于8051的Proteus仿真-数码管显示的频率计2016-09-01 811

-

MC8051_IP核简单指令的仿真步骤2016-05-06 722

-

【超详细】MC8051 IP核在Altera FPGA上的移植与使用,基于芯航线FPGA核心板,小梅哥编写2016-03-11 38771

-

FPGA MC8051移植 100M频率计设计详细步骤2015-11-05 988

-

基于FPGA和8051单片机IP核的多功能频率计的设计与实现2013-01-07 7096

-

基于FPGA的多功能频率计的设计2012-11-09 1257

-

MC8051 IP核基本结构及原理2012-05-22 7797

-

基于MC8051软核的星载智能1394终端2010-08-06 984

-

mc8051 design代码,MC8051 IP core2009-05-14 741

全部0条评论

快来发表一下你的评论吧 !