Altera携手ARM公布SoC FPGA战略细节,意图赶超赛灵思?

PLD技术

描述

早在2012年12月13日,Altera联合ARM召开发布会,共同宣布发售其首款28nm FPGA SoC器件(包含双核ARM Cortex-A9 800MHz处理器)。而此时,赛灵思的类似产品Zynq已经发售一年有余。

客观来说,Altera的SoC产品进展比赛灵思缓慢许多。2010年,赛灵思就放出了与ARM合作开发下一代SoC器件的消息,而与之对应的Altera只是公布了与MIPS的合作蓝图,又联合Intel宣布X86与FPGA的融合技术,直到2011年年中,Altera与ARM的合作计划才姗姗来迟。

实际上,Altera已经意识到产品问世时间落后于赛灵思,为了弥补这一时间缺口,Altera于2011年10月发布了SoC虚拟目标软件设计工具,支持客户在获得硬件之前便能够开始开发其应用软件。据Altera官方称:“很多Altera客户已经采用了SoC虚拟目标工具,他们现在可以将其应用软件导入到SoC FPGA中,节省了数月的开发时间。”

正因为此,Altera的SoC产品才不至于被对手远远甩掉。不过现在,Altera的SoC FPGA已经发售,如何继续追赶并超越赛灵思呢?

在Altera宣布正式发售其首款28 nm SoC器件之前,公司国际市场部总监李俭曾拜访过一位国内工业控制的客户进行前期调研,他们正在用市场上已售的FPGA SoC芯片做开发,不过李俭听到了让他又悲又喜的反馈,悲的是该客户现有的芯片已经很不错了,独特的架构非常适合于他们,因此Altera的产品也类似的话,他们就不会再考虑更换供应商,但同时,该客户表示尽管已售产品性能优越,但开发过程却十分痛苦,这个观点让李俭非常兴奋,因为他知道只有这样,他们即将推出的产品才有可能获得市场的认可。

Altera国际市场部总监李俭

软硬件协同的重要性

该客户称,系统的开发调试会花费60%至70%的时间,对于FPGA SoC来说,尽管硬件和软件高度自由化,但如何将二者无缝衔接,是件非常困难的事情。“每次硬件的变化,都必须手工去和CPU做升级,只要犯一点错误整个系统就会崩溃,除非我们能做到自适应的调整。”该客户称。

李俭分析道:“传统的ARM芯片里面的接口、硬件加速器、内存映射、比特定义等都是固定的,只有CPU具有高度灵活性。但到了FPGA中,什么都是变化的,也就注定了CPU不可能用固定的方式与之适应,所以利用FPGA开发出的硬件可能会与软件与CPU冲突。这就造成了客户的困扰。”

与李俭同去的Altera产品总监表示,Altera的新工具与设计流程,可以解决软硬件协同的难题,客户当场就表示,如果真有你这种东西,我一定会选择你们。“为什么客户愿意放弃一年多的努力而选用我们的平台?这就要求我们必须能给客户一个完全不一样的东西,给客户一个真正适合SoC开发的调试工具。”

不一样的调试工具

Altera的SoC开发调试工具有什么不同呢?

在一年多以前,Altera与ARM合作时,就开始开发基于FPGA的DS-5可视化开发工具,现在,业界首款FPGA自适应嵌入式软件工具包已经上市,有了该工具,像上述的工控客户,就可以不必遭受软硬件协同调试带来的痛苦。

李俭介绍道,此前调试ARM只能用专用的DSTREAM,而FPGA也需要专门的调试工具,Altera的新方案则是基于其USB Blaster,一个工具可以同时调试FPGA与ARM,“这样做真正去除了CPU和FPGA直接的调试壁垒,由于我们和ARM之前有特殊的OEM协议,因此才有了这种创新的产品。”

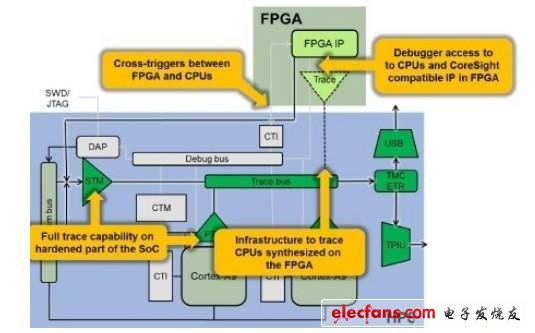

李俭解释道,Altera在产品设计过程中使用了ARM CoreSight的一些规范,使FPGA可以和DS-5之间进行信息的交互与处理,支持FPGA信号事件、软件时间以及CPU指令跟踪相关联。而使用CoreSight之后,不光是ARM CPU,其他与CoreSight兼容的IP核都可以使用DS-5进行调试。

同时,该工具提供了交叉功能,CPU和FPGA之间都可以设置触发,从而实现跨域的硬件软件协同调试。

FPGA的自适应与统一调试方框图

2013年初,995美元的Altera SoC嵌入式设计套装会供货,而2013年4月,1495美元的Altera Cyclone V SoC则会推向市场。

尽管在SoC硬件开发上落后于赛灵思,但Altera同时也可以看到客户面临的挑战与困惑,从软件开发入手,换种方式参与到市场的竞争中,也完全可以在市场中占有一席之地。Altera公司产品和企业市场副总裁Vince Hu评论称:“现在,确定使用Altera SoC 的客 户数量已经超出了我们的预期。”

此外,在硬件方面,Altera也有了相当多的升级,包括32位ECC内存保护、128bit内部总线,灵活的启动型以及内置存储器的双重保护功能等。

在未来规划方面,李俭表示Altera 20nm制程时将会采用性能更好的1.5GHz双核ARM,此前,赛灵思曾透露其20nm制程时将会采用下一代ARM架构,但具体方案尚未公布。

ARM+FPGA的未来?

鉴于此次事件标志着ARM在FPGA领域的重要突破,ARM中国区销售总监刘润国亲临发布会现场,而此前赛灵思的发布会也邀请到了ARM中国区总裁吴雄昂。ARM参与这两次重要的发布会,足以证明其对于FPGA所代表的高端领域的期望,毕竟相对于传统SoC,FPGA产品更高端化,而通过与FPGA厂商的合作,标志着ARM进入了全新的市场。刘润国表示:“FPGA内部集成硬核并不是件新鲜事,此前的PowerPC是最典型的代表,而今ARM能够走进FPGA,证明ARM不光是在功耗上领先于竞争对手,我们在更高端的产品领域同样可以表现的非常出色。”

ARM中国销售总监刘润国

谈到越来越多的FPGA厂商携手ARM进军嵌入式SoC市场,刘润国认为根本的原因来自市场的交叉需求,一方面是Altera等FPGA市场面对的客户的需求,另外一方面则是来自以ARM为代表的SoC市场的需求。

尽管FPGA SoC的好处不言而喻,但李俭同时表示,未来FPGA SoC还会面临一些挑战,“这主要来自两方面,第一点是客户使用习惯的问题,毕竟没有FPGA开发经验的人上手会很困难,但我们通过开发诸如基于FPGA的DS-5等软件,可以让客户更容易的进行FPGA开发工作。第二点则是切换成本的问题,只有那些把眼光放在长处的企业,才会有可能考虑通过长期效应来覆盖短期切换平台成本的损失。”李俭说道。

-

如何使用赛灵思FPGA加速包处理?2021-04-30 1795

-

揭秘赛灵思计算平台ACAP技术细节2021-01-04 4514

-

为什么说赛灵思已经远远领先于Altera?2019-09-02 5592

-

Arm携手赛灵思助力嵌入式开发人员获取成熟的Arm IP2018-10-11 3757

-

赛灵思首度官方回应Altera收购:5 年内将用户群数量提升 5 倍!2017-02-09 328

-

FPGA是用altera多还是赛灵思的多呢2016-01-09 16226

-

携手TSMC 赛灵思稳猛打制程牌2013-10-22 1654

-

“赛灵思”抢楼活动第二轮,中奖楼层公布!2013-10-11 42250

-

反击Altera 赛灵思2014量产16纳米FPGA2013-05-31 1538

-

玩转FPGA 赛灵思(xilinx)FPGA设计大赛获奖名单!!!2012-09-06 11955

-

赛灵思Verilog(FPGACPLD)设计小技巧2012-08-19 2548

-

在赛灵思FPGA中使用ARM及AMBA总线2012-03-01 6978

-

ARM与赛灵思合作,再次进军FPGA2009-11-06 638

全部0条评论

快来发表一下你的评论吧 !