用于SOC或块级时钟的可配置分频器

接口/时钟/PLL

描述

时钟是SOC或块级设计最重要的组成部分之一,在设计概念构思/规划阶段中,需要很好地定义和理解时钟的架构。单个SOC拥有各类模块,如内核、闪存、存储器和外设,这些模块需要在不同频率下运行。它们的最大运行速率可能受到所使用的实现技术、实施架构、功率目标、以及IP访问时间等因素的限制。时钟分频器电路是必不可少的,它可以从主锁相环(PLL)/振荡器时钟,或任何系统时钟中产生分频时钟,并将不同的分频时钟馈送到不同的器件模块。由于时钟也可以被应用驱动,时钟分频器必须是可配置的。需要可配置性的原因有很多,包括:

* 以较低的频率运行系统时钟,从而减少动态功耗。

* 以高于或低于处理器的频率运行外设的状态机。

* 设置发送/接收外设帧的波特率。

本文阐述了目前SOC中各种可配置时钟分频器逻辑的实施方案,强调了各自的问题、优势及局限性。可配置分频有各种实施方案,但是数字化设计行业中最简单且最经常使用的实施方案包括:

* 纹波分频器

* 具有50%占空比的基于Div解码的2N倍分频器

* 不具有50%占空比的基于时钟门控使能技术的整数分频器

* 具有整数分频和50%占空比的基于多路选择器的分频器。

纹波分频器

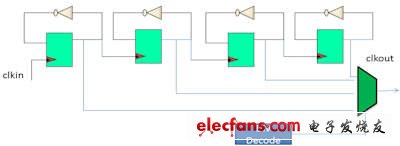

图1:可配置纹波分频器的电路示意图。

纹波分频器是传统的分频器,由于它们在安装和保持时间上有严格的要求,目前的SoC设计中通常避免使用这种分频器。

优势:

* RTL复杂性最小

* 生成的分频时钟占空比为50%。

局限性:

* 时钟时延随着更高版本分频时钟的应用而增加(时钟上升沿的延迟大小排列为DIV16》 DIV8》 DIV4》 DIV2》 DIV1。)

如果启动时钟和捕获时钟从带不同分频因子的不同分频器产生,这个缺陷可能导致更大的路径不一致。

例如,设想一个带两个纹波分频器的简单时钟架构(见下图),其中一个用于为内核提供时钟,另一个用于为闪存提供时钟。两个时钟之间的比例必须是4:1。这会导致设计本身有意想不到的偏差。

图2:可配置时钟示例。

闪存时延–平台时延= 2个触发器的CK-Q延迟

* 即使有时钟树平衡,也要确保强大的时序签收功能,这对于设计进入投产阶段非常重要。STA工程师需要在四个不同触发器的输出上定义时钟,因为每个触发器都在生成具有不同时延的时钟。这增加了人工工作,需要在设计中人工定义并检查所有可能生成的时钟。

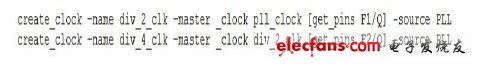

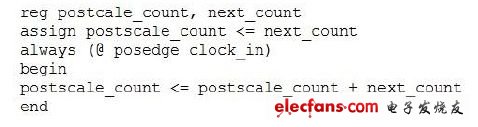

基本RTL如下所示:

图3:Div解码分频器实施。

在需要分频的输入时钟的每个上升沿上都更新一次postscale_count寄存器的值。分频时钟可以从postscale_count寄存器的MSB中产生。下一个计数寄存器的值取决于分频因子。

优势:

* 这类分频器拥有最简单的RTL。

* 它们产生的输出时钟占空比为50%,且不会像纹波分频器一样导致固有偏移,因为分频时钟总产生于一个点。

局限性:

* 这类分频器仅限于2N倍分频。

基于时钟门控使能的整数分频器或穿通分频器

图4显示了一个简单的穿通时钟分频器实施过程。

图4:基于时钟门控的分频器。

图5显示了3分频时钟生成的波形图。

M bit m=log2N(max): M bit m=log2N(max)

图5:3分频时钟生成的波形图。

一旦存储(N-1)寄存器值达到零,倒数计数器将被初始化。电路中的锁存器确保“NOR”门输出产生的使能只有在时钟为低时被传播到AND门。如果没有锁存器,输出时钟可能产生故障。

优势:

* 对于基于时钟门控的分频器,RTL是相当简单的,另外,穿通时钟方案显著减少了高速时钟DFT复杂性。

局限性:

* 某些IP,如DDR,要求占空比为50%,这对于穿通时钟是不可能实现的。

* 从时钟上升沿开始到时钟下降沿结束的时序路径必须在1/2的时钟频率处相遇,也就是说,STA团队必须在时钟架构确定前,检查设计中这些关键时序路径。

基于多路选择器的分频器

基于多路选择器的分频器的实现如下所示,随附进行三分频时的波形样本。基于多路选择器的分频器让时钟流经2:1多路选择器的选择引脚。多路选择器数据引脚的使能值随着输入时钟切换,使得多路选择器输出产生的逻辑正是所需的时钟输出。这类实施需要一个重要的条件。在多路选择器的数据输入端,需要添加额外的时钟门控检查,确保时钟分频器电路正常工作。下面的波形中显示了时序检查。

图6:基于多路选择器的分频器。

以下波形在对输入时钟进行三分频时生成。

图7:3分频波形。

图8:时序检查。

时序检查1是从时钟上升沿到时钟下降沿的半周期设置检查,因此如果输入时钟被锁定在极高的频率,这项检查将至关重要(例如为最大程度地减少抖动,将锁相环输出锁定在极高的频率。)

RTL复杂性低,通常由设计人员选择是否采用50%占空比的时钟分频器。

优势:

* 50%占空比的整数分频和不具有50%占空比的分数分频

* 所有生成的时钟采用单源引脚(多路选择器输出)。

局限性:

* 需要部署额外的时钟门控检查,时序变得至关重要。

可配置的基于多路选择器的分频器作为分数时钟分频器使用

可配置的分数时钟分频器或FCD是基于多路选择器的分频器中一个重要类别。分数时钟分频器的重要特征包括:

* 这些分频器是异步分频器,分频器的时钟输出与设计中生成的其他时钟异步。

* 这些分频器不具有50%的占空比。

* 输出时钟的最大频率(fmax)(f /分频系数)四舍五入到.5或0

* 输出时钟的最小频率(fmin)(f/分频系数)四舍五入到.5或0

所需的输出频率实际上是许多输入时钟周期中输出时钟的平均频率。

FCD的概念

举一个分数时钟分频的例子,就可以理解FCD的概念。

假设时钟分频为1.3 - 这样时钟的最小频率fmin= 1.5,最大频率fmax= 1

也就是说:输出时钟的10个周期=输入时钟的13个周期

设最小频率的输出时钟周期数为X

设最大频率的输出时钟周期数为Y

因此

x + y = 10

1.5 x + Y = 13

由此我们解出

x = 6 y =4

这样,6×1.5=9个输入时钟周期,将除以1.5, 4个输入时钟周期将除以1。 1.3分频的波形图如下所示。这些分频器常常用于逐级时钟频率切换,防止在瞬间出现高电流消耗(这可能导致晶体管的Vdd口出现异常电压下降或上升,破坏设计,并可能引起芯片复位)。时钟频率的步长随着设计中每单位时间允许的最大频率增加或减少。

图9:分数时钟分频。

本文结论

本文向人们展示了目前大多数设计中都使用的基本可配置时钟分频器。尽管实施方案可能会有所不同,但是可配置分频器的基本思路是一致的。由于每种时钟分频器各有优点和局限性,设计人员在选择时钟分频器类型时需要格外注意。虽然穿通时钟方案使DFT时钟更加简单,其占空比局限性给时序团队在分频时钟域关闭关键的半周期路径时留下了繁琐的工作。基于多路选择器的分频器提供50%占空比的输出时钟,但可能使DFT时钟变得复杂。因此,如果在设计早期,从功能,DFT和时序方面详细了解和分析时钟的关键性因素,避免时钟架构变化,可能会在之后的时序收敛阶段带来意想不到的惊喜。

-

qiangua1314

2013-03-25

0 回复 举报不错,学习哦 收起回复

qiangua1314

2013-03-25

0 回复 举报不错,学习哦 收起回复

-

FPGA学习-分频器设计2023-11-03 3656

-

NB7V33MMNGEVB 时钟分频器参考设计2020-12-31 1248

-

用于高速ADC的时钟分频器演示板DC1075A演示板2019-02-21 1901

-

HMC905LP3E分频器2018-10-17 1541

-

可配置技术影响SoC(系统级芯片)的设计2018-02-08 1884

-

分频器的定义及电子、功率分频器的比较2017-11-24 19261

-

用于SOC或块级时钟的可配置分频器2012-12-11 3407

-

什么是分频器 分频器介绍2010-02-05 5288

-

供数字时钟使用的+5000分频器电路2009-01-13 2401

全部0条评论

快来发表一下你的评论吧 !