ADI实验室电路:灵活的中频至基带接收机解决方案

无线/传感

描述

电路功能与优势

该电路是灵活的频率捷变中频至基带接收机。中频和基带 上的可变增益用于调整信号电平。 ADRF6510 基带ADC驱动器还包括可编程低通滤波器,可消除通道外阻塞和噪 声。

此滤波器的带宽可随着输入信号带宽变化而动态地调节。 这样可以确保由本电路驱动的ADC的可用动态范围得到充 分使用。

电路内核是IQ解调器。 ADL5387 基于2×LO的相位分离架构 支持宽频率范围工作。精确的正交平衡和低输出直流失调 确保了对误差矢量幅度(EVM)的影响极小。

本电路内所有元件间的接口均采用全差分式。如果不同级间需要直流耦合,相邻级的偏置电平彼此兼容。

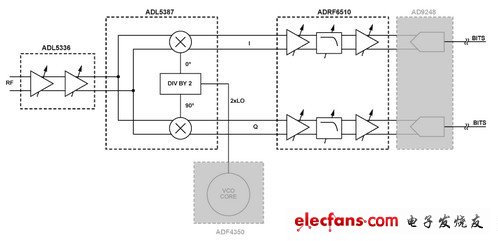

图1. 直接变频接收机原理示意图(所有连接和去耦均未显示)

电路描述

接收机架构

本电路笔记中描述了接收机的直接变频(也称为零差或零中频)架构。与可以执行多次频率转换的超外差式接收机相比,直接变频无线电只能执行一次频率转换。一次频率转换的优势如下:

降低接收机复杂性,减少所需级数;提高性能和降低功耗

避免镜像抑制问题和不需要的混频产物;只需要基带上的一个LPF

高灵敏度(相邻通道抑制比[ACRR])

图1显示了该系统的基本原理示意图,包括集成自动增益控制(AGC)环路的级联中频可变增益放大器(VGA),以及紧随其后的正交解调器、具有可变基带增益的可编程低通 滤波器。图1中以灰色显示的元件( ADF4350 和 AD9248) 是为清楚起见,并不包括在系统级测量中(有关这些器件的详情请参见“常见变化”部分)。

理想情况下,第一级的输入和最后级的输出应设置系统的 动态范围(信噪比)。实际上,情况可能并非如此。在正交 解调器之前放置级联VGA不仅会给系统带来更多增益,而 且有利于整体系统噪声性能,只要VGA的噪声系数低于正 交解调器,只要VGA仍具有增益,且未发生衰减。后续级 的噪声系数通过初始VGA的增益进行分频处理。提供VGA (相对于仅提供固定增益放大器)的另一优点是AGC环路可 经设计以调平正交解调器的输入信号。这一限制施加于正 交解调器和任何后续级的信号电平的能力非常重要。

中频VGA和AGC环路

中频VGA和AGC环路功能可通过 ADL5336来实现。它具有 两个可级联VGA,每个VGA具有24 dB的模拟动态范围,并 且可以通过SPI端口以数字方式改变每个VGA上的最大增 益。

为了实现信号调平AGC功能,每个 ADL5336 VGA具有平方 律检波器,通过可编程衰减器连接到输出。检波器将衰减 器的输出与63 mV rms的内部基准电压进行比较。如果衰减 器输出与63 mV rms基准电压间有差异,误差电流便会产生 并集成到CAGC电容内。AGC环路通过将DTO1/DTO2引脚连 接到GAIN1/GAIN2引脚关闭。为了使AGC环路正常工作, 将MODE引脚拉至低电平,从而产生负VGA增益斜率。

每个 ADL5336 VGA具有允许的输入功率范围,AGC将在此 范围内调平至特定设定点。在该范围以外,VGA输出随输 入一起按dB递增或递减(假定VGA未处于压缩状态或信号 不在噪底内)。

IQ解调器

信号从 ADL5336 路由至 ADL5387,在此接受解调并将频率 转换为零中频。 ADF4350频率合成器可向 ADL5387提供所 需的2×LO信号(参见“常见变化”部分);但实际测试使用信 号发生器代替 ADF4350 。

ADL5387 使用两个双平衡混频器,一个用于I通道,一个用 于Q通道。提供给混频器的LO使用2分频正交分相器生 成。这为I和Q通道提供了0°和90°信号。 ADL5387在RF输入 至基带I和Q输出之间提供约4.5 dB的转换增益。

低通滤波器、基带VGA和ADC驱动器

低通滤波、基带增益和ADC驱动器功能全部使用 ADRF6510来实现。施加于 ADRF6510的信号现在具有独立 的I和Q路径,信号首先通过前置放大器放大,然后进行低 通滤波,以抑制任何不需要的带外信号和/或噪声,最后通 过VGA放大。

ADRF6510 的每个通道可分为三个级:

前置放大器

可编程低通滤波器

VGA和输出驱动器

通过GNSW引脚,前置放大器具有6dB或12dB的用户可选增益。低通滤波器可通过SPI端口设置为1MHz至30MHz的转折频率,步进为1MHz。VGA具有50dB增益范围,增益斜率为30mV/dB。VGA增益通过GAIN引脚控制,GNSW引脚被拉低时范围可为0.5dB至+45dB,GNSW引脚被拉高时范围可为+1dB至+51dB。输出驱动器能够将1.5Vpp差分电压驱动至1k负载内,同时保持高于60dBc的HD2和HD3。

可施加于低通滤波器同时仍在 ADRF6510内保持可接受的HD电平的最大CW信号为2Vpp。如果存在较大带外干扰源且可能造成 ADL5387 和/或ADRF6510的输入过载,带外干扰源(及所需的带内信号)可通过 ADL5336VGA予以衰减。 一旦带外干扰源被ADRF6510的低通滤波器抑制,所需信号可使用XAMPVGA(紧随 ADRF6510的滤波器)放大。

ADRF6510发出的IQ信号可施加于适当的模数转换器(ADC),例如AD9248。

测量结果

4-QAM、5 MSPS调制信号被施加于ADL5336的输入。有关测试设置的更多信息,请参见“电路评估和测试”部分。

EVM衡量数字发射机或接收机的性能质量,反映幅度和相位误差所导致的实际星座点与理想位置的偏差。如图2所示。

图2. EVM图

图3显示了系统EVM与ADL5336输入功率的关系,VGA上的最大增益针对VGA1和VGA2分别设置为15.2dB和19.5dB。

测试了数个AGC设定点组合。图4也是系统EVM与ADL5336输入功率的关系;不过VGA的增益分别设置为9.7dB和13.4dB。测试了相同的AGC设定点组合。

图3. 系统EVM,数字VGA增益=11

图4. 系统EVM,数字VGA增益=00

图3和图4说明,施加于 ADRF6510 的信号电平必须保持足 够低以免压缩输入级和/或滤波器。在最高AGC设定点 (500mVrms和707mVrms), ADL5387IQ解调器的输入开始压缩并给EVM造成额外下降。当AGC设定点位于最低点 (88mVrms)时,可实现最佳EVM。当设定点为250mVrms 时,EVM已经开始下降。

图5比较了 ADL5336VGA上的最小和最大数字增益设置(VGA 均设置为增益代码11或增益代码00)间的EVM,此时VGA1 和VGA2设定点分别为250 mVrms和88 mVrms。

图5. 系统EVM,VGA1设定点=250MVRMS,VGA2设定点=88MVRMS

对于给定AGC设定点,当最大增益代码为11时,从VGA2 至VGA1的切换在VGA2超出增益范围后发生;因此,施加 于 ADRF6510 的信号电平继续增加(同时EVM下降),直至 VGA1到达设定点。一旦VGA1到达设定点,EVM再次变 平;因此施加于 ADRF6510 的信号电平在大约5 dBm的输入 功率下不会变化,除非VGA1超出增益范围。当最大增益 代码设置为00时,VGA均可提供更多衰减,因此允许VGA2偏移动态范围,以免在输入功率低至与最大增益代 码为11时相同的情况下到达设定点。这样VGA2可在较高 输入功率下保持在设定点,使VGA2至VGA1的切换可发生 在VGA2超出增益范围之前。这样就能确保施加于 ADRF6510的信号电平保持在恒定值,直至到达输入功率 范围最高点。

图6比较了 ADL5336 VGA上的最小和最大数字增益设置(VGA 均设置为增益代码11或增益代码00)间的EVM;不过VGA1 和VGA2设定点分别为707mVrms和88mVrms。

图6. 系统EVM,VGA1设定点=707MVRMS,VGA2设定点=88MVRMS

图6中的动态特性与图5相同,只不过更为夸张。当最大增 益代码为00时,VGA2在约-40dBm的输入功率下到达设定点。其保持设定点至约-10dBm,此时VGA1尚未到达707mVrms的设定点。除非输入功率约为0dBm,并且EVM开始略微变平,否则VGA1不会到达设定点。当最大增益设置为11时,相同情况再次发生;不过,VGA2仅保持设定点至大约-20dBm,因为再无更多增益可用于获得规定的设定点。

常见变化

系统和频率合成器

为 ADL5387提供2XLO的信号发生器可被宽带频率合成器取 代,例如 ADF4350,该器件集成了VCO。 ADF4350 属于一个频率合成器系列,该系列具有135MHz至4350MHz的宽 频率范围,且具有变化的相位噪声和输出功率指标,因此很容易找到符合应用所需规格的器件。

系统和ADC

为系统添加ADC以对 ADRF6510的I和Q信号进行采样正是完善模拟信号链自然演化的结果。双通道ADC,例如 AD9248,提供14位分辨率,且采用20MSPS、40MSPS或65MSPS采样速率。建议在 ADRF6510 和 AD9248 的输出之间放置抗混叠滤波器。抗混叠滤波器设计示例请参考 ADRF6510 数据手册。

ADRF6510 输出共模电压考虑因素

ADRF6510 输出共模电压可在1.5V至3.0V范围内调节,且不会损失驱动能力。许多现代ADC的输入共模电压小于1.5V。 将VOCM引脚驱动至小于1.5 V的输出共模电压使ADRF6510 的失真性能开始下降;但器件在小于1.5 V的共模电平下仍可工作。为了保持失真性能,可能需要直流电平转换电 路,或者可使用具有较低共模电压的集成式滤波器和VGA器件,例如ADRF6516。

电路评估与测试

需要/使用的设备

信号发生器包括:

Agilent E4438C vector signal generator

AgilentE4438C矢量信号发生器

基带信号捕获器件有

AgilentDSO90604A示波器

EVM运算器件包括:

Agilent89600VSA软件

运行WindowsXP的PC,通过USB电缆连接到示波器

电源包括:

±5V电源除 AD8130电路板需要±5V外,所有电路板均需要+5V

评估板包括:

ADL5336-EVALZ (需要一个)

ADL5387-EVALZ (需要一个)

ADRF6510-EVALZ (需要一个)

AD8130-EBZ (需要两个)

开始使用

要使用 ADL5336和 ADRF6510,需要评估软件来控制每个器件的各个方面。此软件可在工具、软件和仿真模型链接中的各个产品网页上找到。

下载和安装软件后,将USB电缆从电脑连接到评估板,然后针对需要控制的器件运行软件。

功能框图

图7显示了用于测试接收链的测试设置的功能框图。 ADL5336评估板仅允许单端输入和输出。 ADL5387板上的RF输入也是如此。矢量信号发生器上的RF输出端口仅为单端;因此,发生器与 ADL5336的输入之间需要巴伦。如图7 所示,直至 AD8130差动放大器的其余信号路径均为差分。 由于示波器仅允许对单端信号进行采样,同时受VSA软件控制,因此需要差分转单端转换。

设置与测试

接收机测试设置的第一步是开启所有测试设备。测试设备预热时,电路板必须正确配置以便在信号链内正常使用。

在 ADL5336上,应确保安装0w跳线电阻,将VGA1输出连接到VGA2输入。

在ADL5387电路板上,旁路输出巴伦以在ADL5387和ADRF6510之间构建完整的差分、直流耦合信号路径。

在 ADRF6510电路板上,执行下列操作:

旁路输入和输出巴伦

在输出信号线路上放置1k差分输出负载(每个输出路径上放置两个接地的500电阻就足够了)

用1μF电容取代普通COFS电容

图7. 测试直接变频接收机的功能框图

收集评估板并将所有信号路径连接在一起,如图7所示。将所有电路板连接到+5V,同时将两个 AD8130板连接到-5V。请确保电源电流与期望值一致。

如图7所示,完成下列连接:

将矢量信号发生器的单端、50输出连接到 ADL5336评估板的INPUT1。

将AD8130的I信号路径输出连接到示波器上的输入1,并将AD8130的Q信号路径输出连接到示波器的输入3。

将USB电缆从PC连接到示波器。

将信号发生器的RF端口连接到ADL5387评估板的LO输入。

在AgilentE4438C信号发生器上,执行下列操作:

将频率设置为400MHz

将幅度设置为0dBm

接通RF端口

在AgilentE4438C矢量信号发生器上,执行下列操作:

将RF载波频率设置为200MHz

接通RF端口

接通RF端口

接通矢量信号发生器内部的定制ARB

将信号设置为4-QAM,符号速率设置为5MSPS,脉冲整形滤波器值设置为0.35

在PC上,启动Agilent89600VSA软件。在VSA软件中,执行下列操作:

接通数字解调器

将输入设置为I+jQ选项

将频率设置为0Hz,符号速率设置为5MSPS,值设置为0.35

矢量信号发生器上的信号指标必须匹配VSA软件上的指标。软件启动后,应显示IQ星座图窗格和频谱窗格。在VSA软件中通过下列步骤添加信息窗口:

点击显示

点击布局

选择栅格2×2

默认情况下,已经显示的其他两个窗格应为误差矢量与时间和信息窗口:符号/误差。如果并非如此,执行下列操作

双击任意窗格的标题

在出现的窗口中选择符号/误差

符号/误差窗格提供许多结果,包括EVM。软件应锁定在信号上,并报告EVM数值。

AGC设定点、最大增益和滤波器带宽全部可采用个别器件的各控制软件来设置。ADL5336输入端的功率控制可通过矢量信号分析仪上的功率扫描完成。从−80dBm扫描至几乎+16dBm,以便在此测试设置下测试接收机。 ADRF6510上的增益始终设置为实现1.5Vp-p差分输出电平,假定有足够的增益可用。某些情况下,对于极小的信号电平,ADRF6510无足够的增益来到达1.5Vp-p差分电平。

-

AD6650分集中频至基带GSM/EDGE窄带接收机技术手册2025-04-28 760

-

CN0248 基于IQ解调器,具有中频和基带可变增益以及可编程基带滤波功能的中频至基带接收机2021-06-03 875

-

具有中频和基带可变增益以及可编程基带滤波功能的中频至基带接收机,不看肯定后悔2021-05-24 2326

-

CN0320:基于IQ解调器,具有中频和基带可变增益以及可编程基带滤波功能的中频至基带接收机2021-03-18 730

-

如何使用IQ解调器设计一个中频至基带的接收机2020-08-07 999

-

中频至基带接收机电路功能与优势2019-07-05 3324

-

基于IQ解调器的中频至基带接收机设计2019-03-13 4131

-

基于IQ解调器,具有中频和基带可变增益以及可编程基带滤波功能的中频至基带接收机2017-11-24 1273

-

实验室整体解决方案是什么?2014-08-11 2585

-

ADI实验室电路:带抗混叠滤波器的宽带接收机2012-12-14 6663

-

ADI实验室电路合集2012-09-20 38720

-

模块时代之ADI实验室电路2012-03-01 2515

全部0条评论

快来发表一下你的评论吧 !