尺寸最小的16位SAR ADC-ADI-MAX11100

描述

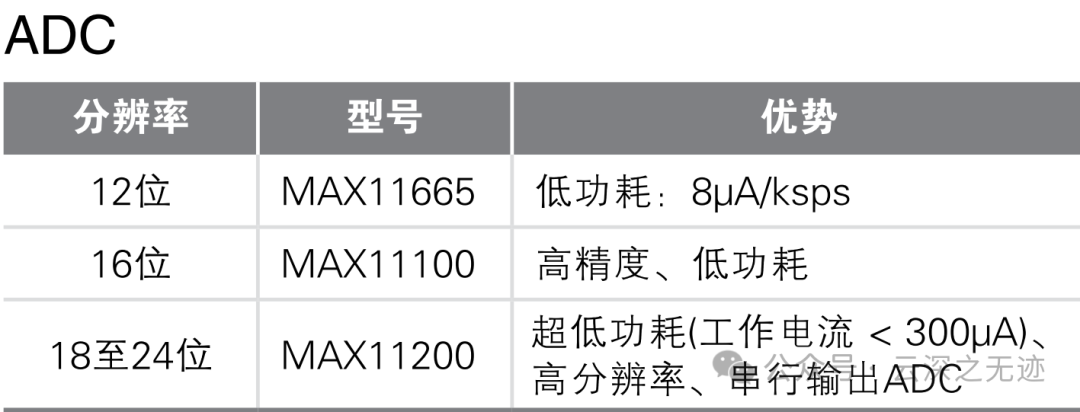

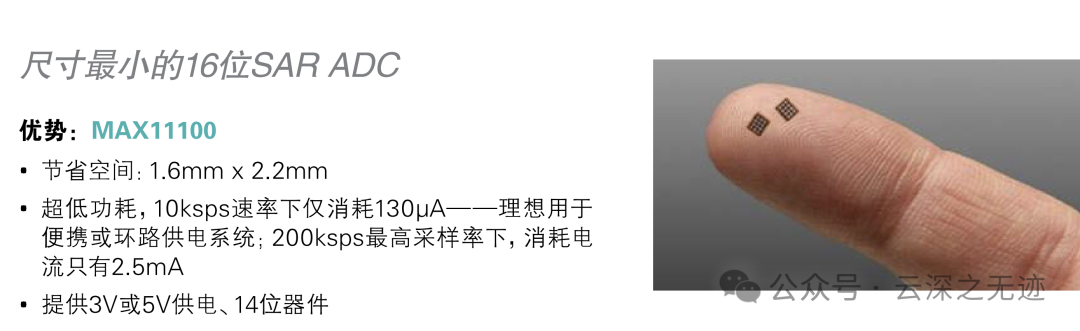

今天看了一个ADI的产品册,关于精密信号链的,发现了一个特别小的ADC。

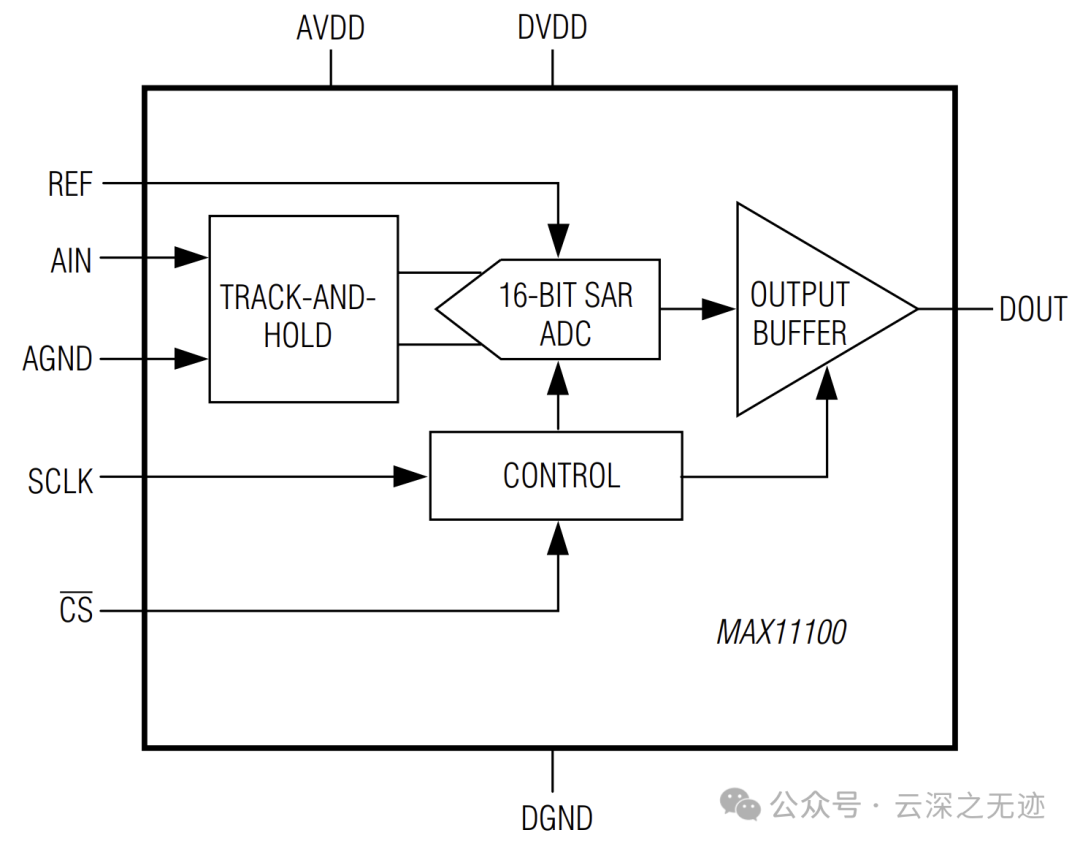

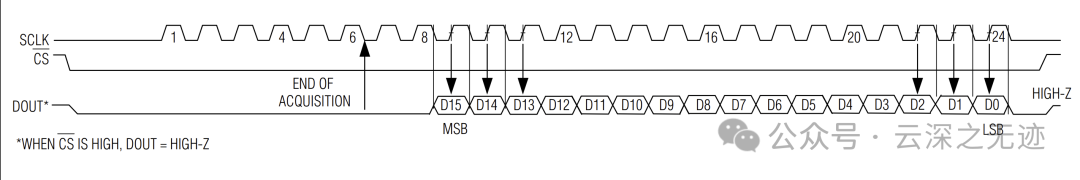

除了小以外,就是使用简单,数据手册里面就有关断和普通采集两个模式。

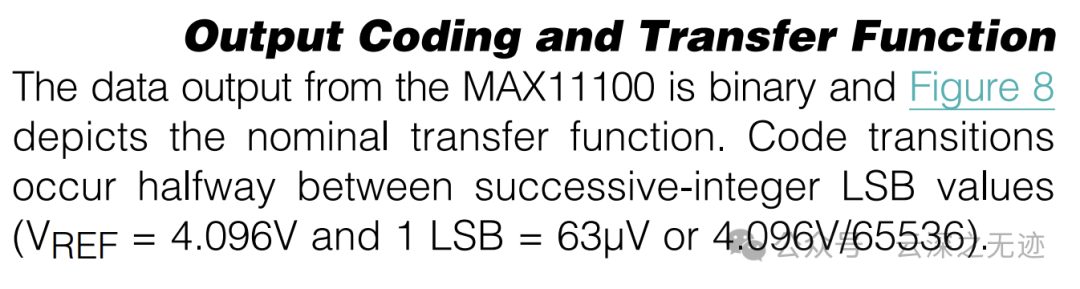

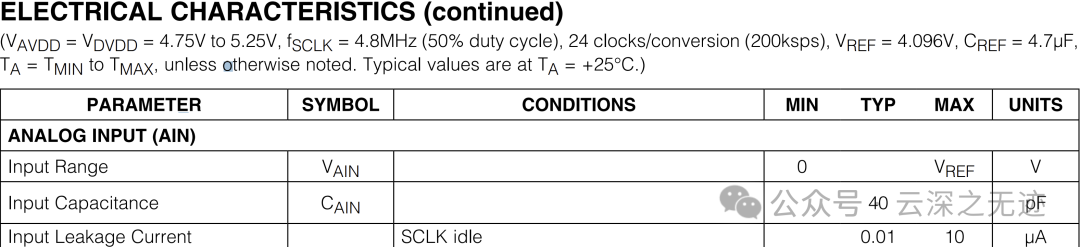

16bit,在典型的环境下可以采样63uV的信号,普通的够用

没有负电压,不支持差分功能

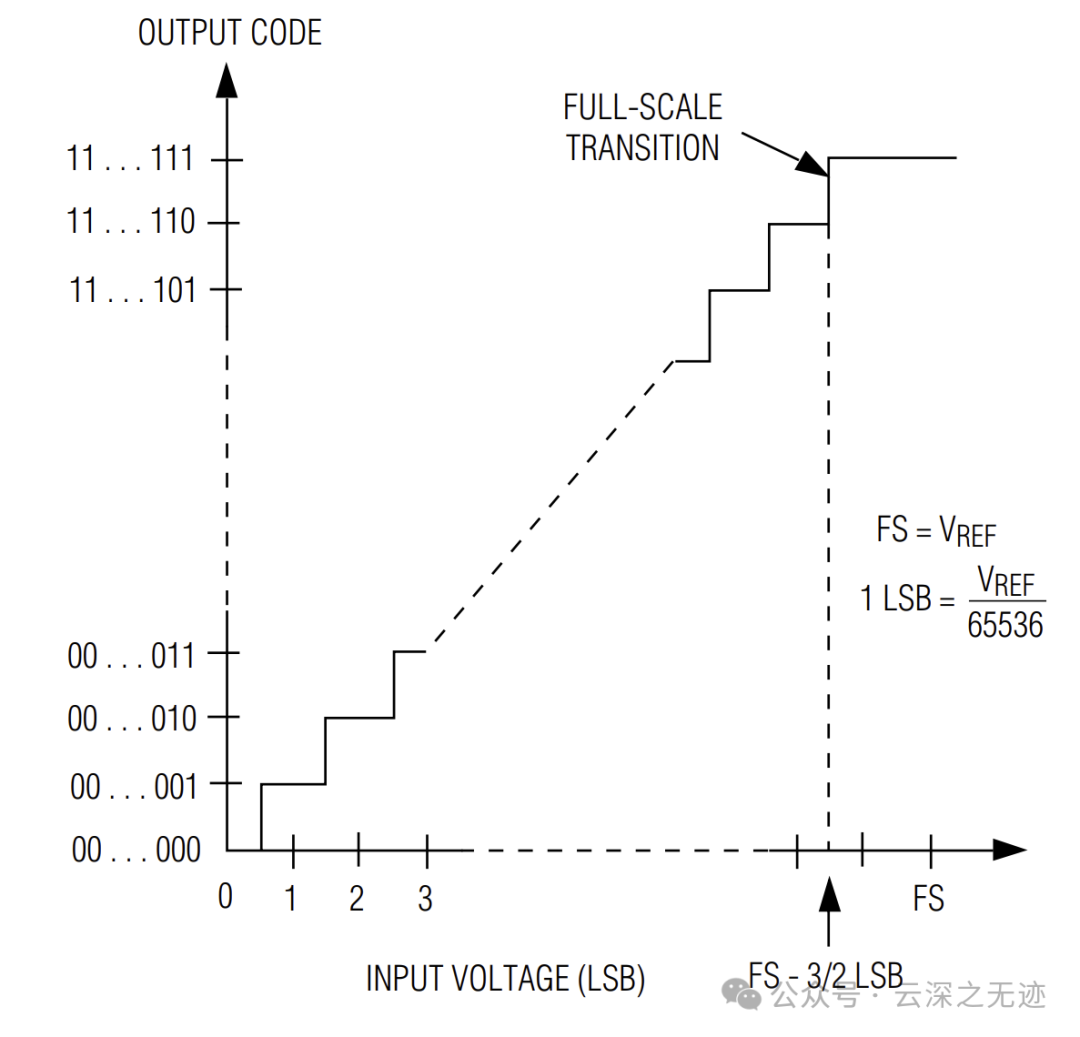

要想达到16bit的精度,还得加缓冲器,又加了多余的器件,emmm

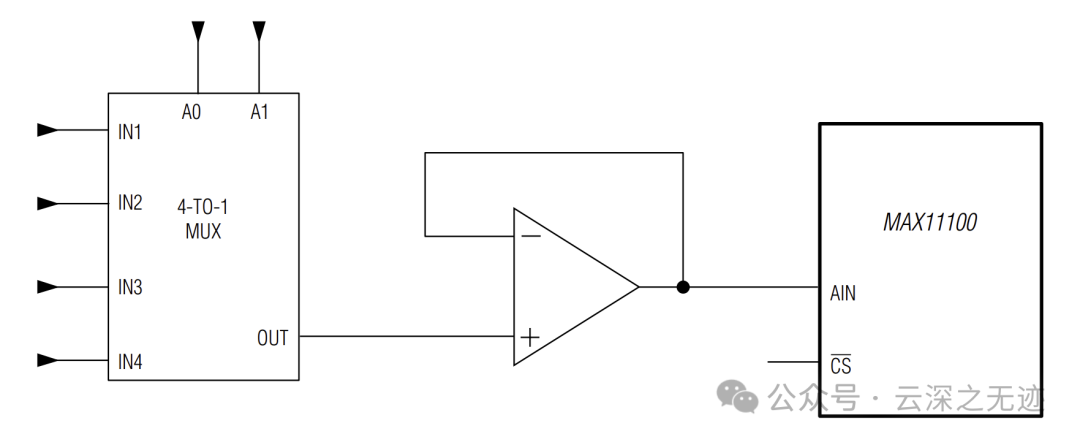

典型传感器应用涉及到传感器参数的监测和执行器的控制。传感器信号链(如下图所示)由模拟域和数字域组成。典型传感器输出的是幅度很小的模拟信号。

这些弱模拟信号使用运放、模数转换器或压频转换器进行放大和滤波,并转换为数 字值,然后在MCU中进行处理。模拟传感器输出通常需要先进 行适当的信号调理,然后再转换为数字信号。

MCU会根据信号检测条件来控制执行器和维持传感器信号调理电路的操作。在数模反馈路径中,最常用的是数模转换器(DAC)、数字电位器和脉宽调制器(PWM)等器件。

MOSFET驱动器常用作反馈电路和执行器(如电机和阀门)之间的接口。

这个图是信号链的全景,通过ADC感知现实何DAC干预现实展开

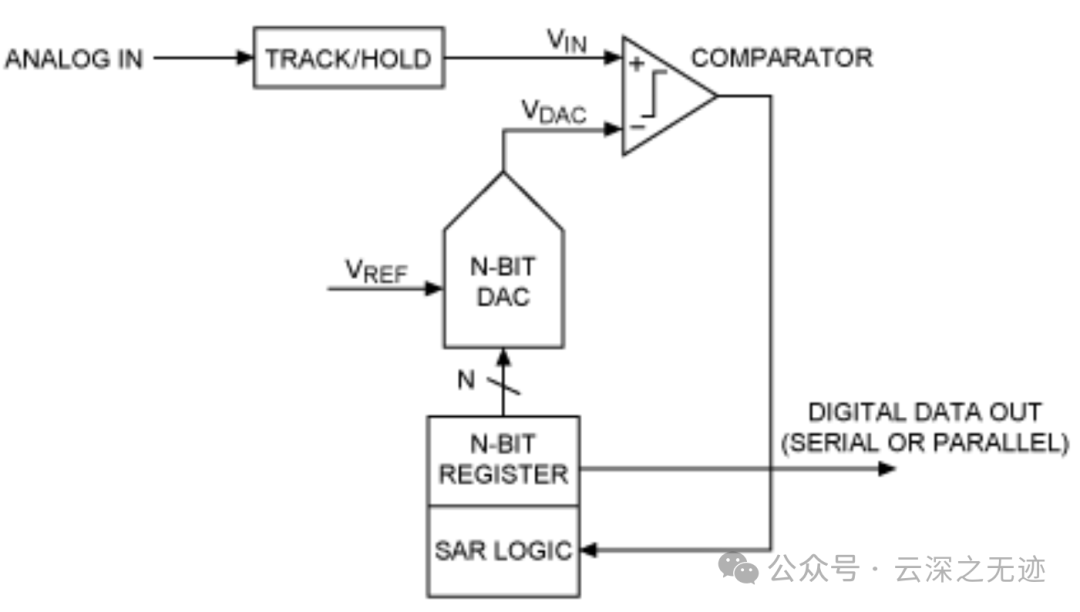

逐次逼近寄存器型(SAR)模数转换器(ADC)占据着大部分的中等至高分辨率ADC市场。SAR ADC的采样速率最高可达5Msps,分辨率为8位至18位。SAR架构允许高性能、低功耗ADC采用小尺寸封装,适合对尺寸要求严格的系统。

逐次逼近寄存器型(SAR)模拟数字转换器(ADC)是采样速率低于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构。这个话虽然和上面比差不多,但是

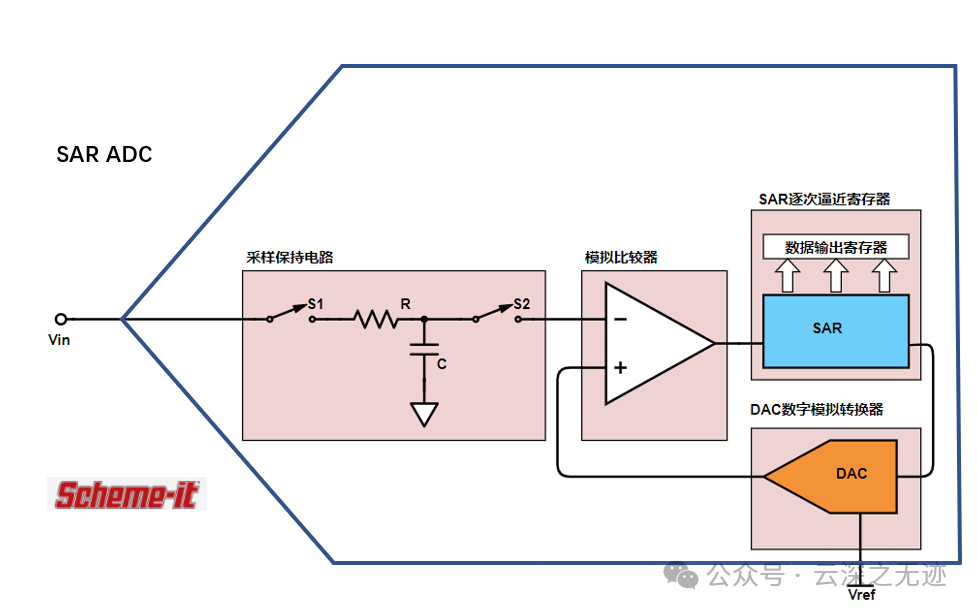

模拟输入电压(VIN)由采样/保持电路保持。

为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100... .00,MSB设置为1)。

这样,DAC输出(VDAC)被设为VREF/2,VREF是提供给ADC的基准电压。然后,比较判断VIN是小于还是大于VDAC。如果VIN大于VDAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。

相反,如果VIN小于VDAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。这个过程一直持续到LSB。上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内。

大概就是这样

放个彩图

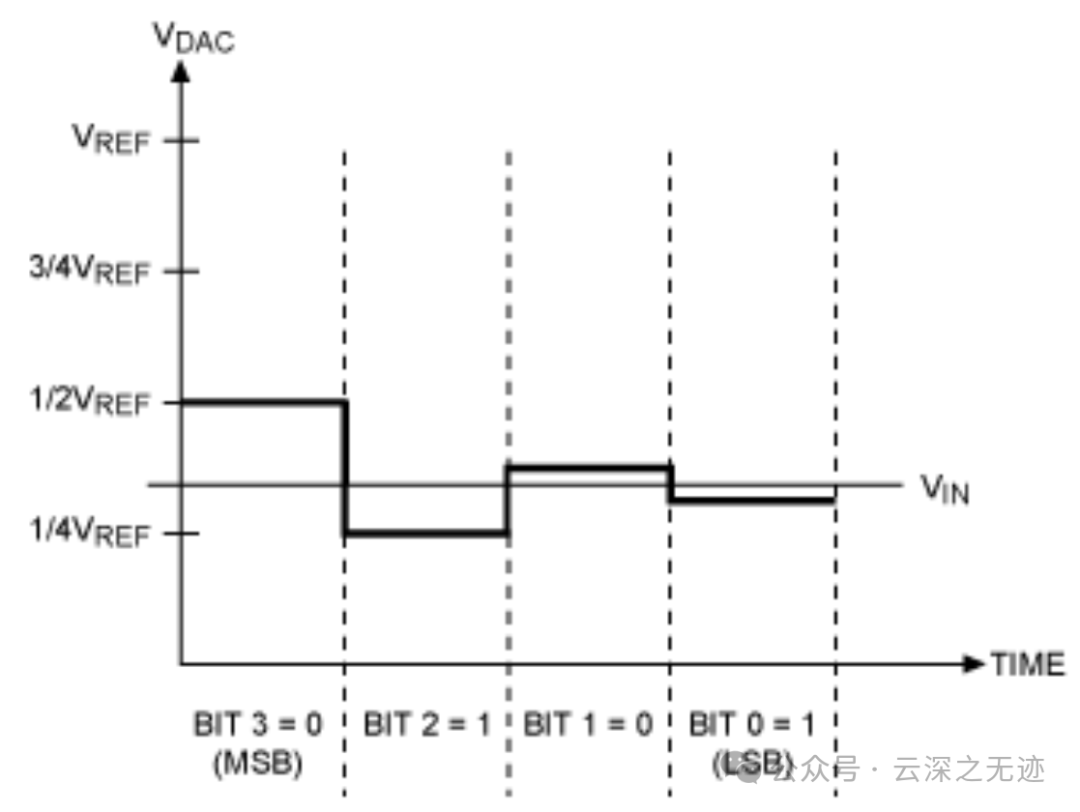

给出了一个4位转换示例,y轴(和图中的粗线)表示DAC的输出电压。

本例中,第一次比较表明VIN < VDAC。

所以,位3置为0。

然后DAC被置为01002,并执行第二次比较。

由于VIN > VDAC,位2保持为1。DAC置为01102,执行第三次比较。

根据比较结果,位1置0,DAC又设置为01012,执行最后一次比较。

最后,由于VIN > VDAC,位0确定为1。

那么这个值就会被慢慢的比较出来。

这个就是不停的比大小

对于4位ADC需要四个比较周期。

通常,N位SAR ADC需要N个比较周期,在前一位转换完成之前不得进入下一次转换。

由此可以看出,该类ADC能够有效降低功耗和空间,当然,也正是由于这个原因,分辨率在14位至16位,速率高于几Msps (每秒百万次采样)的逐次逼近ADC极其少见。

SAR ADC的另一个显著的特点是:功耗随采样速率而改变。这一点与闪速ADC或流水线ADC不同,后者在不同的采样速率下具有固定的功耗。这种可变功耗特性对于低功耗应用或者不需要连续采集数据的应用非常有利

SAR结构的主要局限是采样速率较低,并且其中的各个单元(如DAC和比较器),需要达到与整体系统相当的精度。ADI的文档给了各个单元的细节,我就不放了,那就抄的太多了。

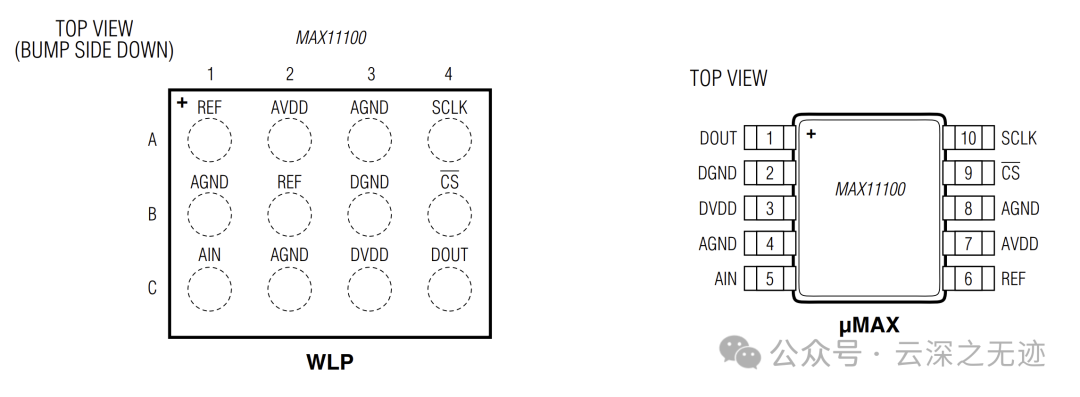

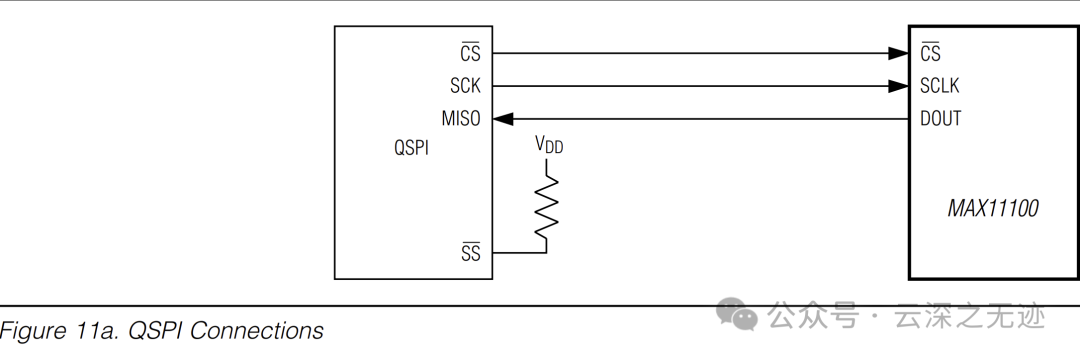

QSPI,这连接也不对啊

时序也没有上面不一样

应该这个QSPI就是快一些,没有很多的资料了,这里MCU是PIC的,感觉国外的MicroChip好流行啊!

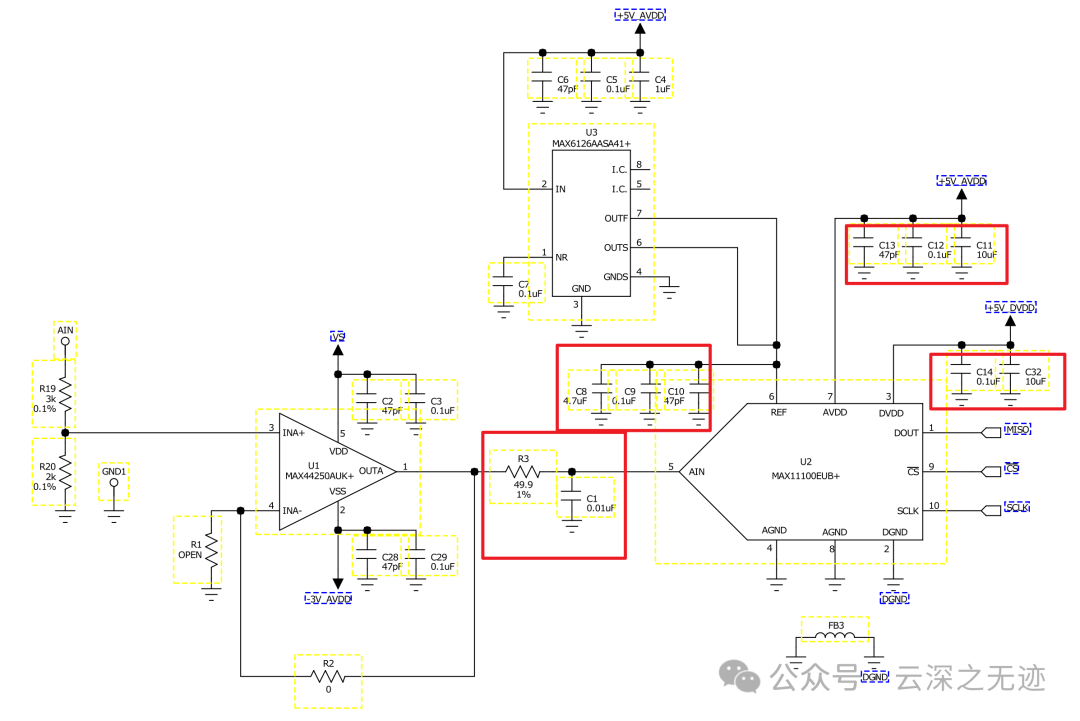

说说布线:

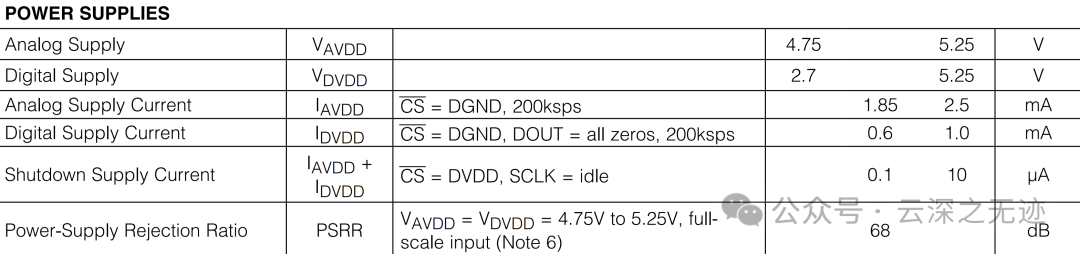

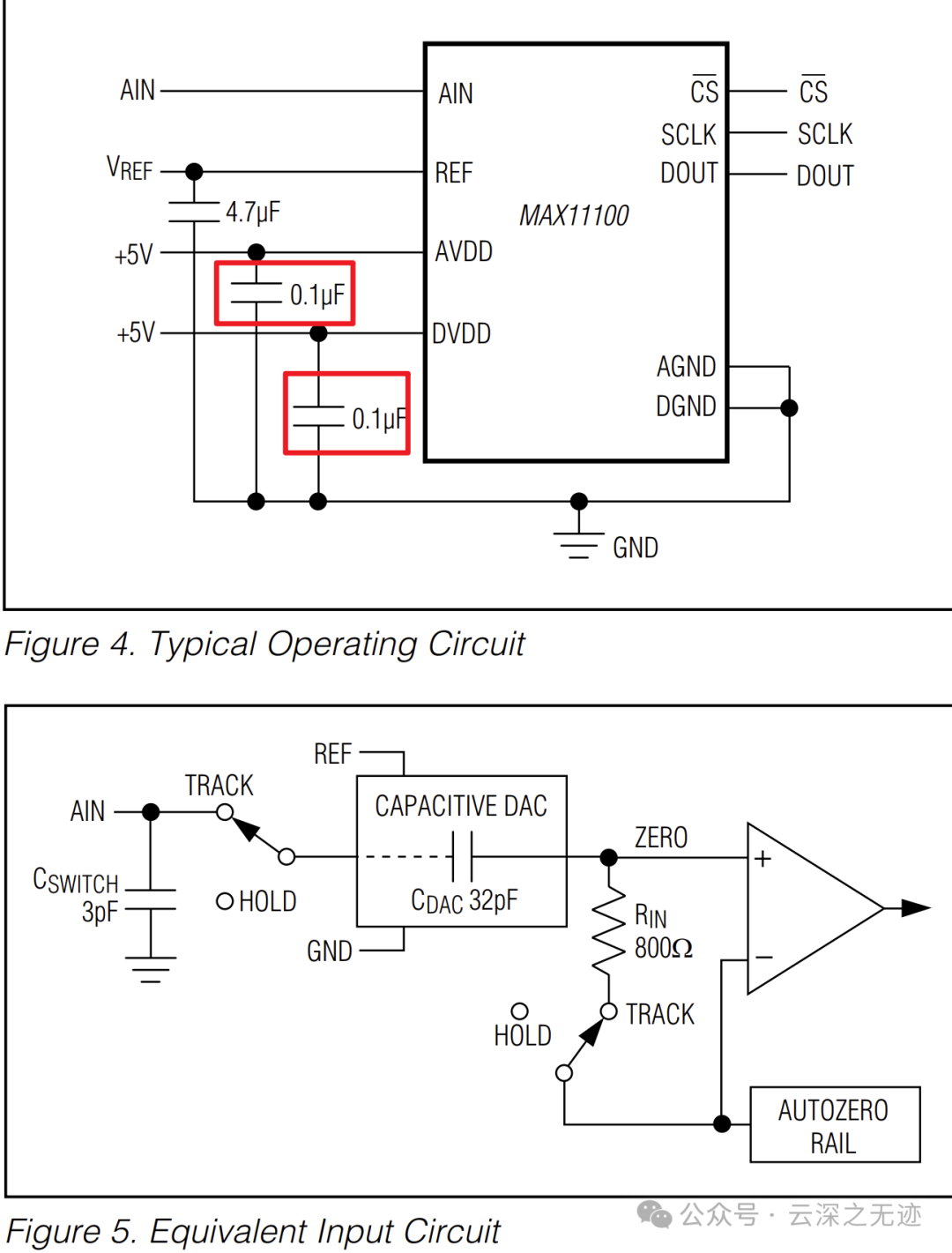

电源,布局,接地和旁路使用pcb与单独的模拟和数字接地平面。

不要使用单面板 在MAX11100上连接两个接地平面。当模拟电源和数字电源来自同一源时,用低值电阻(10Ω)或铁氧体磁头将数字电源与模拟电源隔离。

供电、输入顺序的约束如下:AGND优先于DGND。

在AVDD和AGND存在后应用AIN和REF。

DVDD与电源顺序无关。

确保数字返回电流不通过模拟地,并且返回电流路径是低阻抗的。

当5mA电流流过PCB接地走线阻抗仅为0.05Ω时,产生的误差电压约为250μV,在+4V满量程系统中产生的误差为4lsb。电路板布局应确保数字和模拟信号线保持分开。不要让模拟和数字(尤其是SCLK和DOUT)线彼此平行运行。因为在空间中会互相耦合。 如果一个必须与另一个相交,就以直角相交,指线。ADC高速比较器对AVDD电源的高频噪声敏感。用一个0.1μF的电容和一个1μF到10μF的低esr电容并联,旁路一个噪声过大的电源到模拟地平面。保持电容引线短,以获得最佳的电源噪声抑制。

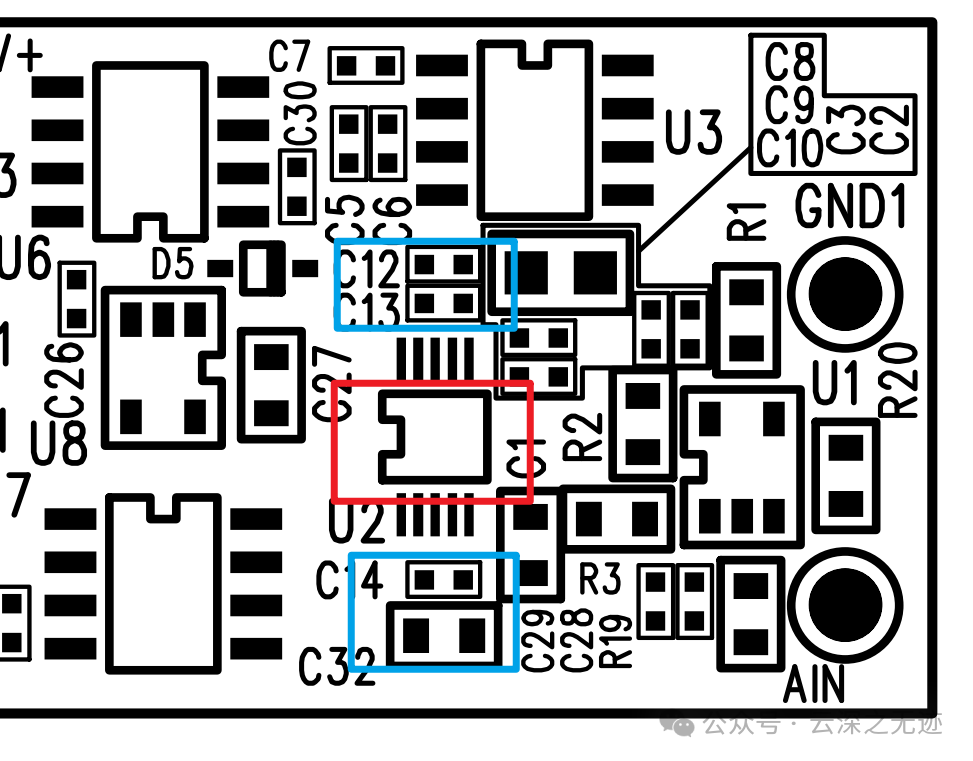

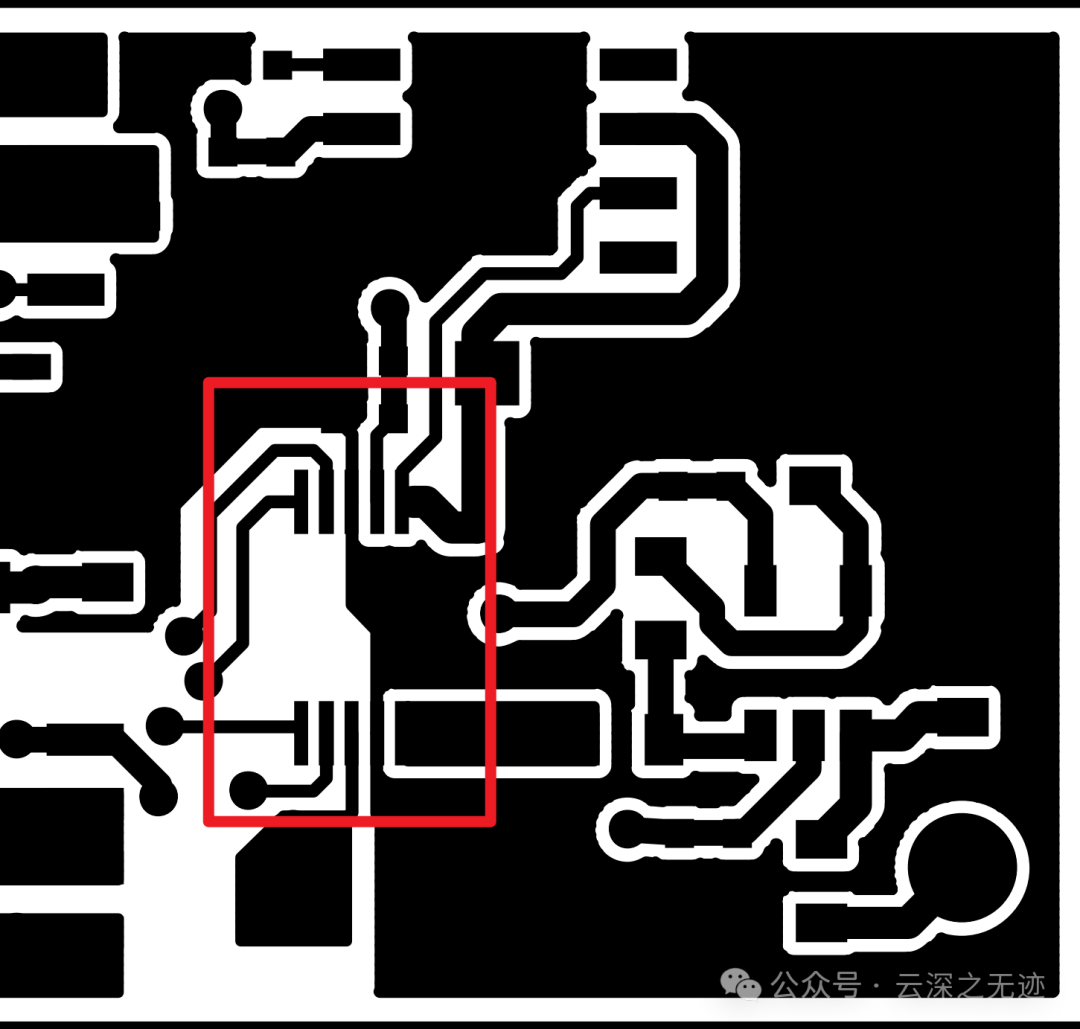

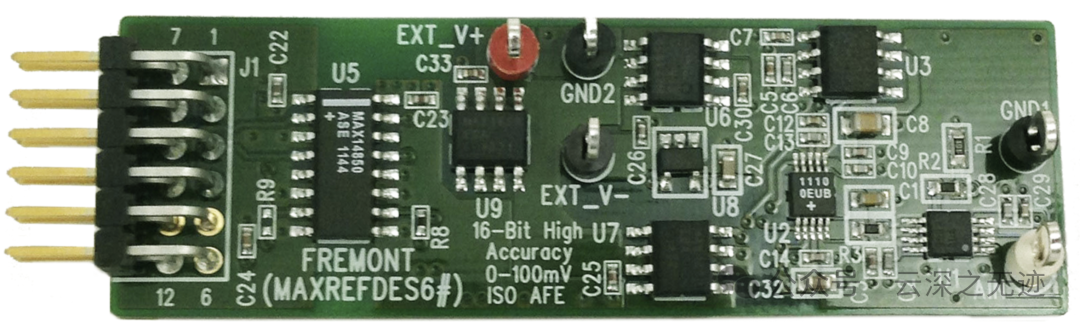

看实际是加了很多的滤波电容,输入端还有滤波器,也可以调整输入的时间。

都是大量的电容

可以看到走线走的很顺,证明布局好

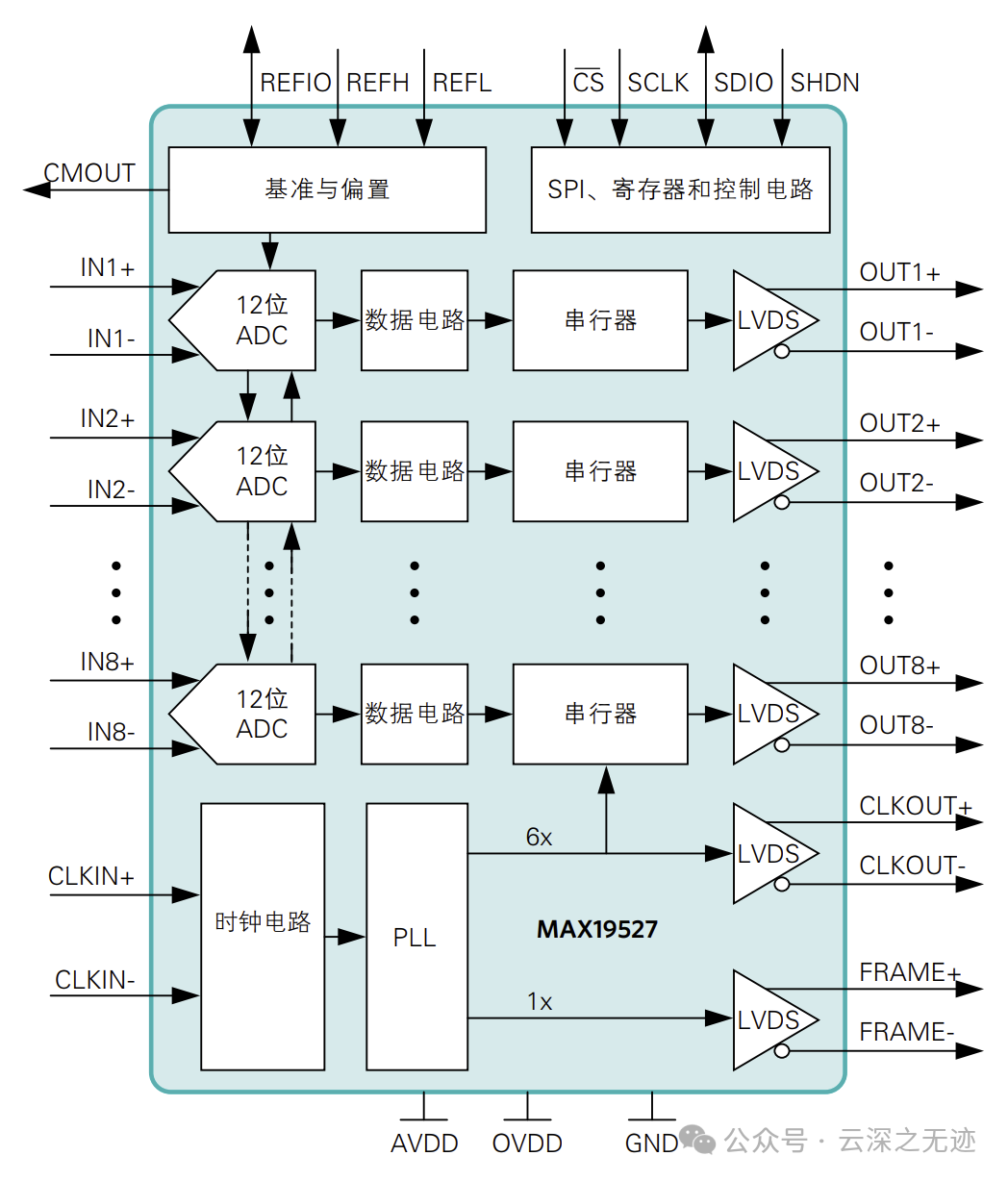

这个是一个高级的ADC,输出的是LVDS

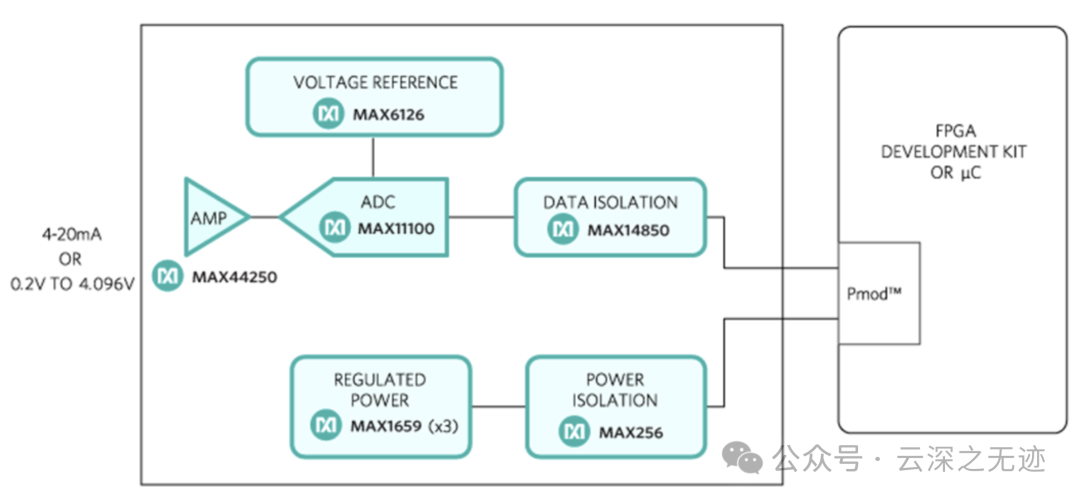

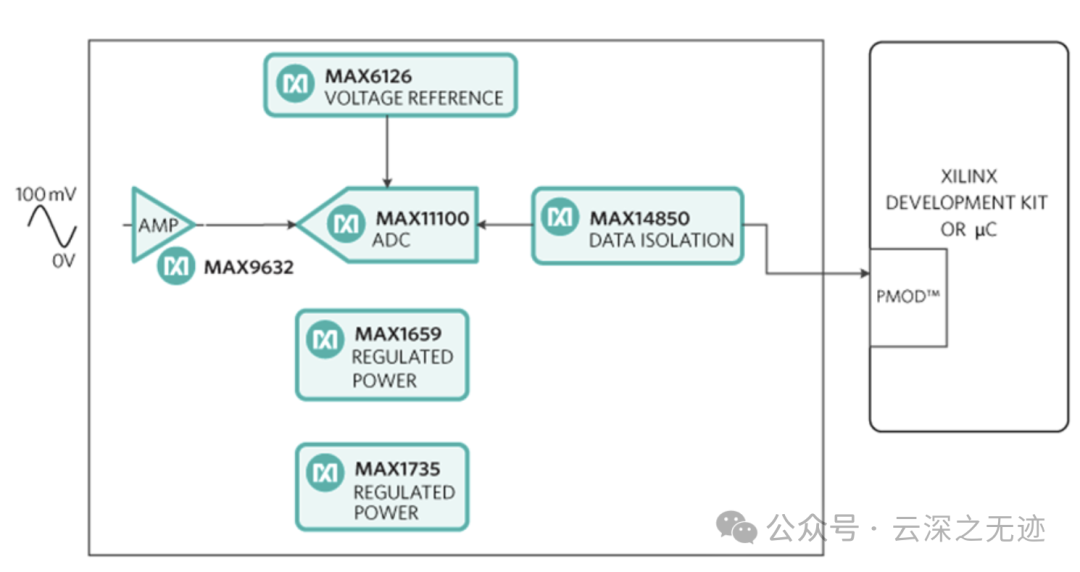

给出了三个设计:

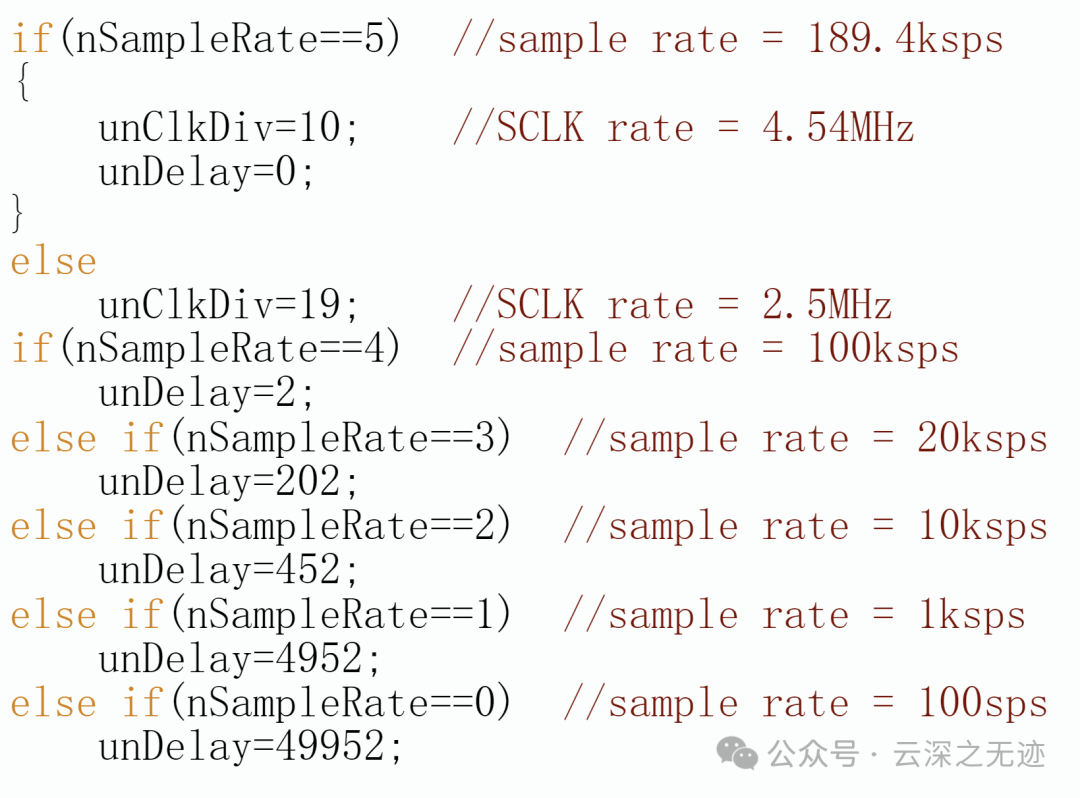

具体的看官网,给的是FPGA上面软核的C代码,很抽象。

真的很怪,有什么值得使用FPGA的

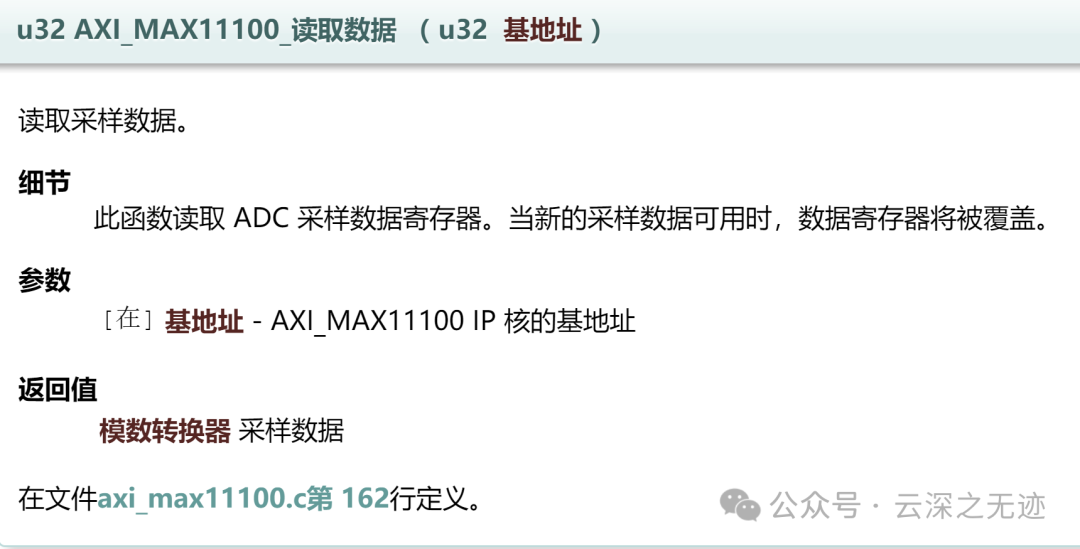

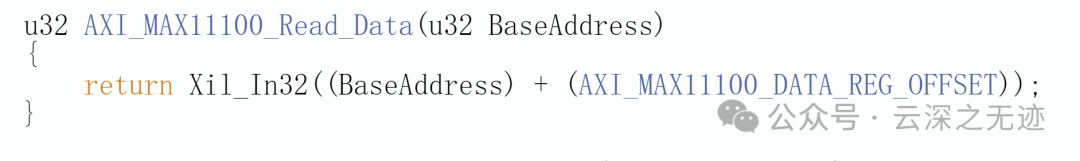

读取函数

实现,好家伙儿,直接在内存里面捞,牛逼牛逼

单次采样的C代码

总之我不理解

哪里好?我买不起是真的

审核编辑:彭菁

-

MAX11100:低功耗16位ADC的卓越之选2026-03-31 306

-

ADI推出新一代16至24位超高精度SAR ADC系列产品2022-05-05 6217

-

双16位5Msps SAR ADC2021-04-30 1032

-

16位SAR ADC MAX11168的关键特性和应用2020-10-22 1944

-

最小的ADS1115系列16位ADC处理器2018-06-12 10911

-

美信推出业内尺寸最小的18位逐次逼近型ADC MAX111562013-05-14 1989

-

Maxim推出尺寸最小双极性ADC MAX11166和MAX111672012-12-17 2213

-

MAX11166业内尺寸最小的16位ADC,支持±5V双极性性输入2012-09-13 3652

-

MAX11100 ,pdf(16-Bit, +5V, 200ksps ADC)2011-10-19 847

-

MAX11100 业内尺寸最小的16位ADC2011-10-18 1915

-

Linear推出16位SAR ADC LTC2393-162010-01-19 1369

-

Linear推出16 位 SAR ADC LTC2393-12010-01-16 1267

全部0条评论

快来发表一下你的评论吧 !